数字体系的规划师们面临着许多新的应战,例如运用选用了串行器/解串器(SERDES)技能的高速串行接口来替代传统的并行总线架构。依据SERDES的规划增加了带宽,削减了信号数量,一同带来了比如削减布线抵触、下降开关噪声、更低的功耗和封装本钱等许多优点。而SERDES技能的首要缺陷是需求十分精确、超低颤动的元件来供给用于操控高数据速率串行信号所需的参阅时钟。即便严厉操控元件布局,运用长度短的信号并遵从信号走线约束,这些接口的颤动地步仍然是十分小的。

固定频率振荡器可用于许多通用的SERDES规范;可是,这些解决方案价格贵重。此外,这种做法缺少灵敏性,并且使调试、测验和出产变得困难。

另一种解决方案是运用可编程时钟器材,如莱迪思的ispClock系列,以及一个低本钱的CMOS振荡器。ispClock器材具有超低颤动特性,一同保留了用户可编程器材所供给的灵敏性,然后满意SERDES时钟的一系列要求。本文将解说怎么更有用地运用可编程时钟器材,完成各种依据SERDES接口的参阅时钟子体系。下面将具体研讨一个XAUI的运用示例。

SERDES参阅时钟源的规划应战

无论是在一个FPGA、SoC仍是ASSP中,为任何依据SERDES的协议挑选一个参阅时钟源都是十分具有应战性的。器材本钱、经过耦合高速信号使得噪声最小化、超低颤动要求、因为信号长度匹配的要求而对走线的约束、考虑周全的电源供电规划(包含噪声的考虑、元件布局上的约束、信号布线的要求和电源去耦)以及测验/出产要求,这些都有必要考虑到并对各个要素的利害进行权衡剖析。

传统驱动SERDES参阅时钟的办法是运用一个真实的差分输出振荡器,特别挑选固定合适的频率,来完成低颤动和较小的相位噪声。该解决方案十分贵重并且不行灵敏,无法在今后的规划中再次运用。固定的解决方案,就其实质而言也约束了灵敏性,为一种接口而规划的时钟体系不能方便地在另一个新的规划中运用。相反,新的规划有必要从头开始,还或许需求运用不同的器材、不同的架构或改动电路板本来的布局布线和走线规范。备货、测验和出产也会愈加杂乱:固定频率器材需求准备多个器材以契合不同规范,然后增加了出产费用。假如器材不能更改时钟频率或不能掩盖整个时钟输出规模,那么子体系的测验和调试会愈加困难。

固定频率、低颤动差分振荡器选用的工艺一般不包含发生输出频率的内部PLL电路,因此这些器材在频域剖析中会有噪声边带和多重方式散布。一同寻觅抱负的终端和差分I/O逻辑规范并坚持安稳的电源供电也相同存在应战。依据参数规范、数量、包装和温度规模,这些振荡器本钱在12美元至50美元。

像莱迪思半导体公司的ispCLOCK 5406D这样一种新式的可编程逻辑器材,供给了灵敏、超低颤动和低本钱的解决方案来驱动SERDES参阅时钟。这些器材和低本钱的CMOS振荡器能够满意FPGA、SoC和ASSP的SERDES参阅时钟所需的严厉超低颤动要求。此外,这种增强型的运用完成坚持了器材低本钱的一同还简化了规划、测验和出产。因为这些器材是可编程的,因此能够仅经过对时钟进行不同功用的编程来完成规划重用。例如:输出能够改为不同的规范——或许是从LVDS变为LVPECL——运用不同接口替代贵重的晶振。依据ispClock的规划能够在多个未来的规划中运用,以缩短产品上市时刻、下降库存并简化出产制作。乃至能够完成现场的功用更改,完成快捷的更改、晋级并进步服务质量。因为这些时钟器材有多个带有独自相位偏移和时刻偏移的输出,因此能够“掩盖”很广的测验规模,能更好地确认元件的容限值,完成更安稳的体系。

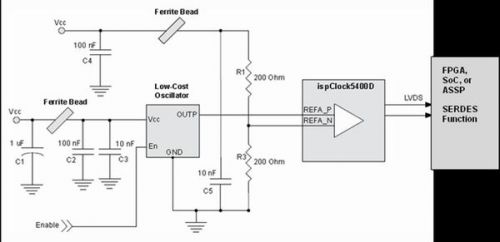

一个选用低本钱的振荡器和一个ispClock5400D器材的体系示例如下面图1所示。振荡器经过运用一些电容和铁氧体磁环来完成去耦并阻隔电源噪声。单端振荡器输出与分压器一同为时钟器材上的参阅输入供给一个差分信号。将参阅信号布线尽或许的接近,能够尽或许地削减共模噪声,进步信号的完好性。

图1:低本钱振荡器和ispClock5400D超低颤动参阅时钟。

运用ispClock5406D完成XAUI参阅时钟源

一般咱们能在XAUI规划中找到SERDES运用。XAUI SERDES的作业频率为3.125GHz,并有0.35 UI(单位距离)的严厉的颤动要求,一个单位距离为一个完好的波形周期。(3.125 GHz的周期是1/3.125GHz或320ps。那么320ps的0.35 UI便是120ps)。一种常见的树立片上3.125GHz SERDES时钟的办法是运用一个精确的输入参阅时钟,时钟频率为1/10的SERDES速率或312.5MHz。该参阅时钟有必要满意精确,以确保SERDES规划能满意XAUI规范的严厉颤动要求。

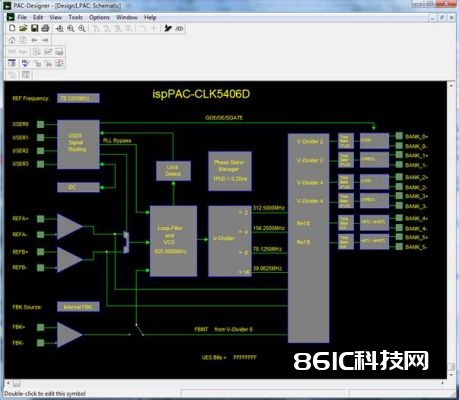

isp5406D可经过依据GUI的规划软件(莱迪思的PAC – Designer 5.2)轻松装备。装备ispClock5406D的GUI如图2所示。可经过该器材的框图界说不同的装备选项。用户只需简略地双击框图中的功用,然后会打开一个对话框,显现该功用的各种可编程挑选。例如,在右上角的对话框中,用户能够输入参阅时钟频率和反应信号源。

图2:PAC-Designer 5.2中显现的莱迪思ispClock5406D框图。

如图2所示,环路滤波器和VCO块的参阅时钟输入源能够从REFA或REFB差分输入中挑选。V分频器块运用环路滤波器和VCO块的输出来发生由PLL的几分频(2、4、8和16分频)决议的四种频率。来自输出V分频器块或用于外部反应的FBK输入的反应信号,供给了可与VCO“匹配”的参阅时钟。假如挑选输出V 分频器块较小的分频数的信号来匹配输入参阅时钟,其反应信号将是挑选较大分频数信号的几倍,这就发生了有用的频率是输入参阅时钟源几倍的参阅时钟源。在本示例中,将78.125MHz的输入参阅时钟源加到REFA并将V 分频器块的8分频输出作为反应,则其8分频的输出为78.125MHz,4分频的输出为156.25MHz,2分频的输出为312.5MHz。

V分频器的输出频率可用于布线矩阵阵列,也能够分配给恣意的isp5406D输出。每个输出都能够进行独立的相位和时刻偏移设置,能够针对走线延迟来调整输出或其它细节方面的时序考虑。最终,输出类型能够从M-LVDS、LVDS、LVPECL、HCSL x6、HSTL/eHSTL、SSTL 1.5V/SSTL 1.8V或SSTL 2.5V中恣意挑选。在示例规划中312.5MHz和156.25MHz信号可经过BANK_0至BANK_3的输出获得,运用LVDS和LVPECL规范。还能够挑选REFB作为Bank 4和Bank 5的输出。这能够经过一些简略的时序调整来完成一个独立的时钟信号。

XAUI测验体系成果

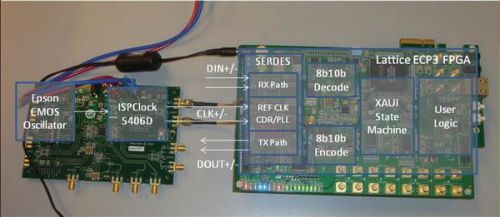

测验体系运用了ispClock 5406D评价板和LatticeECP3 FPGA开发板。测验树立的框图如图3所示,该规划中的开发板相片上标识了左边是ispClock5406D板,右侧是ECP3 FPGA板。(请注意,两个板之间运用SMA电缆传输时钟信号。这是一个比集成的时钟解决方案更具应战性的信号环境。)

Epson CMOS振荡器的作业频率为78.125MHz,用作ispClock 5406D的参阅时钟。ispClock 5406D经过编程以4倍的参阅频率即312.5MHz,用作运用LatticeECP3 FPGA完成的XAUI规划的时钟源。运用片上ECP3的CDR/PLL块,完成了超低颤动、频率为312.5MHz 10倍的参阅时钟。3.125GHz时钟分配给高速的XAUI 功用部分:SERDES的接纳器(RX)和发送器(TX)块以及8b10b解码和编码块。

图3:运用ispClock 5406D的XAUI体系。

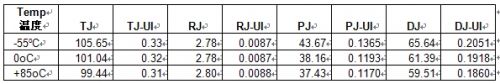

在颤动测验时,XAUI状态机经过编程输出规范的PRBS7测验图形。这从TX块和DOUT+/-信号上显现出来,标识于图3中LatticeECP3 FPGA块的底部方位。这些输出连接到Agilent DSO-81304B的输入,以获取具体的颤动数据。图4以图形方式显现了0℃下的重要丈量成果。在-55℃和+85℃下也进行了相似的丈量。图4底部的表格显现了测验过程中的要害颤动丈量成果。总颤动丈量值需满意120ps(0.35UI)的XAUI规范,即时在最差的情况下,当超越-55℃至+85℃温度时,也有必要满意105.65ps和0.33UI。相同,这些契合规范的成果是在运用两块独立的开发板的情况下获得的。运用一块板的话应该发生更低的颤动成果。

图4:颤动测验成果。

表1

ispClock 5406D的装备存储在片上非易失性存储器中,可经过JTAG接口进行再编程。器材上的许多功用还能够经过I2C接口进行“即时”修正。依据ispClock 5406D的体系的可编程特性支撑许多附加功用,包含:TH和TCO时序裕度丈量,有助于规划安稳性的测验;运用发送和接纳通道间独立的偏移时钟的裕度测验,进步了可制作性;在数据有用窗口的中心进行精确的时钟对齐,增强了体系的可靠性。