手持设备的规划者,如规划智能电话、便携媒体播放器和GPS体系等,总是在寻觅各种办法来延伸产品中所用电池的寿数。杂乱可编程逻辑器材(CPLD)给在低功耗设备中集成特别逻辑和专用IP供给了灵活性。

使CPLD愈加招引关怀功耗的规划者的原因是呈现了“零功耗”CPLD,它们供给了全新的特征来延伸电池寿数。在手持设备中,可编程逻辑一般用于代替某些恣意逻辑,完成操控或履行短数据途径。具有低功耗和小体积长处的CPLD器材是这些运用的抱负挑选,这些“零功耗”CPLD器材具有各种立异特征来支撑手持设备的低功耗规划。

CPLD中下降功耗的技能

经过优化规划架构来下降功耗的完成办法有很多种,包含下降时钟频率、总线端接、低电压作业,以及约束总线负载等。但是,即便选用这些低功耗技能,惯例CPLD的功耗也常常使它们被扫除在电池供电设备之外,但现在,CPLD制造商现已开发出了“零功耗”的CPLD器材。

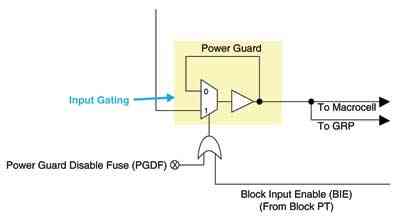

图1 输入门控功用是下降CPLD功耗的最简略办法

术语“零功耗”有不同的解说,它的原意是指CPLD具有非易失的、可当即上电运用的特征。现在“零功耗”的意义是指在大多数运用中CPLD具有许多节约功耗的特色,以及能够用于充沛削减器材功耗需求的中心逻辑。这些新的低功耗特征包含输入门控和上升速率的操控。例如,在一般CPLD中,当32个输入和32个输出在100MHz频率下翻转时会耗费 2.8mA的电流。但是,运用零功耗CPLD,经过输入门控技能,相同的规划仅耗费0.026mA的电流。

输入门控技能

不同制造商对输入门控的称谓不同,例如,Lattice半导体公司称其为“功率监督(Power Guard)”。输入门控是下降CPLD作业功耗的最简略办法,它经过将逻辑阵列与外部改动的输入信号断开来完成,因为任何状况改动的逻辑都耗费功率。当逻辑阵列不需求保存内部逻辑动作时,它就与外部输入源断开。而当使能输入门控时,内部逻辑和相应输出引脚就都维持在它们地点的状况。输入门控由I/O引脚和输入缓冲之间的逻辑组成。门控逻辑是由逻辑阵列内部宏单元之一的一个输出操控的,如图1所示。输入门控功用能够逐一引脚使能或制止。有些CPLD系列为一切的输入引脚供给了一个输入门控块,而别的一些CPLD则运用多个块来为很多I/O的单个部分供给准确操控。

上升速率操控

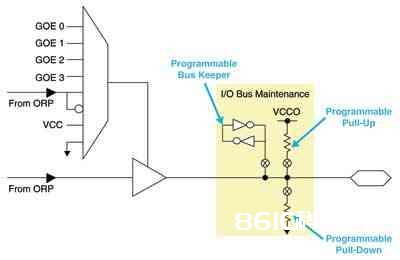

图2 总线坚持锁存器、上拉、下拉,或非端接的I/O内部结构

上升速率操控为每个I/O引脚供给了两种输出缓冲状况改动方法:快速和慢速上升速率。选用短PCB走线和杰出端接的规划能够挑选快速上升速率,这样做能够在以最快速率作业的状况和实际运用的低功耗状况间进行切换。关于长PCB走线和非端接的高速规划,慢速上升速率所发生的反射和噪声都很低,并使地弹噪声最小。

其他先进的CPLD特征

极低功耗CPLD器材的其他先进特征还包含输入迟滞、片上振荡器,以及可编程端接等。输入迟滞可认为慢速改动的输入信号供给改进的抗噪声功用。

最新的CPLD系列器材具有十分高效的I/O单元和在3.3V和2.5V输入信号上的悉数迟滞功用。假如规划者期望下降CPLD的功率功率,也能够挑选制止迟滞功用,以节约I/O单元的功率耗费。

为了下降体系整体本钱,先进的CPLD现在都包含一个片上振荡器用来供给体系时钟。振荡器一般用于上电次序操控、键盘扫描和显现操控器等。集成振荡器能够削减体系器材数,并节约了专用振荡器的本钱。在不需求片上振荡器的规划中,该部分能够被禁用,以下降功耗。

一切零功耗CPLD都为输入引脚供给了多种形式的可编程I/O端接方法,以此来下降因为外部三态总线所耗费的功耗。当非端接或起浮的输入信号在高电平和低电平逻辑之间漂动的时分,会耗费很多不确定的功率。

CPLD的类型不同,它们的功用也各异,大部分都具有总线坚持锁存器、上拉、下拉或非端接等,如图2所示。例如,Lattice半导体公司的4种类型CPLD都能够在每个引脚上指定上述功用。其他制造商的器材在每个引脚上能够挑选上拉和总线坚持,或许为总线坚持和上拉指定大局端接,而且每个引脚都能够被包含或排出端接信号组。

每一代手持设备都将一些添加的产品功用规划到更小的空间中,而且CPLD也成了计划的一部分。其间一个重要的原因便是CPLD能够“快速批改”ASSP和AS%&&&&&%器材中的一些规划问题。

CPLD制造商所供给的零功耗器材种类十分完全,不同价格的器材封装从小至5mm×5mm到大至28mm×28mm,可获得的I/O引脚数从21个到324引脚BGA封装中的270个。片式BGA封装供给了优化的I/O引脚数与封装尺度的比率,64个宏单元的ispMACH 4000ZE CPLD在5mm×5mm的封装中有52个I/O引脚,如图3所示,而且整个系列的CPLD也集成了功率监督(Power Guard)输入门控,每个器材包含2~16段的功率分区,能够在功率操控上完成更细的粒度。

增强的片上振荡器包含除n定时器模块,一切I/O引脚均支撑上拉、下拉和能够在每个引脚上被使能的总线坚持器。

图3 紧凑型5mm×5mm封装的CPLD能够供给52个I/O引脚

在器材上电过程中,一切I/O引脚都处于下拉形式,这能够下降从外部信号线上吸入电流的强度,一片32个宏单元CPLD的典型待机电流是10μA。

CPLD有助于规划优化

当功用和各种接口不断添加到已有规划中时,零功耗CPLD器材能够十分容易地完成这种需求,而且不会添加体系的功耗预算。回忆一下最近盛行的便携式GPS接收器便能够看到在接口和逻辑功用方面需求多个专用器材,包含一个SD卡接口、总线收发器和端口扩展器。这些功用都被集成到一个零功耗CPLD器材中,然后削减了设备所用器材的数量,下降了本钱,也添加了整体可靠性。