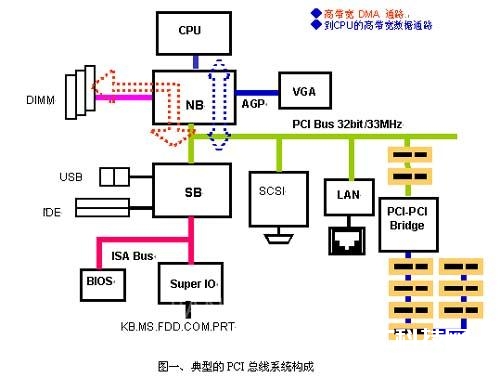

从1992年创建规范到现在,PCI总线已成为了事实上计算机的规范总线。由PCI总线构成的规范体系结构如图一所示。

PCI总线渐渐地替代了ISA总线。它有许多长处,比方即插即用(Plug and Play)、中止同享等。在这里咱们对PCI总线做一个深化的介绍。

数据宽度上看,PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种。现在盛行的是32bit @ 33MHz,而64bit体系正在遍及中。改进的PCI体系,PCI-X,最高能够到达64bit @ 133MHz,这样就能够得到超越1GB/s的数据传输速率。假如没有特别阐明,以下的评论以32bit @ 33MHz为例。

一、基本概念

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的优点是,一方面能够节约接插件的管脚数,另一方面便于完结突发数据传输。在做数据传输时,由一个PCI设备做建议者(主控,Initiator或Master),而另一个PCI设备做方针(从设备,Target或Slave)。总线上的一切时序的发生与操控,都由Master来建议。PCI总线在同一时间只能供一对设备完结传输,这就要求有一个裁定组织(Arbiter),来决定在谁有权利拿到总线的主控权。

32bit PCI体系的管脚按功能来分有以下几类:

体系操控: CLK,PCI时钟,上升沿有用

RST ,Reset信号

传输操控: FRAME#,标志传输开端与完毕

IRDY#,Master能够传输数据的标志

DEVSEL#,当Slave发现自己被寻址时置低应对

TRDY#,Slave能够转输数据的标志

STOP#,Slave自动完毕传输数据的信号

IDSEL,在即插即用体系启动时用于选中板卡的信号

地址与数据总线: AD[31::0],地址/数据分时复用总线

C/BE#[3::0],命今/字节使能信号

PAR,奇偶校验信号

裁定号: REQ#,Master用来恳求总线使用权的信号

GNT#,Arbiter答应Master得到总线使用权的信号

错误报告: PERR#,数据奇偶校验错

SERR#,体系奇偶校验错

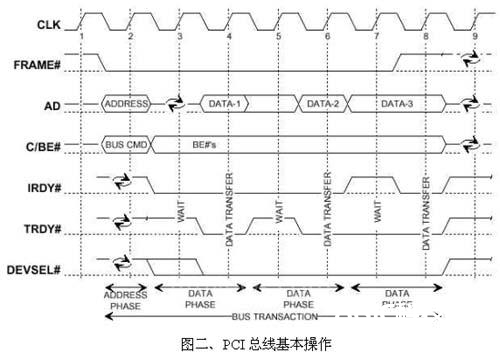

当PCI总线进行操作时,建议者(Master)先置REQ#,当得到裁定器(Arbiter)的答应时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,一起C/BE#放置指令信号,阐明接下来的传输类型。一切PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,能够传输数据。当Master数据传输完毕前,将FRAME#置高以标明只剩最终一组数据要传输,并在传完数据后铺开IRDY#以开释总线操控权。