1 导言

电信网和因特网是两大网络系统,必定存在两个网络数据或信息的互通问题,例如:VoIP、混合视频会议等新事务。E1接口和以太网接口别离是电信网和因特网运用最为遍及的接入端口,规划一个嵌入式网关设备,经过这两种端口将两大网络衔接起来就显得尤为火急、重要。本文介绍的AT91RM9200处理器处理才能强、接口丰厚,内部集成了同步串口和以太网接口,是嵌入式小型网关控制器的抱负挑选。

2 AT91RM9200和DS21554

AT91RM9200内部集成了一个ARM920T—ARM Thumb处理器,在180 MHz时钟时运行速度高达200 MI/s;内部有16 KB的数据Cache、16 KB指令Cache、写缓冲区、全功用的MMU(存储器办理单元);片内带有调试通道的仿真器、16 KB的SRAM和128 KB的ROM,支撑SDRAM、SRAM、Burst Flash,无缝衔接CompactFlashTM,SmartMediaTM和NAND Flash;增强型的时钟产生器和电源办理控制器,包括周期性中止、看门狗和带有报警中止的实时时钟;带有8个优先级、可单个屏蔽中止源、7个外部中止源和一个快速中止源;122个可编程I/O引脚(多功用复用);20通道DMA(直接存储器存取)控制器;10/100 Base-T型以太网控制器及介质无关接口MII,全速USB2.0接口(12 Mb/s,2主1从),3个同步串行控制器(SSC),4个通用同步/异步串口(USART),主机/从机串行外设接口(SPI),两线接口(TWI),两个3通道16位守时/计数器(TC)。超强的处理才能和丰厚的接口使得该处理器广泛使用于各种嵌入式通讯和控制系统中,尤其是同步串口和以太网接口,使其能够作为网关设备中心处理器。

电信网中数据以TDM(时分复用)方法传输,选用E1帧结构,相应网络接口包括电气接口和帧结构,契合ITU-T的G.703/G.704规范或许国标GB7611。DS21554是一个契合该规范的E1成帧器集成电路,内部集成了线路接口和成帧器,其主要功用有:契合规范的完好PCM30/32 E1收发器:内含一个64 KB缓冲器的HDLC控制器;8 bit并行控制器接口;供给随路信令(CAS)、共路信令(CCS)和CRC4帧格局;回环测验功用;HDB3编码的线路接口等。线路接口支撑75 Ω同轴电缆或许120 Ω双绞线衔接;背板接口能够根据需要在主、从形式下作业,供给同步接纳、发送数据信号(RSER/TSER),收发帧定位信号(RSYNC/TSSYNC),收发时钟信号(RSYSCLK/TSYSCLK);四个DS21554能够完成背板信号菊花链衔接,供给8192 KB/s字节复用同步数据流。

3 SSC特性剖析

AT91RM9200供给三个独立的同步串行控制器(SSC)与外部器材进行同步通讯。它支撑音频和电信使用中常用的串行同步通讯协议,如I2S、短帧同步、长帧同步方法等。

每个SSC包括独立的接纳器、发送器以及一个时钟分频器。发送器/接纳器别离有三个信号引脚:数据TD/RD信号、时钟TK/RK信号及帧同步。TF/RF信号,因为这些引脚与通用I/O引脚复用,初始化程序有必要装备使其在SSC形式下作业;每帧最多由16个32位字组成,可编程设定为主动发动或在帧同步信号检测到不同事情时发动。SSC与内部两个32位专用外设数据直接存取控制器PDC(Pe-ripheral DMA Controller)通道衔接,可在没有处理器干与的情况下进行接连的高速率数据传输。初始化程序装备使每帧为16个16位半字即每帧32字节,与E1帧对应;串口发送/接纳时钟由其作业形式决议,从形式时,TK/RK和TF/RF均为输入端子,由外部供给时钟和帧定位类型。主形式时,TK/RK和TF/RF均为输出端子,对E1成帧器供给时钟和帧定位信号,此刻,时钟信号TK/RK来历十分灵敏。

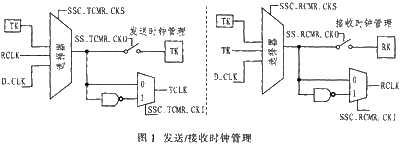

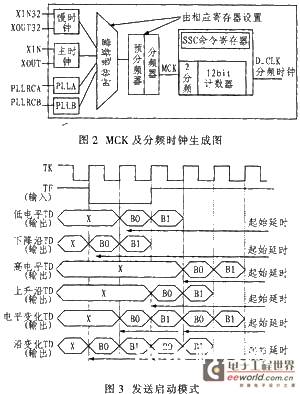

内部发送时钟TCLK(接纳时钟RCLK)来历十分灵敏,能够来自处理器主时钟MCK经SSC分频后得到的分频时钟D_CLK、TK引脚(RK引脚)或许RCLK(TCLK),如图1所示。处理器内部主时钟MCK经过初始化程序装备时钟挑选器、预分频器和分频器得到MCK,再经过SSC分频器使得分频时钟D_CLK为2.048 Mb/s,如图2所示。主形式下帧定位信号TF/RF也十分灵敏,经过装备相关寄存器,能够使其为正脉冲或许负脉冲,脉冲宽度能够调理,与发送/接纳信号的相位联系也能够灵敏调整,能够与规范的E1成帧器背板信号直接衔接。数据流中能够发送或许接纳一个特定符号数据(帧同步数据),相似于E1帧结构中的帧同步数据。每帧开始方位能够经过寄存器设置,帧脉冲收效后,数据开始方位与时钟信号有关,主要有4种形式:接连、TK/RK上升或下降沿触发、TK/RK高或低电平触发、TK/RK电平改变或沿跳变触发,如图3所示,接纳开始形式与发送相似。

发送数据或许接纳数据帧格局由发送器帧形式寄存器(SSC_TFMR)以及接纳器帧形式寄存器(SSC_RFMR)编程设定,能够别离设置的参数有:

发动数据传输条件;

帧脉冲前沿到第一个数据位的延时;

数据长度(DATLEN);

每帧传输的数据数(DATNB);

帧同步数据寄存器长度(FSLEN);

比特含义:高位或低位在前(MSBF)。

上述设置能够装备SSC同步串口每帧长度最大为512位长,因为E1帧格局每帧固定长度8×32位=256位,因而,装备恰当SSC相关寄存器不只能够确保SSC同步串口与E1接口时钟、帧脉冲、收/发数据等时序共同,并且数据帧格局也能保持共同。