网上材料

TFT屏

-支撑单色、4级灰度、256色的调色板显现形式

-支撑64K和16M色非调色板显现形式

-支撑分辩率为640*480,320*240及其它多种标准的LCD

关于操控TFT屏来说,除了要给它送视频材料(VD[23:0])以外,还有以下一些信号是必不可少的,别离是:

VSYNC(VFRAME) :帧同步信号

HSYNC(VLINE) :行同步信号

VCLK :像数时钟信号

VDEN(VM) :数据有用标志信号

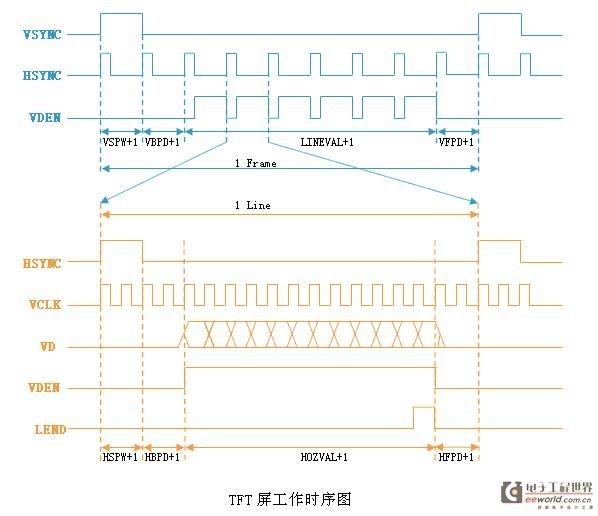

一般的TFT屏作业时序

外部引脚信号:

VSYNC: 笔直同步信号,表明扫描1帧的开端。

HSYNC: 水平同步信号,表明扫描1行的开端。

VDEN:数据使能信号。

VD[23:0] : LCD像素数据输出端口。

VCLK:像素时钟信号。

寄存器参数:

VSPW:笔直同步信号的脉宽,单位为1行(Line)的时刻。

VFPD: 笔直同步信号的前肩,单位为1行(Line)的时刻。

VBPD: 笔直同步信号的后肩,单位为1行(Line)的时刻。

LINEVAL :笔直显现尺度-1,即屏行宽-1。

HBPD:水平同步信号的后肩,单位为1VCLK的时刻。

HFPD:水平同步信号的前肩,单位为1VCLK的时刻。

HSPW:水平同步信号的脉宽,单位为1VCLK的时刻。

HOZVAL:水平显现尺度-1,即屏列宽-1。

由上图可知:

扫描一帧所需的时刻:

=((VSPW+1)+(VBPD+1)+( LINEVAL+1)+(VFPD+1))个行时刻。

扫描一行所所需的时刻:

= ((HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1))个VCLK时刻。

而一个VCLK时刻由LCD寄存器LCDCON1内的CLKVAL决议:

=HCLK/[2*(CLKVAL+1)]

因而扫描一帧所需的时刻:

T=[(VSPW+1)+(VBPD+1)+( LINEVAL+1)+(VFPD+1)]* [(HSPW+1)+(HSPD+1)+(HFPD+1)+ (HOZVAL+1)]* HCLK/[2*(CLKVAL+1)]

即帧频率为:1/T

要想正确运用LCD,有必要留意两点:1、时序;2、显现缓存区。

1、时序

LCD一般需求三个时序信号:VSYNC、HSYNC和VCLK。VSYNC是笔直同步信号,在每进行一个帧(即一个屏)的扫描之前,该信号就有用一次,由该信号能够确认LCD的场频,即每秒屏幕改写的次数(单位Hz)。HSYNC是水平同步信号,在每进行一行的扫描之前,该信号就有用一次,由该信号能够确认LCD的行频,即每秒屏幕从左到右扫描一行的次数(单位Hz)。VCLK是像素时钟信号。

s3c2440处理LCD的时钟源是HCLK,经过寄存器LCDCON1中的CLKVAL能够调整VCLK频率巨细,它的公式为:

VCLK=HCLK÷[(CLKVAL+1)×2]

例如,HCLK的频率为100MHz,要想驱动像素时钟信号为6.4MHz的LCD屏,则经过上式核算CLKVAL值,成果CLKVAL为6.8,取整后(值为6)放入寄存器LCDCON1中相应的方位即可。由于CLKVAL进行了取整,因而咱们把取整后的值代入上式,从头核算VCLK,得到VCLK=7.1MHz。

按理说,关于一个已知尺度(即水平显现尺度HOZVAL和笔直显现尺度LINEVAL已知)的LCD屏,只需确认了VCLK值,行频和场频就应该知道了。但这样还不可的,由于在每一帧时钟信号中,还会有一些与屏显现无关的时钟出现,这就给确认行频和场频带来了必定的复杂性。如在HSYNC信号先后会有水平同步信号前肩(HFPD)和水平同步信号后肩(HBPD)出现,在VSYNC信号先后会有笔直同步信号前肩(VFPD)和笔直同步信号后肩(VBPD)出现,在这些信号时序内,不会有有用像素信号出现,别的HSYNC和VSYNC信号有用时,其电平要坚持必定的时刻,它们别离叫做水平同步信号脉宽HSPW和笔直同步信号脉宽VSPW,这段时刻也不能有像素信号。因而核算行频和场频时,必定要包含这些信号。HBPD、HFPD和HSPW的单位是一个VCLK的时刻,而VSPW、VFPD和VBPD的单位是扫描一行所用的时刻。在s3c2440中,一切的这些信号(VSPW、VFPD、VBPD、LINEVAL、HBPD、HFPD、HSPW和HOZVAL)都是实践值减1的成果。这些值是经过寄存器LCDCON2、LCDCON3和LCDCON4来装备,只需把这些值装备成与所要驱动的LCD中相关内容的数据共同即可。例如,咱们所要显现的LCD屏巨细为320×240,因而HOZVAL=320-1,LINEVAL=240-1。水平同步信号的脉宽、前肩和后肩别离为30、20和38,则HSPW=30-1,HFPD=20-1,HBPD=38-1;笔直同步信号的脉宽、前肩和后肩别离为3、12和15,则VSPW=3-1,VFPD=12-1,VBPD=15-1。

下面咱们就详细核算一下行频(HSF)和场频(VSF):

HSF=VCLK÷[(HSPW+1)+(HSPD+1)+(HFPD+1)+(HOZVAL+1)]

=7.1÷408=17.5kHz

VSF=HSF÷[(VSPW+1)+(VBPD+1)+(VFPD+1)+(LINEVAL+1)]

=17.5÷270=64.8Hz

在有些情况下,s3c2440的LCD时钟信号的默许极性与所操控的LCD时钟信号的极性相反,这时能够经过寄存器LCDCON5的相关位来改动某些时钟信号的极性。

2、显现缓存区

只需把所要显现的数据放入显现缓存区内,就能够在屏幕上出现内容。该缓存区是咱们自己编程时拓荒的一段内存区。一般咱们是经过界说一个与屏幕尺度巨细相同的二维数组来拓荒该空间的,这样操控屏幕内容会便利一些,如当屏幕的尺度为320×240时,能够界说该缓存区为LCD_BUFFER[240][320]。由于s3c2440支撑16位和24位的非调色板真彩色的TFT型LCD形式,而24位色彩形式是用32位数据来表明的,所以前面界说的那个二维数据的数据类型应该是半字整型或全字整型的。例如,在24位色彩形式下,咱们想要在尺度巨细为320×240屏幕的中心处设置为白色像素,则:LCD_BUFFER[120][160]=0xffffffff。

在s3c2440中,寄存器LCDSADDR1和LCDSADDR2用于设置显现缓存区,即把咱们界说的那个二维数组告知s3c2440。其间LCDBANK的9位数据指定LCD的BANK,即显现缓存区的第30位到第22位地址;LCDBASEU的21位数据指定了LCD的基址,即显现缓存区开端地址的第21位到第1位;LCDBASEL的21位数据指定了LCD的尾址,即显现缓存区完毕地址的第21位到第1位。例如,咱们想要在尺度为320×240的屏幕上显现24位色彩,界说的显现缓存区数组为LCD_BUFFER[240][320],则LCDBANK等于LCD_BUFFER的第30位到第22位数据值(由于LCD_BUFFER表明的便是数组的首地址),LCDBASEU等于LCD_BUFFER的第21位到第1位数据值,由所以用32位数据表明24为色彩,因而每个像素值是4个字节,所以LCDBASEL等于(LCD_BUFFER+(240×320×4))成果的第21位到第1位的数据值。别的寄存器LCDSADDR3有两个内容:OFFSIZE和PAGEWIDTH。OFFSIZE用于虚拟屏幕的偏移长度,假如咱们不运用虚拟屏幕,就把它置为0;PAGEWIDTH界说了视口的宽,单位是半字,如在上面的比如中,PAGEWIDTH应该为320×32÷16。