高速长线阵CCD(电荷耦合器)具有低功耗,小体积,高精度等优势,广泛应用于航天退扫体系中的图画数据收集。而CCD驱动电路规划是CCD正常作业的关键问题之一,CCD驱动信号时序是一组相位要求严厉的脉冲信号,只要时序信号和CCD杰出合作,才干充分发挥CCD的光电转化特性。现在CCD驱动电路主要有以下4种办法:IC驱动法,EPROM驱动法。单片机驱动法以及可编程逻辑器件驱动法。前3种办法存在着灵活性差,精度低,可调试性差等特色,本文研讨的依据FPGA(现场可编程门阵列)的驱动电路规划办法具有集成度高,可靠性好,调试性好等特色,十分合适高速线阵CCD驱动电路的规划。

1 IL—P4线阵CCD原理

IL—P4是DALSA公司出产的高速线阵CCD产品,具有8192个感光象元,像敏单元尺寸为7μmx7μm,像元总长为57.3 mm。双路奇偶输出,最高作业频率为40 MHz。

1.1 IL—P4的根本结构和作业原理

IL-P4为典型的埋沟道型二相线阵CCD。他由4 241×2个PN结光电二极管构成,其间前面的13×2个PN结用作阻隔和后边的32×2个PN结用作屏蔽而被遮盖的。中心的8 192个光电二极管是曝光像敏单元。光敏元的两边是用作存储光生电荷的搬运栅。搬运栅的两边为CCD模仿移位寄存器,它的有用像素单元(8 192像元)分奇,偶两列搬运并别离由OS1,OS2端口输出。

1.2 IL-P4驱动时序剖析

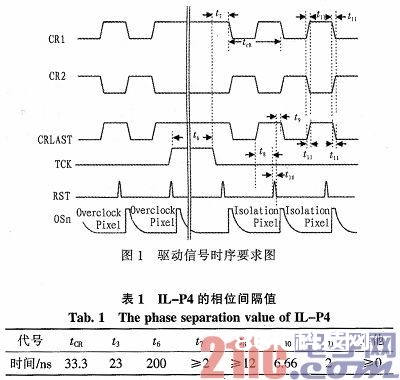

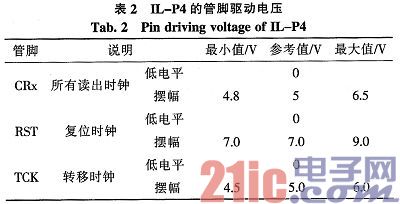

IL—P4正常作业时需求五路驱动时序,别离是两相时钟信号CR1,CR2、搬运脉冲信号TCK、像元复位信号RST、最终像元读出信号CRLAST。各相位之间有必要满意严厉的时序要求,才干确保CCD正常作业,各时序的相位联系如图1。这儿需求着重的是TCK与CR1和CR2的联系,当TCK为高电平时,CR1和CR2也需求同步变为高电平,而且CR1脉冲有必要比TCK提早上升,推迟下降t7时刻,CR1脉冲提早上升意味着移位寄存器中接纳电荷包构成,有利于电荷搬运,CR1脉冲推迟下降能使存储栅和移位寄存器阻隔,避免CR1的移位寄存器中的电荷倒回原势阱中,而且当TCK为高电平期间,RST有必要坚持低电平,表1为图1中各脉冲之间应满意的相位距离值。

2 CCD驱动电路规划

2.1 驱动电路硬件规划

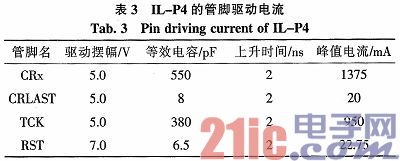

本规划中选用Intersil公司的EL7457作为体系的管脚驱动芯片,EL7457是一款高速的四路驱动芯片,单路最高能够供给2A的驱动电流,其时钟频率最高能到达40 MHz,彻底能够满意本规划中的要求,IL—P4管束驱动的峰值电流如式(1)所示

其间Cpin为管脚等效%&&&&&%,Vswing为驱动信号上升沿摆幅,trsing为驱动信号上升沿时刻,Ipeak管脚驱动的峰值电流。

IL-P4-8192B的管脚驱动电压和峰值电流别离如表2和表3所示。

2.2 驱动时序信号规划

IL-P4的最高作业频率可达40 MHz,依据需求选取的作业频率为30 MHz。依据表1中IL-P4各路脉冲时序相位距离值要求,能够确认CCD根本驱动信号CR1、CR2、TCK、RST、CRLAST的参数。各路脉冲技术指标如下:CR1=CRLAST=~CR2=30 MHz,占空比为1:1,方波;TCK=7.24K,脉冲宽度为200 ns,低电平宽度为138μs,方波;RST=30 MHz,占空比为1:4,方波。

用Verilog HDL言语作为开发言语,软件渠道则是Xilinx公司的ISEl3-4。依据上述对驱动时序的剖析,归纳考虑各信号的脉冲宽度,选用50 MHz的外部晶振作为输入时钟,通过Spartan 3E的DCM模块倍频到120 MHz,作为整个体系的基准时钟。运用计数分频的规划办法来完成驱动电路。Clk_base为通过DCM模块后的120 MHz基准时钟,通过时钟上升沿触发计数,cnt_div4为计数变量,该变量为两位二进制变量,计数溢出时会主动归零,因而通过判别cnt_div4的值,完成频率30MHz.占空比为1:4的RST驱动信号的生成,以及频率为30 MHz,占空比为1:1的CR1,CR2驱动信号的生成,在硬件电路上,CRLAST与CR1通过一个50欧姆的电阻相连,因而FPGA只需求输出CR1即可,cnt_pix为像元计数变量,结合驱动时序要求,TCK高电平持续时刻为6个像元输出时刻,即200 ns,由此即完成了CCD作业所需求的五路驱动时序信号的发生。

3 仿真与实测成果

3.1 仿真

运用验证东西ISIM来进行功用验证。通过仿真得出的时序图如图2。依据仿真波形得出图2中各参数的值如下:

t3=33.3 ns、t6=200 ns、t7=22 ns、t8=14 ns、t10=6.66 ns。各参数均在表1的取值范围内。所以仿真成果满意CCD的驱动时序要求。

3.2 实测成果

图3为运用TEK公司的数字示波器所观察到的FPGA发生的驱动时序,信号2为搬运脉冲信号(TCK),信号1为像元复位信号(RST),信号4为CR1,信号3为CR2,由图3能够看到,在搬运脉冲信号高电平阶段,像元复位信号置低,CR1以及CR2别离坚持原状态,而且CR1脉冲比TCK提早上升,推迟下降,有利于电荷搬运,以及避免CR1的移位寄存器中的电荷倒回原势阱中。

成果表明运用依据Verilog HDL的分频器发生CCD作业需求的时序信号计划的可行性和正确认,而且该计划依据FPGA,具有精度高,速度快,可靠性好以及便于调试的特色。

4 定论

高速长线阵CCD(电荷耦合器)具有低功耗,小体积,高精度等优势,广泛应用于航天退扫体系中的图画数据收集。由软件仿真和示波器测验成果可得出,驱动电路输出信号的相位联系和脉宽满意时序规划要求,波形较好。该计划充分发挥了FPGA的可编程的特色,选用Verilog HDL描绘的分频器规划的驱动电路功能安稳,速度快,可靠性好,结构简略,相对于传统的驱动电路,该计划极大地简化了驱动电路结构和规划进程。