摘要:传统的多路同步信号源常选用单片机搭载多片专用DDS芯片合作完成。该技能完成杂乱,且在要求各路同步相干可控时难以完成。本文在介绍了DDS原理的基础上,给出了用Verilog_HDL言语完成相干多路DDS的作业原理、规划思路、电路结构。使用Modelsim仿真验证了该规划的正确性,本规划具有调相便利,相位接连,频率稳定度高级长处。

关键词:DDS;现场可编程门阵列(FPGA);相位累加器;Verilog_HDL

完成信号源的多路同步输出且各路间具有固定的相位联系,在雷达、通讯等多范畴有着重要的使用。为了完成此功用,大多数规划是使用单片机操控多个专用DDS芯片,完成多信号同步输出,如图1所示。但腱因为选用分立的专用DDS芯片,各芯片参数很难做到完全相同,参数的差异会形成输出信号频率和相位不同。因而,虽然各DDS芯片选用同一频率字,各个输出信号频率也难以完全相同。相同,因为参数的不一致,波形之间的相位也难以做到同步精确可调,更重要的是各个信号通道间频率差异的累积效应可能会导致同步失利。因为这些原因,要完成多路同步输出且各路信号间成相干联系有必要选用别的的体系。本文给出了一种根据FPGA的3路相干信号源规划方案。

1 DDS基本原理

DDS(Direct Digital Synthesizer)的本质足对相位进行可控等问隔的采样。一个DDS信号发生器是由:相位累加器、正弦查找表(波形Rom表)、数模转换器以及模仿低通滤波器(LPF)组成,原理框图如图2所示。

DDS体系的中心是相位累加器。相位累加器在参阅时钟信号的操控下发生读取Rom表数据的地址值,随后经过查表改换,读出相应地址的信号波形的数字起伏值序列,再由数模改换器将代表波形起伏的数字序列转化为模仿电平,最终经由低通滤波器滤除高频重量使波形滑润。

2 根据FPGA的3路同步输出DDS作业原理

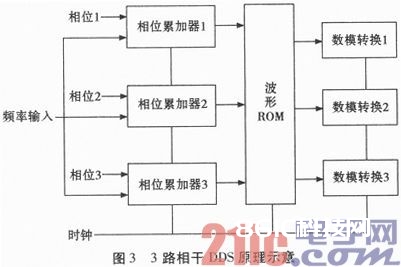

3路同步相干DDS信号源作业原理如图3所示。

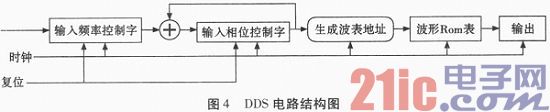

一切的部分都在一致时钟的操控下确保了各路信号的同步输出;各频率输入为同一操控字,使得各信号间有很好的同频性;不同的相位输入决议了各路间固定的相位差,满意了相干性要求。在FPGA里边做到的是D/A转换器之前的部分。3路信号结构相同,每一路的电路结构如图4所示。

3 电路规划

3.1 电路整体接口

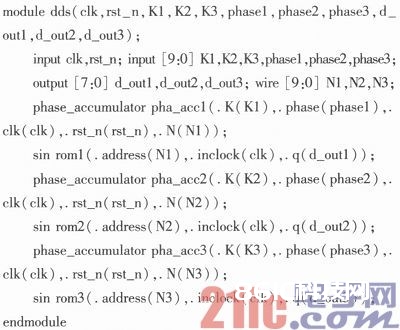

本体系选用Verilog言语编程,归纳东西为Quartusii,仿真东西为Modelsim。

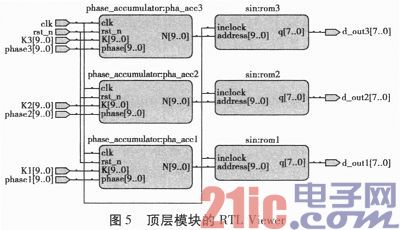

电路接口有clk,rst_n,K1,K2,K3,phase1,phase2,phase3,d_out1,d_out2,d_out3,其间clk为体系时钟,rst_n为复位信号低电平异步复位,K1,K2,K3为频率操控字输入(本体系为同一输入),phase1,phase2,phase3为3路相位输入,d_out1,d_out2,d_out3为3路输出。

3.2 源程序代码代码

顶层模块代码如下所示,

顶层模块的RTL Viewer如图5所示。

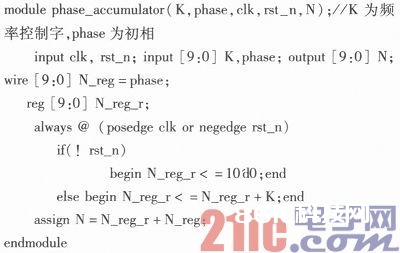

相位累加器模块代码如下所示。

波形ROM表使用Quartus ii软件的插件管理程序Megawizard plug-in manager取得,关于波形数据mif文件的取得这儿使用了专用软件Guagle_Wave。

4 仿真与剖析

仿真测验文件代码如下。

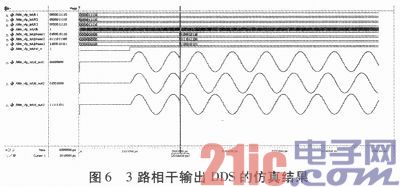

3路相干输出DDS的仿真成果如图6所示。途中竖线为相位跳变处,从此之后各路信号坚持了杰出的相干性,由此可见满意了规划要求。本规划只需改动各路的相位操控字就可完成各路之间的相位调整。本规划运用Vefilog言语结合DDS原理和FPGA器材,完成了多路相干信号源规划,相位接连可调,且易于调理。