在编写软件时,您有没有遇到过不管怎样尽力编码,软件都不能按您期望的速度运转?我遇到过。您有没有想过,“有没有什么简略并且本钱不高的办法可将一些代码输入多个定制处理器或定制硬件?”究竟,您的运用仅仅许多运用中的一个,并且创立定制硬件需求花费时刻和本钱。是不是这样?

最近听说了赛灵思的高层次归纳东西Vivado®HLS后,我开端从头考虑这一问题。高层次归纳东西与Zynq®-7000 All Programmable SoC的结合为规划拓荒了新的或许性,其间Zynq®-7000 All Programmable SoC结合了带有FPGA架构的双核ARM®CortexTM-A9处理器。这类东西能够用C言语,C++言语或SystemC源代码创立高度优化的RTL。近年来,呈现许多这项技能的供给商,且其采用率也不断提高。

假如我只用Vivado HLS便能完结要求更高的核算,那么将那些慢速代码迁移到硬件中会有多难?究竟我经常用C++言语编写代码,而Vivado HLS将C/C++言语作为输入言语。ARM处理器内核意味着我能够在惯例环境下运转大都软件。事实上赛灵思还供给了一款软件开发东西(SDK)以及PetaLinux来帮您完结这一意图。

架构问题

从软件视点考虑这一改变,我开端愈加忧虑软件接口问题。究竟,HLS创立的硬件专心于处理硬件接口。我需求一些易于拜访的东西(如协处理器或硬件加速器)来加速软件运转速度。并且,我不想编写新的编译器。为了便利与软件的其它部分交流数据,这个接口应该类似于简略的存储单元,咱们能够在其间输入信息并稍后读取成果。

然后我有了新的发现。Vivado HLS支撑以相对较小的尽力轻松创立AXI从接口。这让我开端考虑,创立加速器或许没有那么难。所以,我编码了一个简略的实例来探究这种或许性。探究的成果让我惊喜不已。

下面看看我用了什么办法,并考虑这种办法所得出的成果。

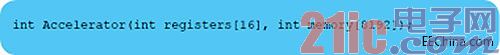

在我的实例中,我挑选了对一系列简略的矩阵运算(如加法和乘法)进行建模。我不想将它约束在固定的巨细,因而,我有必要一起供给输入阵列及各阵列的尺度巨细。抱负的接口会将一切数值作为函数的自变量,例如图1中的代码。

硬件接口需求用一种简略的办法将函数自变量映射到存储单元。图2是支撑这一映射的存储器装备。寄存器中保存了有关矩阵的摆放办法以及所需运算的信息。指令寄存器将指示履行何种运算。这样我便能够将一些简略的运算融合到一个硬件中。能够用状况寄存器来检查是否正在进行运算或是现已成功完结运算。此外,器材最好还能供给中止支撑。

回到硬件规划,我了解到Vivado HLS为阵列自变量留出空间以指定小容量内存。这样,图3所示函数便说明晰这种函数性。

假定能够归纳AXI从接口,怎样将它用在软件上?我将正常编码环境假定为Linux。还好赛灵思供给PetaLinux,并且PetaLinux供给一种叫做用户I/O器材的机制。UIO能够用简略的办法将新硬件映射到用户内存空间,并具有中止等候才能。这意味着您能够省去编写器材驱动程序所消耗的的时刻和流程。图4显现了这个体系。

这种办法当然也有缺点。例如,无法在DMA中运用UIO器材,因而您有必要在器材内存中构建矩阵,并在构建完结后手动仿制出来。假如需求,将来能够经过定制器材驱动程序处理这个问题。

用Vivado HLS归纳硬件

现在回到归纳AXI从接口的论题。它的归纳难度有多大?我发现这些编码约束十分合理。除内存的动态分配以外,大大都C ++言语都能够运用。

究竟硬件在运转过程中不能出产其自身。这约束了规范模板库(STL)功用的运用,由于这儿很多运用了动态分配。只需数据坚持静态,大都功用都能够运用。起先这项使命好像十分深重,但我发现这并不是什么大事。别的,Vivado HLS答应C++类、模板、函数和运算符重载。我的矩阵运算可容易归入定制矩阵分类。

添加I/O来创立AXI从接口十分简略。只需添加一些能够指示包含哪些端口以及运用哪些协议的编译指示即可。

只需我不按下一切旋钮,运转这款归纳东西十分简略。图5展现了其间各个过程,在此我不再具体解说。需求就方针技能和时钟速度对Vivado HLS进行一些引导。之后触及的程序会亲近重视违背方针的陈述并研讨剖析陈述以保证Vivado HLS按我所期望的办法运转。东西用户有必要对硬件方面有所了解,但有一些技能课程能够处理这个问题。还存在归纳前后运转仿真以查验预期行为的问题。

Vivado IP Integrator让AXI从接口衔接到Zynq SoC硬件变得垂手可得,并打消了对信号衔接过错的顾忌。赛灵思乃至具有我所运用的ZedBoard开发体系的体系概述,并用IP Integrator导出数据用于软件开发套件。

铲除瓶颈

我对成果十分满足,我期望能用这款芯片与东西集的组合做更多工作。我并没有探究一切的或许性。例如,Vivado HLS还支撑AXI主接口。AXI会答应加速器从外部存储器仿制矩阵(虽然这样也或许存在安全问题)。不过我强烈建议一切面对代码瓶颈的人都能考虑这个东西集。这儿供给满足的训练课程、资源和资料以完结快速匀变,其间包含Doulos供给的课程、资源和资料。如需了解更多信息,敬请拜访:www.doulos.com。

图1 – 调用加速器示例

图2 – 寄存器汇总表

图3 – 加速器函数API