摘要:以STM32F103VET6微处理器为中心,合作CR95HF射频芯片构成契合ISO/IEC 15693规范的便携式读卡器。一起,选用无线存储芯片M24 LR64,开发了与读卡器配套的新式无源RFID标签。该RFID体系作业在13.56 MHz频率,其标签的存储容量到达24 KB,并经过I2C总线完成数据传输,适用于需求在标签中带着很多数据的运用场合。试验证明,开发的RFID体系能安稳地进行无线数据通讯,具有作业安稳、适用性强的特色。

关键词:射频辨认;嵌入式体系;ISO/IEC 15693;CR95HF;大容量标签;M24LR64

导言

射频辨认(Radio Frequency Identification,RFID)技能是一种以射频信号为通讯载体非触摸的自动辨认技能,能够完成无线信息沟通。RFID技能选用射频信号传输数据,具有非触摸和在恶劣环境下作业等长处。此外,比较于其他辨认技能,RFID标签能够经过上位机操作读卡器进行读写,愈加便利和高效。因而,现在该技能已被广泛运用于交通运输、身份验证、门禁安全等范畴。依据供电方法,RFID标签能够分为有源、无源和半有源标签。

本文首要介绍了典型的嵌入式RFID体系,之后以意法半导体公司STM32F103VET6为中心与CR95HF射频芯片组成一个便携式读卡器。一起,针对现有RFID标签存在存储容量小、数据传输方法单一等问题,依据意法半导体供给的M24LR64芯片,研讨规划了一款运用于嵌入式RFID体系的大容量无源RFID标签。该读卡器和标签无线作业频率为13.56 MHz,契合ISO/IEC 15693规范,并支撑契合I2C总线规范的有线通讯;标签存储容量可达24 KB,能够满意便利带着和大容量存储的要求。

1 嵌入式RFID体系介绍

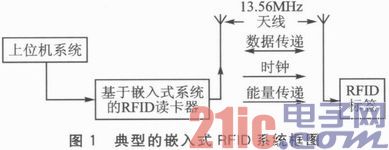

典型的嵌入式RFID体系一般包含以下部分:上位机体系、读卡器、射频标签。读卡器由嵌入式微处理器和射频芯片组成。上位机作业的流程大致分为读写两个部分:读取标签和向标签中写信息。读取标签信息时,上位机宣布指令信号存入微处理器,软件操控射频芯片发送读数据指令给标签,标签依据接收到的读数据指令将存储单元中指定的数据经过天线发送到读卡器,读卡器再将数据发送到上位机体系。向标签中写信息时,进程相似,上位机经过射频读卡器发送写指令,并将数据写到所规划标签的相应存储单元。典型的嵌入式RFID体系框图如图1所示。

2 依据嵌入式体系的读卡器和标签的规划

2.1 嵌入式RFID读卡器的规划

2.1.1 读卡器主控芯片及外围电路的规划

本规划主控芯片选用STM32F103VET6微处理器。该处理器依据ARM Cortex—M3内核,支撑多种通讯总线,作业频率为72 MHz,包含5个USART串行接口、2个I2C总线接口、3个SPI总线接口、CAN总线和USB总线。一起,该处理器还具有80个通用I/O口、A/D转换器、16位定时器、实时时钟等功能,具有功能强大、功耗低一级长处,能够满意本体系读卡器的规划要求。

读卡器选用规范USB 5 V供电,经过稳压芯片KF33BDT供给3.3 V电压供微处理器运用。为了抗干扰,微处理器的每个电源引脚都并联了0.1μF的去耦电容。微处理器的外部时钟源选用两个,分别为高速外部时钟源和低速外部时钟源。高速外部时钟源的晶振频率为8 MHz,用于为体系供给精准的主时钟;低速时钟源的晶振频率为32.768 kHz,用于为时钟或日历等供给时钟源。负载电容的挑选需求依据晶振的巨细进行匹配,本读卡器中高速外部时钟源的负载电容为20pF,低速外部时钟源负载%&&&&&%为10pF。sTM32F103 VET6微处理器经过串口与CR95HF射频芯片进行通讯,选用规范JTAG接口完成程序的烧写与调试,并经过USB总线与上位机高速通讯。