1、导言

自1971年,美国学者J.Tierney等人编撰的“A Digital Frequency Synthesizer”-文初次提出了以全数字技能完结数字频率组成以来,构成DDS元器材的速度的约束和数字化引起的噪声这两个首要缺陷阻止了DDS的开展与实践使用。近几年超高速数字电路的开展尤其是大规模超高速的FPGA技能的日渐老练,以及对DDS的深入研究,DDS的最高作业频率以及噪声功用已挨近并到达锁相频率组成器适当的水平。它具有较高的频率分辨率,能够完结快速的频率切换,并且在频率改动时能够坚持相位的接连,很简略完结频率、相位和起伏的数控调制。因而,在现代电子体系及设备的频率源规划中,尤其在通讯范畴,直接数字频率组成器的使用越来越广泛。而完结直接数字频率组成器的计划也较多,现在,用得最多的有三种技能计划,一种是选用高功用DDS单片电路的解决计划;二是选用低频正弦波DDS单片电路的解决计划;三是自行规划的依据FPGA芯片的解决计划。尽管有的专用DDS芯片的功用也比较多,但操控办法却是固定的,因而纷歧定是咱们所需求的。而使用FPGA则能够依据需求方便地完结各种比较杂乱的调频、调相和调幅功用,具有杰出的实用性,但由于编制VHDL源程序较为杂乱,因而也得不到很好的使用。本文使用Matlab/DSP Builder建模,然后很方便地在FPGA中完结DDS信号发生器的规划,避免了编制VHDL言语源程序的杂乱性,使规划制造一个需求的DDS信号发生器变得十分简略和方便。

2、DDS的根本原理

一个频谱纯洁的单频信号可标明为![]() 这种单频信号的首要特征是相位是时刻的线性函数,且相位函数对时刻的导数是一个常数。相位函数是一条直线,它的斜率便是信号的频率。假如对上式的信号进行采样,采样周期为Tclk,则能够得到离散的波形序列为:

这种单频信号的首要特征是相位是时刻的线性函数,且相位函数对时刻的导数是一个常数。相位函数是一条直线,它的斜率便是信号的频率。假如对上式的信号进行采样,采样周期为Tclk,则能够得到离散的波形序列为:

![]()

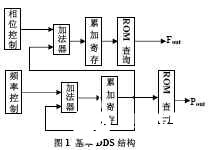

相应的离散相位序列的接连两次采样之间的增量为![]() ,若采样值在采样距离内坚持,则波形和相位变成了阶段梯形。依据采样定理,能够通过查表法发生波形,即规划一操控电路,使之依照必定的地址联系从存储器傍边读取数据,进行数模转化,就能够得到必定频率的输出波形。其根本的电路框图可用图1来标明。

,若采样值在采样距离内坚持,则波形和相位变成了阶段梯形。依据采样定理,能够通过查表法发生波形,即规划一操控电路,使之依照必定的地址联系从存储器傍边读取数据,进行数模转化,就能够得到必定频率的输出波形。其根本的电路框图可用图1来标明。

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率操控字k与累加寄存器输出的累加相位数据相加,把相加后的成果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲效果后所发生的新相位数据反应到加法器的输入端,以使加法器鄙人一个时钟脉冲的效果下持续与频率操控字k相加。这样,相位累加器在时钟效果下,不断对频率操控字进行线性相位累加。由此能够看出,相位累加器在每一个时钟脉冲输入时,把频率操控字累加一次,相位累加器输出的数据便是组成信号的相位,相位累加器的溢出频率便是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址,这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完结相位到幅值转化。波形存储器的输出送到D/A转化器,D/A转化器将数字量方式的波形幅值转化成所要求组成频率的模拟量方式信号。低通滤波器用于滤除不需求的取样重量,以便输出频谱纯洁的正弦波信号。

3、DDS在MATLAB/DSP Bulider中的模型树立及在FGPA中完结

3.1 在MATLAB/DSP Bulider建模

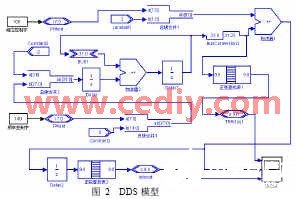

依据DDS的作业原理,能够使用MATLAB树立DDS根本原理图的模型如图2所示,其间正弦查找表的Matlab Array一项填写“ ”,即在让SignalCompiler在编译过程中,主动发生1024个正弦波数据,此波形数据存放在DSP Bulider模型文件夹的一个扩展名为.mif文件里。别离设置频率操控字和相位操控字为100和200后,进行仿真,翻开SCOPE调查其波形,发现其频率能够受频率操控字的操控,其相位也能够受相位操控字操控。仿真正确后,双击Singacompler图标,将此模型转化成VHDL源程序。通过剖析转化后的VHDL程序并将其转化为ATOM netlist,最终编译ATOM netlist,无误后标明建模已完结。

3.2 在Quartus II 4.0中进行编译仿真生成FPGA下载文件

翻开 Quartus II 4.0,找到DDS的Quartus II 4.0项目文件并翻开。设置好方针器材,编译后再进行一次仿真。其仿真波形如图3所示。由此能够看出,其输出波形即为咱们需求的正弦波数据。最终锁定好引脚,下载到方针器材,完结DDS模块芯片的规划。

4、结语

由上面的规划咱们能够看出选用MATLAB/DSP Bulider建模,再在Quartus II 4.0中进行编译,最终下载到方针器材这种办法完结数字频率组成办法,既避免了VHDL编程的杂乱性,并且又便于修正和扩大其功用,到达需求的信号。如要改动输出波形的的步进精度,以及假如要添加起伏操控等,则只需求在模型中作简略的修正即可,行将频率操控字、相位操控字的宽度改动即可。如要添加起伏操控,则只需求在模型顶用一乘法器操控输出起伏即可完结。因而选用此种办法,完全能够依据用户需求定制一个DDS信号发生器,而不需求添加太多的本钱。本文作者立异点,充分使用了嵌入到MATLAB中的DSP Bulider东西的强壮功用,完结DDS信号发生器的建模,并给出了详细的模型。避免了杂乱的VHDL程序编制,一起也充分使用了FPGA的规划的灵活性,完结用户需求的DDS信号发生器规划。

责任编辑:gt