跟着人们生活水平的进步,公路上的私家车辆也增多了,但随之带来的问题便是交通事故发生率居高不下,严重危害着人们的生命安全。文中就怎么防备交通事故发生,研讨规划一种呼应敏捷、高可靠性并且经济实用的轿车防擅报警设备。该设备在规划过程中的要害使命是使用置于轿车车头左右两头的双路通道高速收集激光雷达回波信号并对其进行实时存储和处理,从而快速丈量本身交通工具与障碍物之间的间隔及相对速度。

1 体系概述

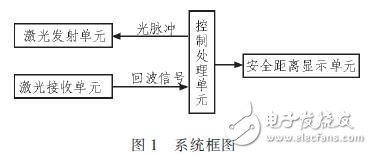

对用于高速公路中的雷达体系而言,考虑到开车的速度比较快,关于一些突发事件无法马上做出呼应,因而就要求规划的防撞雷达勘探间隔尽量长些,可让驾驶员提早做好安全准备作业,因而这种高速公路防撞体系一般选用激光勘探法。选用激光测距的轿车防撞体系结构图,如图1所示。

2 硬件整体规划原理及框图

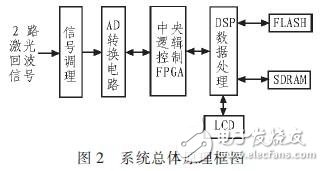

关于激光雷达回波信号经过光电器材转化后构成的电信号,其信号频率高,脉冲宽度相对比较窄,信号起伏低,布景噪音大,如果是选用低速的数据收集体系进行数据收集的话,那么将会存在数据精度不高的缺乏,所以有必要选用高采样率、高分辨率的数据收集体系。体系整体原理框图如图2所示。

该体系的首要信号流程:由激光传感器取得的2路激光雷达回波信号先经过缓冲扩大等前端调度后,一起送到AD转化电路进行模数转化,然后可以一起被中心逻辑操控模块FPGA来收集,这样相关于用DSP的分时收集来说,极大的进步了速度。FPGA一方面完结对A/D的采样操控,另一方面与DSP的EMIF接口构成传输通道,完结了AD与DSP之间的数据传输使命,避免了ADC直接与DSP通讯,降低了对很多的数据传输的压力。

2.1 前端信号调度电路

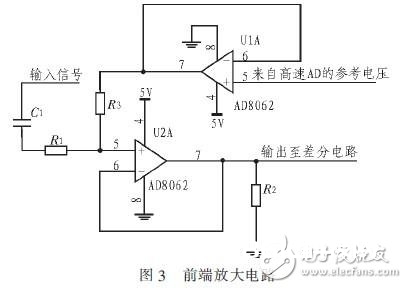

2.1.1 前端扩大电路

从传感器中输出的信号有必要经过调度才可以有效地进行数据收集,为了到达最高的丈量精度,应该使被测信号的电压改变规模扩大至ADC最很多程邻近,所以需要将传感器出来的小信号经过前端扩大电路线性扩大成合适体系的的电信号。在本体系中首要选用了AD公司出产的AD8062低成本的运放模块来完结的,如图3所示。

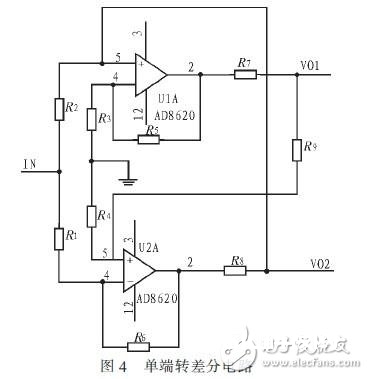

2.1.2 前端差分电路

为了消除偶次谐波重量,按捺共模噪声源,起到体系抗搅扰的作用,本体系的AD转化电路选用差分输入的方式,而信号经过扩大电路后得到的是单端信号,所以,有必要要将前端的输入单端信号转化为差分信号。本规划选用了ADI公司出产的AD8620驱动芯片构成差分驱动电路,其详细电路规划如图4所示。

2.2 AD转化电路

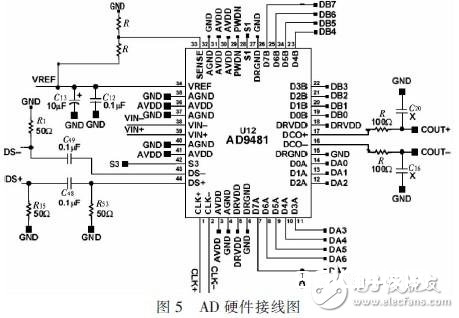

在数据收集体系中AD是比较重要的环节,首要完结对激光回波信号的收集作业,而采样时钟信号可以由FPGA电路内部的时钟模块来供给。ADI公司的AD9481,可以选用差分输入,采样率到达250 MSPS,并且选用250 M的PECL规范的时钟信号,为此在规划中为发生该差分时钟信号,考虑选用MC100LEL16的时钟芯片。AD9481的数字输出归于并行接口,有16位的数据流,关于这么高速的数据与存储会呈现竞赛冒险,使体系不稳定,因而在规划时AD与FPGA的输出端之间串接了一个100 Ω的电阻,可以消除呈现在0~1之间的毛刺与高速数据线之间的搅扰,详细的AD硬件原理如图5所示。

2.3 数据处理部分硬件电路

本体系数据处理部分由FPGA和DSP两个部分来完结。依据前一级AD电路的信号输出时序进行VHDL编程,来完结一起对两路AD输出的数字信号的收集,将数据输入到FIFO模块中,然后经过EMIF总线将数据快速传输到DSP里进行相关算法的运算。

2.3.1 FPGA电路

FPGA选用硬件编程完结杂乱的逻辑功用,不只可以对收集到的大批量数据流进行预处理,并且作为整个操控体系的中心部分,供给体系所需的时钟信号,确保数据的有序收集,并且作为数据传输的枢纽,确保了AD与DSP进行数据传输。结合采样存储传输等功用FPGA的模块首要分为4个部分:时钟办理模块、A/D操控模块、FIFO缓存模块、与DSP的EMIF接口模块:

1)时钟办理模块,该部分首要是发生体系所需的各模块的时钟信号,本体系选用ISE软件自带的DCM模块来完结。