AD9571相关信息来自ADI官网,详细参数以官网发布为准,AD9571供给信息可在查IC网查找相关供给商。

产品概况

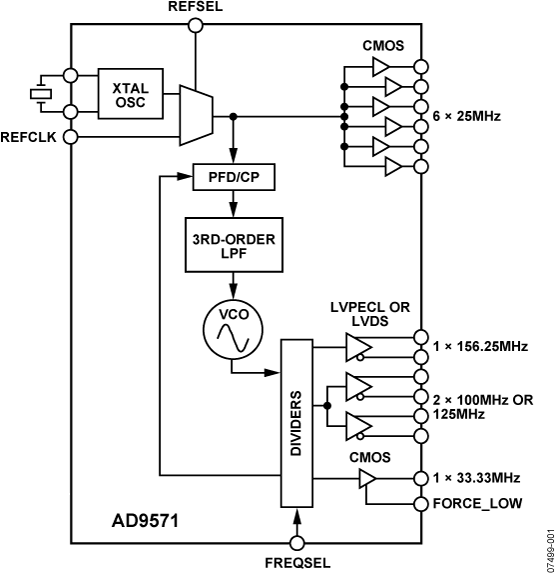

AD9571具有多路输出时钟发生器功用,内置专用PLL内核,针对以太网线路卡使用进行了优化。整数N PLL规划根据ADI公司老练的高功能、低颤动频率合成器产品系列,保证完成最高的网络功能。这款器材也合适相位噪声和颤动要求严厉的其它使用。

PLL部分由低噪声鉴频鉴相器(PFD)、精细电荷泵(CP)、低相位噪声电压操控振荡器(VCO)和预编程反应分频器与输出分频器组成。经过将外部晶振或基准时钟衔接至REFCLK引脚,可将最高达156.25 MHz的频率确定至输入基准。

每个输出分频器和反应分频器分频比都针对要求的输出速率进行预编程。无需外部环路滤波器元件,然后节省了名贵的规划时刻和电路板空间。

AD9571供给40引脚6 mm × 6 mm引脚架构芯片级封装,选用3.3 V单电源供电。工作温度规模为−40°C至+85°C。

优势和特色

- 彻底集成VCO/PLL内核

156.25 MHz时,颤动值:0.17 ps均方根值(1.875 MHz至20 MHz)

125 MHz时,颤动值:0.41 ps均方根值(12 kHz至20 MHz)

输入晶振或时钟频率:25 MHz - 针对156.25 MHz、33.33 MHz、100 MHz和125 MHz预设分频比

- 可选LVPECL或LVDS输出格局

- 集成环路滤波器

AD9571电路图

AD9571中文PDF下载地址

AD9571下载链接地址:https://www.analog.com/media/en/technical-documentation/data-sheets/AD9571.pdf

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/xinpin/yuanjian/42583.html