可编程片上体系( SoPC)是在可编程逻辑器材的根底上发展起来的一种灵敏、高效的嵌入式体系规划解决方案,体系规划者能够从传统的板级体系规划转换到芯片级体系规划,将体系规划中所需求的各个功用单元以IP ( Intellectual Property)的办法集成到FPGA中,完结集成度更高的嵌入式体系。

Virtex-4系列FPGA是由Xilinx公司推出的包含多个面向特定范畴渠道的FPGA产品,各个系列的FPGA经过对嵌入式处理器、高功用DSP功用单元、增强时钟办理、存储器、并行和串行I/O、混合信号以及其它功用模块等的优化组合使其能够满意特定范畴的运用需求。Virtex-4系列的三个渠道别离是:针对逻辑运用的Virtex-4 LX,针对超高功用信号处理的Virtex-4SX,针对嵌入式处理和高速串行衔接的Virtex-4 FX。其间Virtex-4 FX系列FPGA首要是为杂乱体系运用供给优化,特别是网络、存储、电信和嵌入式运用中的高速串行衔接和嵌入式处理,在其配套的EDK环境中还为体系规划者供给丰厚的总线、时钟、外设、JTAG口等IP资源,使规划者能够便当的建立自己的嵌入式体系。

1 Virtex-4 FX系列FPGA介绍

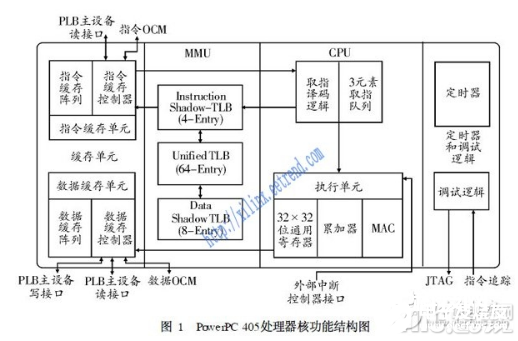

Virtex-4 FX系列FPGA芯片内至少包含一个PowerPC405处理器核,其功用结构如图1所示,该处理器核为32位哈佛结构的R ISC硬核,最高作业频率为400MHz。PowerPC405处理器包含以下功用单元: ( 1)5级数据通道流水线,包含取指、译码、履行、写回、装入写回5 级流水段; ( 2 ) 一个虚拟内存办理单元(MMU) ,支撑可变页面巨细和写保护、操控拜访选项;(3)独立的指令Cache和数据Cache; ( 4)支撑调试和盯梢,包含一个JTAG接口; ( 5)三个可编程计时器。别的, PowerPC 405硬核还具有如下特色: ( 1)支撑硬件乘法和除法; ( 2) 32个32位通用寄存器; ( 3) 16KB两路组相联办法指令缓存( set-associave) ; (4) 16KB两路组相联办法数据缓存、写回/写直达; ( 5 ) 完结PowerPC用户指令集架构(U ISA) ; ( 6)专用的片上存储器接口(OCM) ; ( 7 )支撑IBM CoreConnect总线架构。

CoreConnect总线架构是由IBM开发的一种片上总线通讯衔接技能。CoreConnect总线包含处理器部分总线( PLB) 、片上外设总线(OPB)和设备操控寄存器总线(DCR) 。PLB总线为主设备和从设备之间供给高带宽、低推迟的衔接,OPB总线为衔接具有不同总线宽度和时序要求的外设供给了一条途径,削减了对PLB功用的影响,DCR总线用来操控PowerPC405处理器中的通用寄存器和设备寄存器之间的数据传输。

2 依据SoPC的嵌入式体系规划技能2. 1 渠道技能

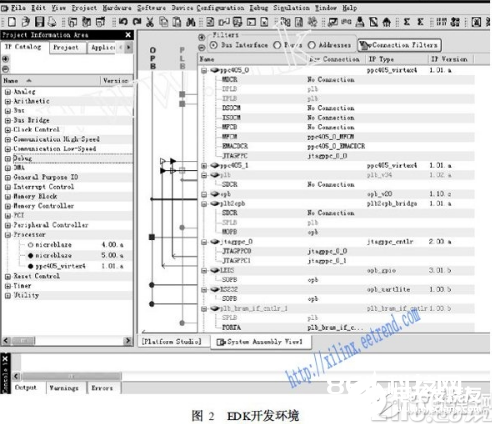

在渠道的根底上来构建嵌入式体系为规划者供给了极大的便当, Xilinx 推出的嵌入式开发东西包( EDK)集成了比如硬件渠道发生器(platgen) 、硬件仿真模型发生器( SimGen) 、软件渠道发生器( libgen) 、运用软件编译东西(GNU Compiler) 、软件调试东西(GNU Debugger) 等一系列东西。规划者能够经过集成在EDK环境下的Xilinx渠道作业室(XPS)便当的调用各种东西进行依据SoPC的嵌入式体系规划。EDK环境下为体系规划者供给了丰厚的IP资源,可使用现有的资源敏捷建立自己的嵌入式体系,完结整个PowerPC体系硬件的开发。假如开发东西包供给的IP库不能满意体系规划者的需求,规划者也可定制自己的IP。图2所示为EDK开发环境图形界面。

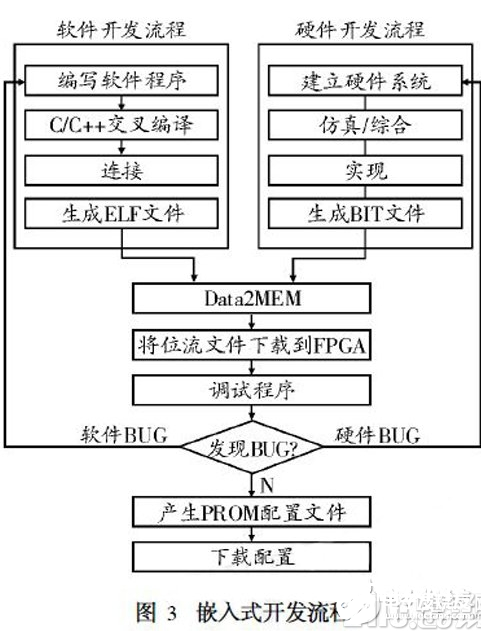

EDK环境为其自带的IP供给了相应的驱动程序及相关的函数,规划者能够经过调用这些函数加速运用程序的开发。关于规划者自行研发的IP,则需求编写相应的驱动程序。运用程序编写完结后,调用EDK下的GNU东西,编译衔接生成可履行文件,再将硬件、软件文件结合在一同,发生可下载的位流文件下载到FPGA,运用Xilinx 微处理器调试东西(XMD ) 衔接GNU调试东西进行运用程序调试,在承认运用程序正确无误,能完结体系功用之后,即可将位流文件转换成PROM的装备文件(MCS文件) 下载到方针板上的PROM,然后完结整个规划开发。图3为使用EDK东西进行嵌入式体系开发的流程。

2. 2 体系架构及硬件规划

依据SoPC的嵌入式体系规划过程中,体系规划者首要要清晰规划需求,这关于整个规划具有指导性效果,也是将来规划完结后查验规划是否可用的规范之一。体系规划者依据规划需求来确认其体系架构,界说体系首要模块组成,决议其接口类型、总线结构、硬件功用及软件功用,齐备的体系架构界说要能满意根本的规划需求,并能最大极限的进步体系全体功用。

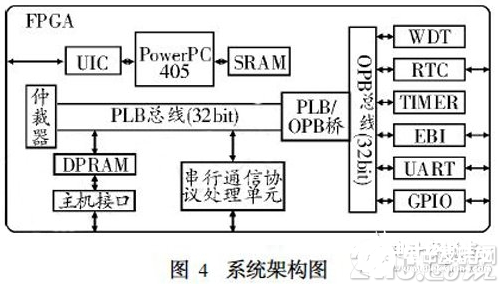

依据SoPC的多路传输数据总线接口的规划需求是在板级多路传输数据总线接口模块的根底上提出的,经过对板级器材的IP化,将原有板上芯片以IP的办法集成到FPGA中,用单片集成电路完结原板级电路的规划。依据板级多路传输数据总线接口模块的体系结构,提出了如图4所示的依据SoPC的嵌入式体系架构图,该嵌入式体系集成了PowerPC405处理器、串行通讯总线协议处理器,具有实时时钟(RTC) 、看门狗(WDT) 、计时器( TIMER)功用,可完结GJB289A-97(数字式时分制指令/呼应型多路传输数据总线)中规则的RT/BC功用,支撑完结ISBC协议(改善的静态总线操控协议) ,经过办法挑选别离支撑LBE总线拜访、VME总线拜访、PC I总线拜访(经过PLX9054 桥接器) 、PCI-Express总线拜访(经过PEX8311桥接器)四

种主机接口拜访办法。

硬件规划过程中,体系规划者在XPS图形界面下调用现成的IP库,建立SoPC的硬件环境,经过硬件渠道发生器(p latgen)生成硬件文件,其间PowerPC405处理器、双口存储器、SRAM、串行通讯总线协议处理单元挂接在PLB总线上;实时时钟(RTC) 、看门狗(WDT) 、计时器(TIMER) 、外部总线接口( EB I) 、通用输入输出接口( GPIO) 、串口操控器(UART)挂接在OPB 总线上;通用中止操控器(UIC) 、裁定器和PLB /OPB 桥的寄存器经过DCR总线拜访。硬件架构建立起后经过硬件仿真模型发生器( SimGen)对硬件的功用进行仿真。

2. 3 软件规划

依据SoPC的嵌入式体系软件规划过程中,软件规划者要清晰嵌入式体系的相关硬件装备,比如内存地址映射联系,硬件寄存器装备等,这将决议开宣布的嵌入式软件是否具有实用性。嵌入式软件的规划一般包含CPU发动代码,体系初始化代码,硬件自测验程序,设备驱动程序,实时操作体系及运用软件等,依据不同的体系需求,软件包含的内容稍有差异。软件规划阶段,规划者将挑选出编译和调试东西并完结编程。

依据SoPC的多路传输数据总线接口的软件由初始化程序、自测验程序、BC /RT操控程序组成。依据SoPC的嵌入式软件开发是在EDK环境下选用C言语编程完结的,经过软件渠道发生器( libgen) 、运用软件编译东西(GNU Compiler)编译衔接得到可履行文件,该文件可与生成的硬件位流文件经过JTAG接口一同下载到FPGA 运转,也可先将位流文件固化到外部PROM中,运用软件的可履行文件转换成二进制文件固化到外部FLASH中,体系上电后主动加载硬件逻辑并将运用软件搬迁到SRAM运转。各部分软件完结如下的功用:初始化程序完结CPU初始化及相关功用单元的初始化;自测验程序完结体系的上电自测验和内部自检; BC /RT操控程序完结该嵌入式体系作为BC或RT时的数据传输操控。依据SoPC的嵌入式体系硬件规划和软件规划能够并行展开,使用软硬件协同规划的思维,可加速整个嵌入式规划的速度。

2. 4 测验验证

依据SoPC的嵌入式体系规划的测验验证用来保证体系不存在软件和硬件上的缺点。软件测验验证旨在经过履行软件并调查其行为是否满意规划要求,而硬件测验验证则包含了保证硬件能够对外在的鼓励作出正确的呼应并能正确的履行软件。

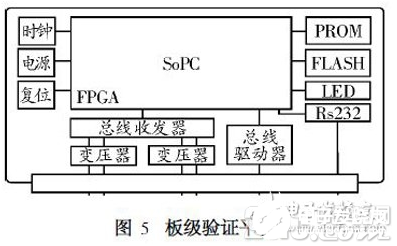

依据SoPC的多路传输数据总线接口中杂乱的软硬件结构及其品种繁复的IP资源,使得该体系的测验验证作业也变得杂乱。在测验验证过程中,选用多级测验验证技能,首要对各单一模块进行仿真测验,进行软硬件协同验证,再经过集成各个功用模块进行体系集成验证,最终进行板级验证。在进行体系各模块功用验证时,软件能够作为硬件测验的信号源,针对各个模块都编写相应的C言语测验向量,进行功用覆盖率测验。在单一功用模块验证测验的根底上,将各模块集成为一个完好的体系,对整个体系进行集成测验。进行板级验证时,能够运转更为完好、更挨近实践运用的C程序测验向量,使得测验更全面、更牢靠。图5所示为板级验证渠道示意图。

3 结束语

本文经过对Xilinx公司Virtex-4 FX系列FPGA的介绍,剖析了其内嵌的PowerPC405处理器的体系结构及CoreConnect总线的特色,经过依据SoPC的多路传输数据总线接口的硬、软件规划技能和验证技能的介绍,更好地论述了依据SoPC的嵌入式体系规划办法。在依据SoPC的嵌入式体系规划中,经过单片FPGA完结多片专用芯片的功用,削减器材数目,缩小体系面积,添加体系牢靠性,达到了对板级多路传输数据总线接口模块小型化、集成化的意图。依据SoPC的嵌入式体系规划以其数据处理速度快、集成度高、开发周期短、运用灵敏便当等特色,信任在航空航天范畴将会得到广泛的运用。