引 言

自单片机引进我国以来,相关产品的遍及促进单片机的运用规划日益广泛。传统的单片机操控体系由单片机以及外围扩展芯片组成,可是这些外,围芯片一般具有接线重复性高、体积大等缺陷。可编程逻辑宏单元或逻辑块之间的彼此连线在同一封装内,受外界搅扰影响小,电磁兼容(EMC)性能好。对规划者来说,CPLD器材最大的长处在于可现场编程,改动逻辑关系时,无需更改外部线路板,只需用图形言语程序或硬件描绘言语程序来改动电路,生成下载修正软件,通过下载电缆输入CPLD器材即可,十分便利,特别有利于新品试制,大大缩短了开发周期。运用CPLD和单片机结合构成其外围电路能够削减体系芯片数量,缩小体系体积,进步体系可靠性。

1、操控体系

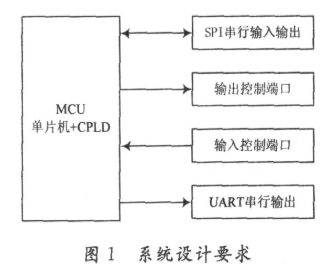

该体系是一个无线传感器网络节点的操控体系,它用于操控无线模块接纳主站发送过来的信息,单片机读取这些数据并译码后,依据译码成果操控各功用子模块,如无线模块操控、温度收集操控、电源办理操控、时刻一致信号操控等功用,共需求28个输出操控I/O口,13个输入操控I/O口,扩展I/O端口分配8个。各外围模块通过SPI串行规范接口的扩展与单片机和CPLD进行通讯,并完结数据传输操控功用。各外围模块只需承受MCU的操控指令,即可独立完结外围模块各自的功用:无线模块的收发、数据收集A/D转化、时刻一致记载、电源办理等。一起预留单片机通过USART的串口输出,别的,还需求此体系具有很好的扩展性,通过扩展外围模块来添加节点不同的功用。体系规划要求如图1所示。

依据规划要求,单片机体系要8 b的UART串行输出以及SPI串行输入输出,一起为了完结各种操控功用,单片机有必要至少扩展7个I/O端口。假如运用传统的扩展办法,在输出速率要求不高的情况下,并行接口一般运用8255传统的微处理器接口芯片来扩展。

可是,这些芯片都是40脚DIP封装,体积巨大,并且每片最多只能扩展3个8 b I/O端口,还要考虑8255中A,B,C口是作为输进口仍是输出口。当需求的操控端口较多时,不得不必多个这种专用芯片。这时需重复衔接多片8255的8位数据线、单片机读/写信号线、ALE,CS(片选)和A0,A1信号线,添加了单片机硬件、软件的规划难度,也就形成电路杂乱、操控不便利、可靠性下降,并且增大了电路的功耗、体积和分量。一起接口芯片供给的端口数未必与实践需求的端口数持平,不能依据实践情况分配I/O端口的数量,简单形成芯片部分资源的糟蹋。而CPLD具有丰厚的可编程I/O引脚,并且因为其在体系可编程的特色,规划者能够自己界说器材的内部逻辑和管脚,扩展电路也具有可编程规划的特色,便利电路的屡次改善,下降了规划本钱。

2、单片机与CPLD

AVR单片机,选用精简指令集CPU(RISC),具有高性能,处理速度快(1 MIPS/MHz),本钱低,包括FLASH程序存储器、看门狗、E2PROM、同/异步串口、SPI、ADC、定时器/计数器,很多的中止体系,集成多种功用,具有低功耗抗搅扰的休眠形式。

杂乱可编程逻辑器材(Complex Programmable Logic Device,CPLD)是一种半定制的专用集成电路(Application Specific Integrated Circuit,ASIC)。其芯片上按必定摆放办法集成了很多的门和触发器等根本逻辑元件。通过软件编程能够完结这些元件的衔接,然后使之完结某个逻辑电路或体系的功用,成为一个可在实践电子体系中运用的ASIC。

现在,最大的两家CPLD/FPGA出产厂商分别是ALTERA以及Xilinx。该体系运用的Xilinx的XC2C256归于XiIinx公司的Coolrunner2系列,包括256个宏单元,最大用户I/O管脚有100个。

3、体系硬件衔接组成以及作业进程

运用CPLD替代单片机的外围接口芯片,与AVR单片机构成的操控体系相连如图2所示。体系的首要部分仅需求2片集成电路,AVR单片机系列AT—megal62和XC2C256。单片机与CPLD之间的接口是通过单片机的地址/数据复用总线(PORTA端口)以及读写操控I/O口(WR,RD,ALE)与CPLD的I/O口相连来进行数据、状况的传输。

在单片机中对扩展的I/O端口进行一致编址,通过C言语能够便利地拜访I/O端口,单片机要往数据端口或操控端口输出信息,有必要先把地址送到地址总线上,将确认的操控信息送到操控总线上,再把数据信息送到数据总线上。通过CPLD的内部逻辑进行地址、数据锁存,并译码以取得扩展的端口号,然后取得对各个外部功用子模块的操控信号,端口号COM1,COM2,COM3。COM4,COM5,COM6,COM7分别是无线模块操控、时刻一致操控、数据收集操控、电源办理操控、片选挑选操控、状况挑选以及可扩展模块操控等的操控端口,并且通过操控片选端口号(COM5端口),能够对各个功用子模块进行SPI串行数据的传输,然后到达对SPI串行规范接口的扩展。

通过挑选不同的I/O端口能够操控读取、写入各外围处理模块的数据。要读取某一外围处理模块的数据,有必要先读取状况挑选端口COM6的状况信息,状况挑选RDY(数据准备好)安排妥当时,通过向此处理模块操控端口COM写入操控信息来操控子模块的作业形式,再通过写片选端口COM5来挑选子模块,然后发动SPI完结读取子模块的数据。与此对应,写入数据也需求读取状况信息,再操控某一子模块的作业形式,挑选片选信号,发动SPI写,就能够完结写入数据的功用。

4、CPLD软件规划

选用Xilinx公司的CPLD开发软件Xilinx ISE完结体系的软件规划,Xilinx ISE支撑原理图输入、HDL言语输入、状况图输入和混合输入等输入办法。其间HDL言语中的VHDL硬件描绘言语,与详细的工艺技术和器材无关,易于同享和复用,具有多层次描绘体系硬件功用的才干。

在规划中,CPLD需求完结的功用为地址译码端口以及操控不同端口的电路规划,用VHDL言语对进行编程编译,然后选用元件例化的办法得到电路结构如图3所示。

CPLD中所规划的程序片断:

地址译码端口以及不同端口完结的功用仿真成果如图4所示。能够看出,仿真成果契合规划要求。

5、单片机软件规划

AVR单片机固化程序选用ICC言语编写,并运用模块化的规划办法,分为初始化程序、预界说子程序、主程序、无线收发操控程序、各功用模块操控程序、读功用子模块的子程序、装备功用子模块程序、超时程序等。模块化规划使软件愈加灵敏,便于调用和移植,并且在过错产生的时分,能够很快找到过错,极大地进步了体系的可靠性和稳定性。

单片机中要对扩展的不同I/O端口分配相对应的不同的内存地址。例如:要对扩展的电源办理I/O端口分配单片机所映射的内存地址为Ox2000。能够写成:#deftne POWER ADDR (*(unsigned char*)0x2000)。

单片机首要完结体系的操控功用,在完结输出操控接口时需求与CPLD合作,供给CPLD需求的数据和地址及操控线。当需求某一组输出作业时,在单片机顶用C言语对宏变量对应的地址进行赋值,“WR”或“RD”一起就被拉低,CPLD通过这组信号判别挑选并且使能某一组输出作业,并将输出操控代码从单片机通过CPLD的相应端口输出,完结操控功用。例如对电源办理单片机中界说的I/O端口对应的内存地址为:#define POWER_ADDR(*(unsigned char*)Ox2000),当用C言语写下POWER_ADDR=Oxl2时,就会在CPLD的8个I/O口输出相应的操控信息“00010010”,然后对各功用模块进行供电或断电。

6、结 语

选用CPLD作为单片机I/O端口的扩展芯片,大大削减了单片机外围所用芯片的品种和数量,缩小了体积,下降了功耗,进步了体系的可靠性和整体性。运用单片机和CPLD结合能够有效地完结曩昔需求使用单片机和很多外围接口芯片才干完结的功用,并且还能够依据需求不断地扩展外围电路,只需求修正CPLD的程序就能够完结用户的需求。CPLD器材与单片机结合,能够优势互补,组成灵敏的、硬软件都可现场编程的操控器,缩短开发周期,习惯市场需求。

责任修正:gt