传统上,模仿IC规划工程师都是通过进步电源电压和作业电流来进步设备的运转速度和动态规模,但在动力功率认识愈强的今日这一办法已很难到达最佳的作用。如今,规划者不只寻求更高的作业频率、可用带宽、噪声功用和动态规模,还要一起确保设备的功耗不变乃至更低。

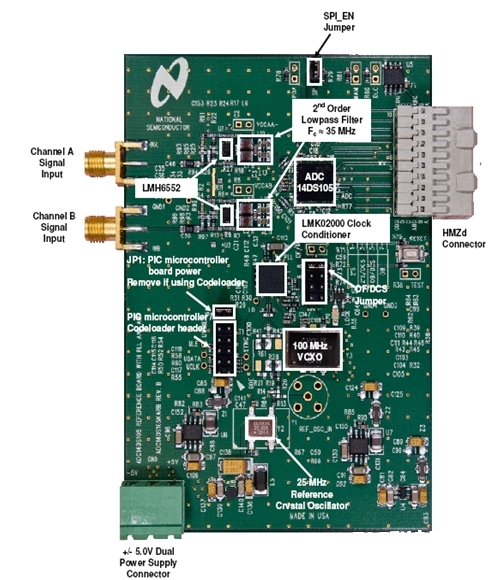

美国国家半导体公司的PowerWise产品选用立异的架构和抢先的制造工艺,不光功用微弱并且功耗极低。本文将通过选用图1中的参阅规划渠道来展现怎么运用高动力功率的模/数转化器(ADC)、全差分放大器和时钟调整电路来开发一个完好的模仿体系。首要,咱们先从PowerWise 品牌背面的技能内在谈起。

图1. 完好的参阅规划电路板,傍边包含有ADC、全差分放大器和时钟调整器电路。

为特定组件度身订造的工艺技能

用来开发模/数转化器(ADC)的工艺技能并不一定适宜用来开发高频的低噪声放大器。事实上,半导体公司一般都会运用几种不同的工艺技能,例如CMOS、BiCMOS和SiGe等。而运用哪一种工艺则取决于组件的要求。假如没有优异的工艺技能相合作,再完美的电路规划也是有缺憾的。

不同于其他大多数的半导体供货商,美国国家半导体选用纯CMOS技能去规划大部分最新的ADC。今日,CMOS技能可谓无处不在,原因是CMOS的逻辑门没有任何的静态功耗,但具有较高的驱动电流和速度。考虑到ADC内包含有很多的数字电路,因而用纯CMOS技能去完成电路规划便可完成比BiCMOS更低的功耗。数字CMOS门电路在直流形式下不会耗费电流,但双极的门电路即便在直流形式下都需耗费电流,因为电路需求偏置电流来保持功用参数。成果,芯片中的数字部份会耗费较多的电流,然后进步全体的功耗。

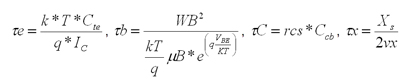

美国国家半导体特别开宣布VIP 10工艺来合作放大器电路的规划。VIP 10是一种高速、介质隔离的互补双极电路工艺,它在一片键合晶圆(bonded wafer)上选用深槽技能完成彻底的介质隔离以及优化的高速放大器功用。键合晶圆选用的深槽技能可尽量下降寄生电容,优化功率/带宽功用、下降失真并使裸片的体积更小。选用高功用NPN和PNP晶体管的互补双极晶体管规划可认为如今的高速放大器带来最优的功用组合,包含高带宽、低功耗、低电源电压、大输出摆幅、高输出电流和低失真。关于双极晶体管来说,最常用的AC质量要素是过渡频率(FT),在这频率下共发射极电流增益下降到单位级。在VCE=5V下,VIP 10 NPN和PNP的FT分别为9GHz和8GHz,大约比同类竞赛的工艺高出50%。晶体管的高FT意味着在既定作业点下其发射极-基极分散电容值会很低。合作VIP 10晶体管,美国国家半导体能够规划出带宽超越1GHz 或带宽在100MHz 规模以内的放大器,并且其功耗能够十分低。因为分散和寄生电容一起被大幅减少后,内部级在很低的作业电流下也会呈现低相位位移。关于某些双极工艺来说,FT能够在较低电压下大幅地下降,但若选用VIP 10工艺,那即便Vce=1V,FT都可保持在高水平:NPN可达7GHz而PNP可达5GHz。下面的公式1表示出一个双极晶体管的过渡频率是怎么计算出来。

其间:

k是玻尔滋曼常数、T是绝对温度、Cte 是发射极电容、q是电子的单位电荷、IC 是集电极电流、WB是基带带宽、μB是电子移动性、rcs是集电极电阻、Ccb 是集电极电容、Xs 是集电极空间电荷区的宽度,而vx则是集电极空间电荷区的饱满速度。

立异的技能

上文中咱们已讨论过IC规划者知晓了最优的电路规划办法、专利架构和顶级的工艺技能就根本掌控了到业界最先进的技能,然后能够在竞赛剧烈的商场中开宣布异乎寻常的产品。要进一步稳固竞赛优势,规划者还必须紧随业界开展的潮流,比如美国国家半导体的PowerWise等立异技能。PowerWise技能能够使数字处理器(例如DSP或FPGA)中的DSP或FPGA功耗下降70%。

PowerWise选用自适应电压调整(AVS)和阈值调整技能能够在保持体系最低开支的情况下主动将数字逻辑电路中的作业电路和漏电功耗减到最低。PowerWise技能在业界是绝无仅有的,它是仅有一种可供一切电路开发商运用的先进体系级动力办理计划,不光内容齐备并且还可供应具体的常识产权信息。通过运用简略的规范硬件接口,加上业界闻名合作伙伴ARM、TSMC、UMC、Synopsys等支撑,这项技能可运用到任何CMOS工艺,并且规划东西和流程都已规范化,可合作任何的操作体系或运用,完成最优的动力功率。

树立一个完好的模仿体系

规划参阅可认为规划工程师供应了规划模版,其重要性显而易见。特别是要求在不添加功耗的前提下进步体系功用时,规划参阅就显得更为重要了。大多数扎手的规划问题,例如挑选正确的组件、组件安置、体系布局和布线等,都可在这些规划参阅中找到答案。依据服务客户创立的高功用模仿体系的常识堆集,美国国家半导体树立起了一个会聚创作的规划参阅库。以最新参加参阅库的ADC14DS105KARB参阅规划为例,它选用了最新的PowerWise 宗族LMH6552 1.5GHz差分驱动器作为信号链的一部份。该组件与高速的ADC14DS105数据转化器和守时计划结合在一起,为丈量外表的规划者供应一个杰出的参阅东西。

ADC14DS105KARB接收器参阅规划板

ADC14DS105KARB是一个近零中频接收器参阅规划板,它所运用的组件如下:两个LMH6552 1.5GHz 带宽差分电流反应放大器;ADC14DS105 带有LVDS输出的14位、1GHz、双路、105MSPS模/数转化器;LMK02000低颤动精细时钟调整器,它带有一个可在100Hz到20MHz带宽规模内供应128fs颤动的集成锁相环路(PLL);数个高动力功率的电源办理电路。

ADC14DS105KARB (其框图见图2)是一块中频接收器子体系参阅规划板,它选用一对LMH6552差分驱动器和一个双路ADC,能够当即测验适用于直流电至40MHz信号频率的正交直接转化或近零中频接收器。这个接收器架构现已被广泛运用到WiMAX 和WCDMA接收器体系。

图2. 参阅规划板的框图。

因为ADC的输入带宽高达1GHz,而差分放大器增益级的带宽高达1.5GHz,因而若输入信号不超越40MHz,大信号的信噪比可达 73.3满刻度分贝值(dBFS),而无杂散信号动态规模(SFDR)则超越85dBFS。这款电路板除了选用LMH6552之外,还安装了美国国家半导体的14位、 105MSPS、低失真、低噪声、并可输出串行LVDS数据的双通道模仿/数字转化器ADC14DS105、低颤动时钟调整器LMK02000以及多颗高能效的电源办理IC。

LMH6552是一个高功用全差分放大器,它能供应驱动14位高速数据收集体系所需的超强信号保真度和宽广的大信号带宽。通过选用取得专利的差分电流形式输入级架构,LMH6552能够在不献身呼应平整度、带宽、谐波失真或输出噪声功用下,在增益大于一个单位级下作业。

合作外置的增益设置电阻器和集成式的共模反应, LMH6552可被装备成一个差分输入到差分输出,或信号单端输入到差分输出的增益级。LMH6552的输入端可作沟通耦合或直流耦合,因而能够运用到比如通讯体系及高速示波器的前端电路等十分广泛的范畴。

LMH6552的电流反应拓扑使器材即便在高增益下,只需挑选适宜的反应电阻(RF1, RF2),便可供应有超强增益平整度和噪声功用的增益和带宽独立性。在大多数的运用中,RF1都被设置成等于RF2,因而增益是由RF/RG的份额来决议。

LMH6512的数据表依据各式各样的增益给出最优的反应电阻器数值。无论是过大或过小的RF都会对稳定性构成影响。在答应的情况下,反应电阻器还能够调整频率呼应。

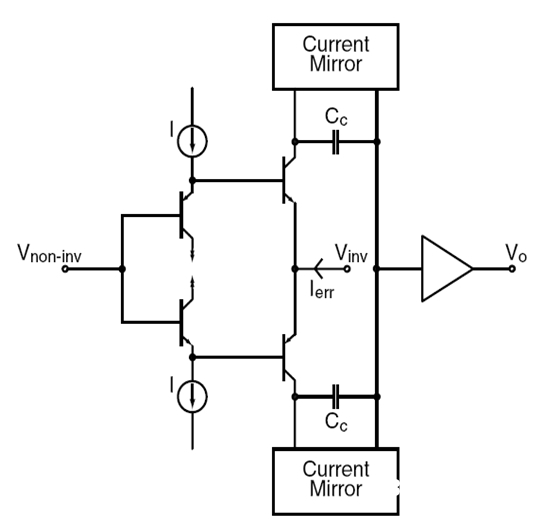

电流反应放大器的另一长处是需求内部增益级相对较低。一般一个电流反应放大器首要包含有一个输入缓冲器、一个增益级和一个输出缓冲器。具有较少的增益级意味着通过开环电路的推迟会较少,然后在相同的功耗下能取得较大的带宽。

图3. 根本的电流反应(CFB)拓扑。

图3中的根本电流反应(CFB)拓扑是一个单级放大器。电路中的仅有高阻抗节点是在输出缓冲器的输入。VFB放大器一般需求两个或以上的增益级才干取得满足的开环增益,这些附加的增益级不单会添加推迟,并且还会下降带宽的稳定性。

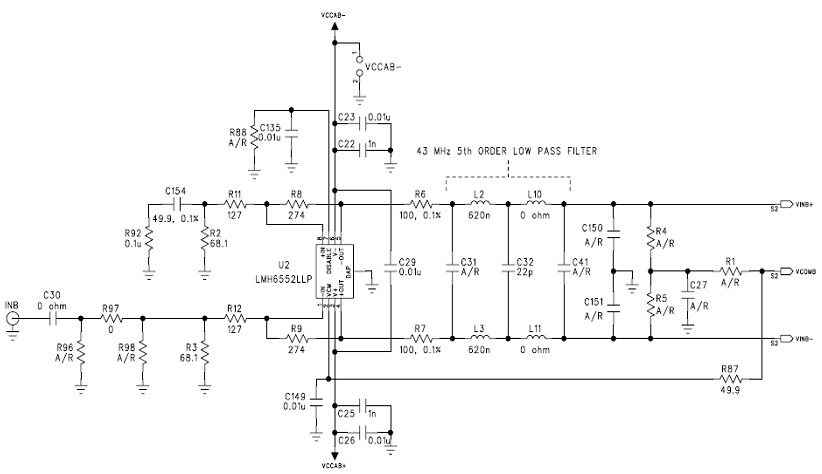

图4. LMH6552电路和5阶低通滤波器。

图4说明晰放大器的参阅电路板装备。傍边的输入是50Ω和直流耦合。LMH6552被装备成单端到差分形式转化,而ADC14DS105的VCOM输出会用作放大器的共模输入。每一个放大器都被装备成有6分贝的增益,因而最大的输入信号电平为1Vp-p,并在放大器的输出处发生出2Vp-p。这儿主张放大器最好由一个双电源轨来供电(+/- 5VDC)。在VCCAA- 和VCCAB-处设置跳线,电路板就可在单电源形式下作业,具体信息可参阅LMH6552数据表中有关LMH6552单电源作业的部分。要取得最佳的失真功用(最佳SFDR),主张选用一个低噪声信号发生器来驱动评价板的信号输入,而信号发生器的输出应该通过带通滤波以按捺由信号发生器引进的谐波失真,以及容许进行准确的噪声和失真功用丈量。但是,跟随在LMH6552之后的43MHz的5阶低通滤波器可过滤信号发生器的宽带噪声,然后进一步改进ADC的噪声功用。滤波器输出会被模/数转化器采样。

ADC14DS105是世上第一款带有串行化LVDS输出的14位高速、1GHz FPBW的双路模/数转化器,它选用串行化LVDS输出大幅地减少了需求跨过电路板或在电路板之间的导线数量,因而大大地简化电路板的布局。

用来替模仿输入采样的ADC时钟信号是由一个经LMK02000精细时钟调整器操控的VCOX所发生。该LMK02000为用户供应一个设有时钟分配区的超低噪声锁相环路(PLL),它可供应5个LVPECL输出和3个LVDS输出(全为差分)。

每一条在LMK02000上的时钟输出通道均包含有一个分频器模块和推迟调整时钟。LMK02000一般都会跟一个低颤动的VCOX衔接在一起。在这种情况下,一个Crystek 类型的CVHD-950X-100.0可供应一个单端CMOS时钟信号来驱动ADC的时钟输入。LMK02000 的锁相环路可把这个VCOX确定到一个25MHz的参阅振荡器(Connor-Winfield 类型CWX823),而LMK02000的锁相环路计数器、相位检测器和电荷泵是选用PIC微操控器电路板来编程的,详情请参看用户攻略。

LMK02000的RMS信号颤动仅为128fs(输入的时钟规模由100Hz到20MHz)。图5表示出时钟的相位噪声功用,该功用值是在LMK02000的CLKout4情况下丈量出的。从VCOX发生出来的单端时钟信号会供应ADC14DS105的CLK输入。

图5. LMK02000的相位噪声功用。

LMK02000精细时钟调整器将多种功用结合在一起,包含颤动铲除/从头调整、倍频和参阅时钟分配。该器材集成了一个高功用的整数-N锁相环路(PLL)、一个部分集成,环路滤波器、三个LVDS输出和5个LVPECL时钟输出分配模块。

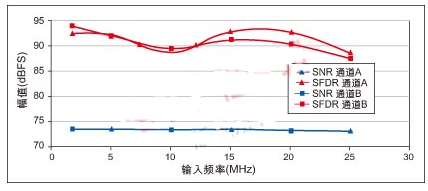

图6. 典型SFDR和SNR功用与输入频率的联系。

图6所示为差分放大器、带通滤波器和ADC的结合通道呼应。请注意图中最佳的动态功用和通道间的匹配性。

责任编辑:gt