简介

在“ 为工业4.0启用牢靠的根据状况的有线监控 — 第1部分 ”一文中,咱们介绍了ADI公司的有线接口解决计划,该计划协助客户缩短规划周期和测验时刻,让工业CbM解决计划更快地进入市场。本文探讨了多个方面,包含挑选适宜的MEMS加速度计和物理层,以及EMC功能和电源规划。此外,还包含榜首部分介绍的三种规划解决计划和功能权衡。本文为第二部分,侧重介绍榜首部分展现的SPI至RS-485/RS-422规划解决计划的物理层规划考量。

为MEMS完成有线物理层接口的常见应战包含办理EMC牢靠性和数据完整性。可是,在RS-485/RS-422长电缆上散布SPI之类的时钟同步接口,一起在相同的双绞线(虚伪电源)上布置电源和数据时,会带来更多应战。本文评论以下关键问题,并就物理层接口规划供给主张:

◆ 办理体系时刻同步

◆ 引荐的数据速率与电缆长度

◆ 适用于共用电源和数据架构的滤波器规划和仿真

◆ 虚伪电源结构中的无源元件功能权衡

◆ 元件挑选和体系规划窗口

◆ 试验性丈量

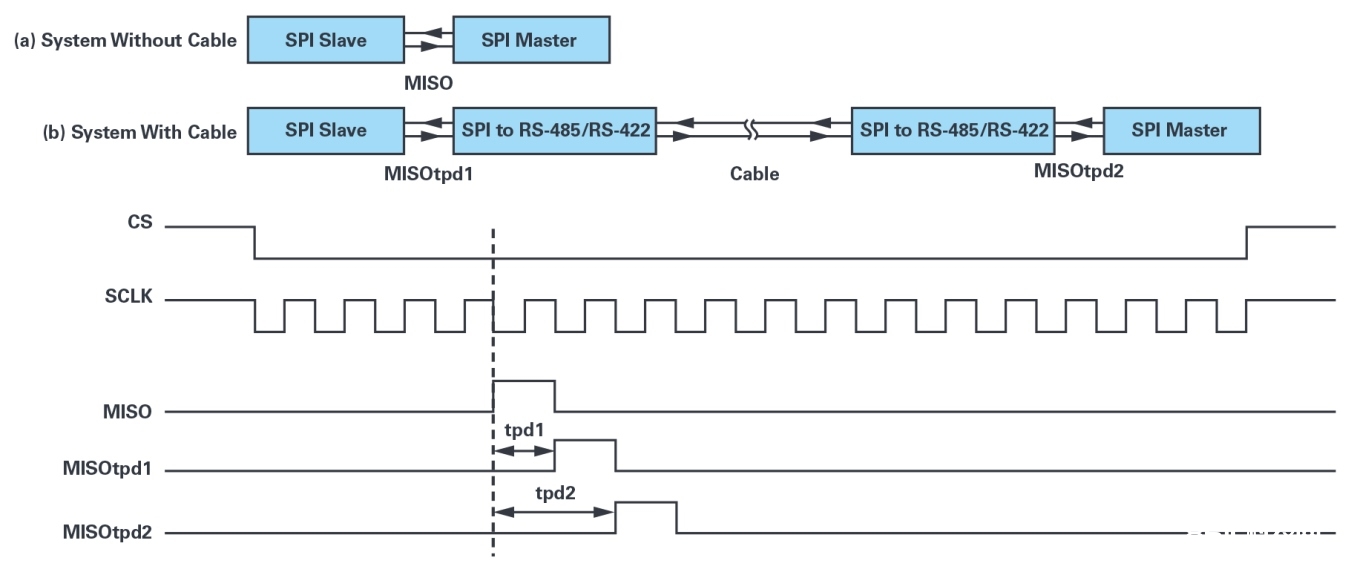

图1.选用与不选用RS-485/RS-422长电缆的体系的MISO数据和SPI SCLK同步。

时刻同步和电缆长度

规划SPI至RS-485/RS-422链路时,电缆和元件会影响体系时钟和数据同步。在长电缆中传输时,SCLK信号会在电缆中产生传达推迟,100米长的电缆会推迟约400ns到500 ns。关于MOSI数据传输,MOSI和SCLK会被电缆推迟平等时刻。可是,从从机MISO发送到主机的数据会呈现两倍传达推迟,因此不再与SCLK同步。或许的最大SPI SCLK根据体系传达推迟设置,包含电缆传达推迟,以及主机和从机元件传达推迟。

图1展现体系传达推迟怎么导致SPI主机上呈现不精确的SPI MISO采样。关于没有选用RS-485/RS-422电缆的体系,MISO数据和SPI SCLK会以低推迟或无推迟同步。关于选用了电缆的体系,SPI从机上的MISO数据与SPI SCLK之间存在一个体系传达推迟,如图1中的tpd1所示。回到主机的MISO数据存在两个体系传达推迟,如tpd2所示。当数据由于电缆和元件传达推迟而右移时,会产生不精确的数据采样。

为了避免呈现不精确的MISO采样,能够缩短电缆长度、下降SPI SCLK,或许在主控制器中施行SPI SCLK补偿计划(时钟相位偏移)。理论上,体系传达推迟应该小于SCLK时钟周期的50%,以完成无错通讯;在实践中,能够将体系推迟限值确认为SCLK的40%,这能够作为一般规矩。

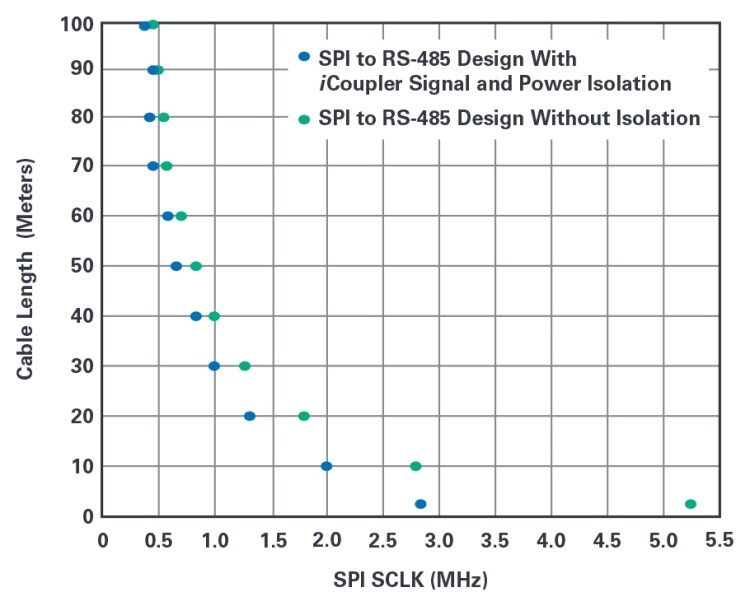

图2针对1.1部分中描绘的两个SPI至RS-485/RS-422规划供给SPI SCLK和电缆长度攻略。这种非阻隔规划运用了ADI公司具有高速EMC稳健性的小型RS-485/RS-422器材( ADM3066E 和 ADM4168E )。这种阻隔规划还选用了ADI公司的iCoupler®信号和电源阻隔 ADuM5401 器材,能够为SPI至RS-485/RS-422链路供给更高的EMC稳健性和抗噪声搅扰功能。这种规划会添加体系传达推迟,导致不可在更高的SPI SCLK速率下运转。在更长的电缆(超越30米)中传输时,强烈主张添加阻隔,以协助消除接地回路和EMC事情的影响,例如静电放电(ESD)、电快速瞬变脉冲群(EFT),以及与数据传输电缆耦合的高压浪涌。当电缆长度到达或超越30米时,阻隔和非阻隔规划的SPI SCLK和电缆长度功能类似,如图2所示。

图2.针对阻隔和非阻隔规划的SPI SCLK和电缆长度攻略。

虚伪电源

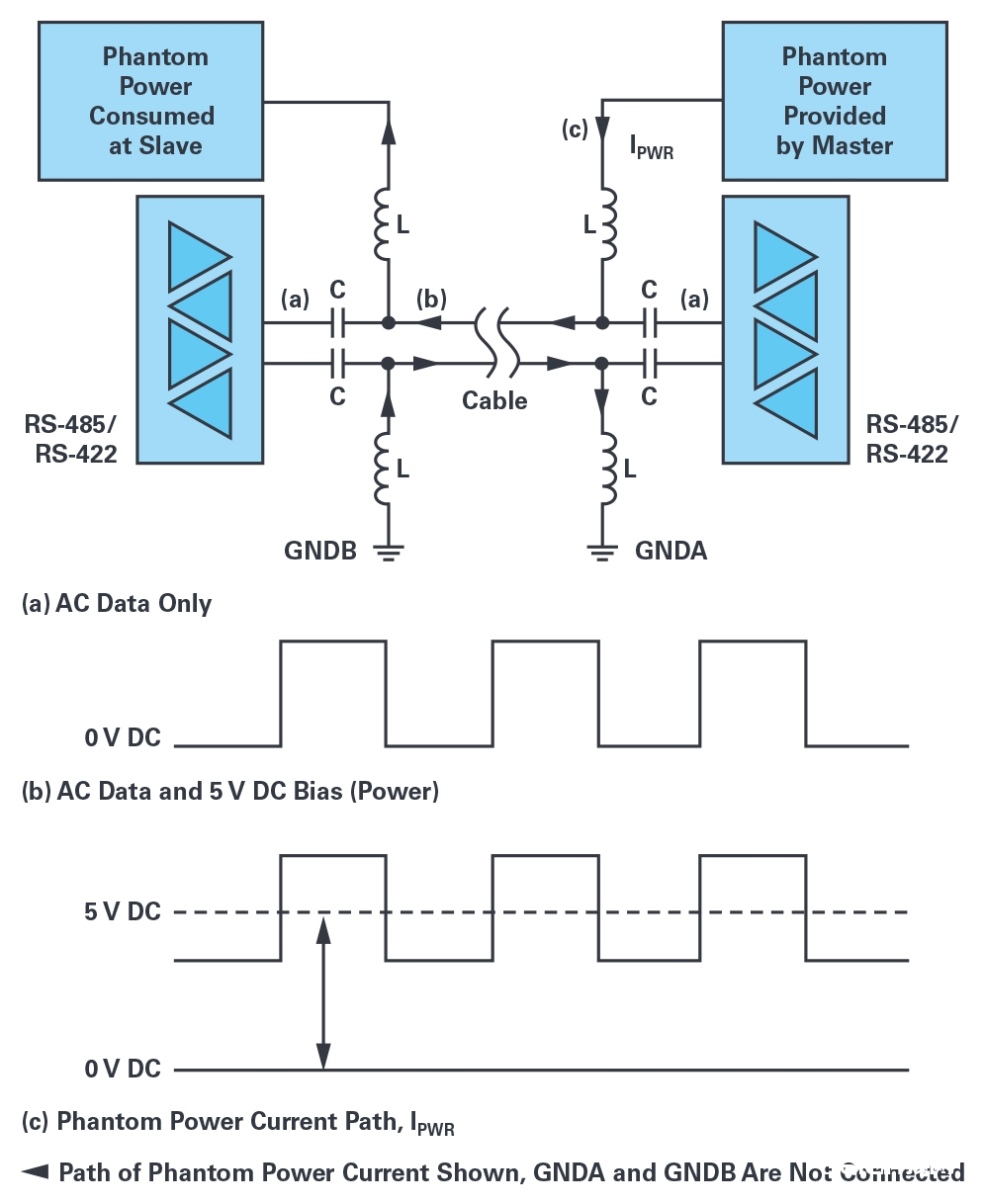

图3.虚伪电源物理层的沟通和直流电压电平。

布景常识

虚伪电源将电源和数据布置在一根双绞线上,在主机和从机之间完成单电缆解决计划。将数据和电源布置在同一根电缆上,能够在空间有限的边际传感器节点上完成单衔接器解决计划。

电源和数据经过电感电容网络散布在单根双绞线上,详细如图3所示。高频数据经过串联电容与数据线路耦合,能够维护RS-485/RS-422收发器免受直流总线电压影响,如图3a所示。图3所示为经过衔接至数据线路的电感衔接至主机控制器的电源。如图3b所示,5V直流电源对沟通数据总线施行偏置。在图3c中,电流途径显现为从机和主机之间的IPWR,运用电缆远端根据状况监控(CbM)的从机传感器节点上电感从线路中获取电源。

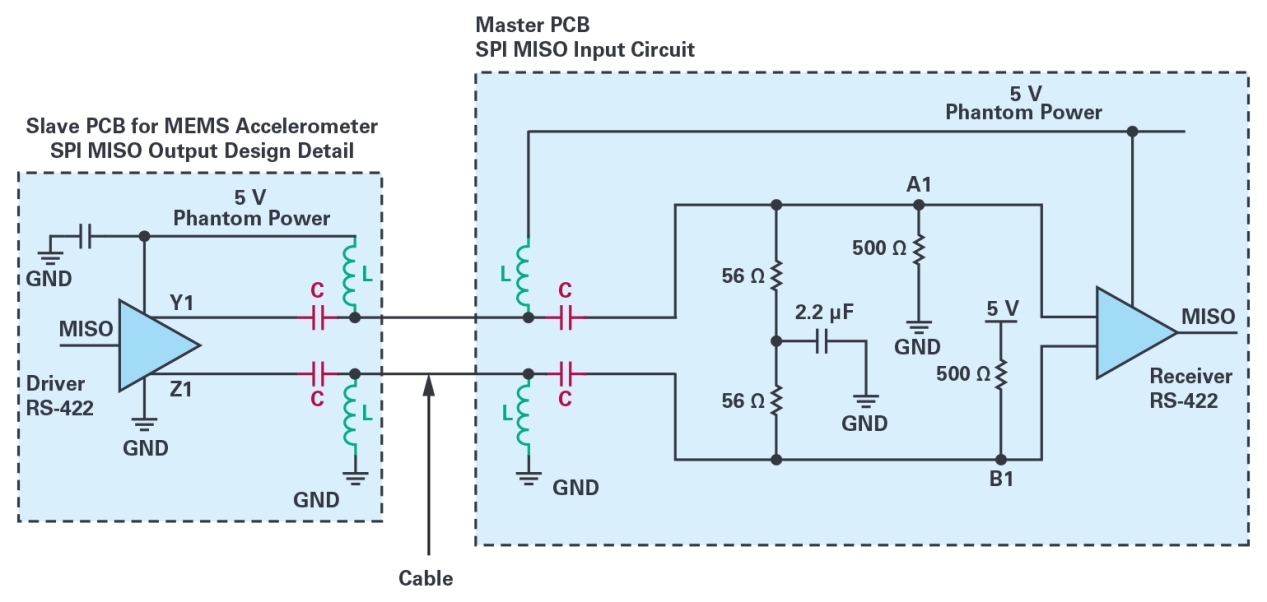

图4.SPI至RS-485/RS-422规划和虚伪电源滤波器电路。

高通滤波器

在本文中,假定将虚伪电源电感电容网络布置到两根电缆中,这会布置SPI MISO信号的RS-485/RS-422转化。图4描绘主机和从机SPI至RS-485/RS-422的规划,以及SPI MISO数据线的虚伪电源滤波器电路。滤波器电路选用高通电缆,所以要求传输的数据信号不能包含直流内容或极低频率的内容。

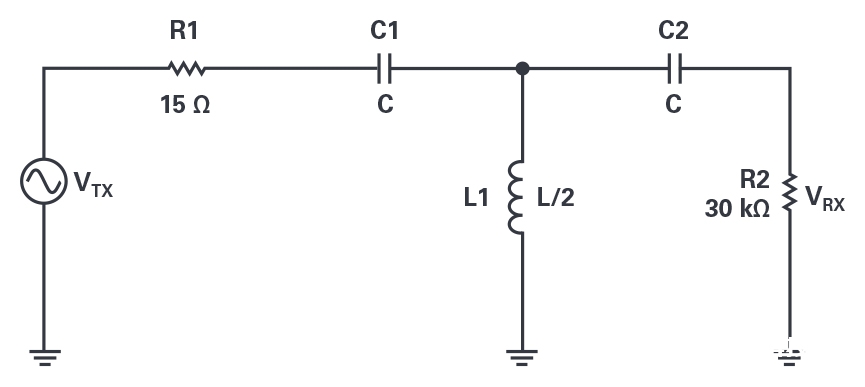

图5所示为二阶高通滤波器电路,这是对图4的简化演示。RS-485/RS-422发射器的电压输出标记为VTX,R1具有15Ω输出电阻。R2为30 kΩ,是RS-485/RS-422接纳器的规范输入电阻。电感(L)和电容(C)值能够挑选,以匹配所需的体系数据速率。

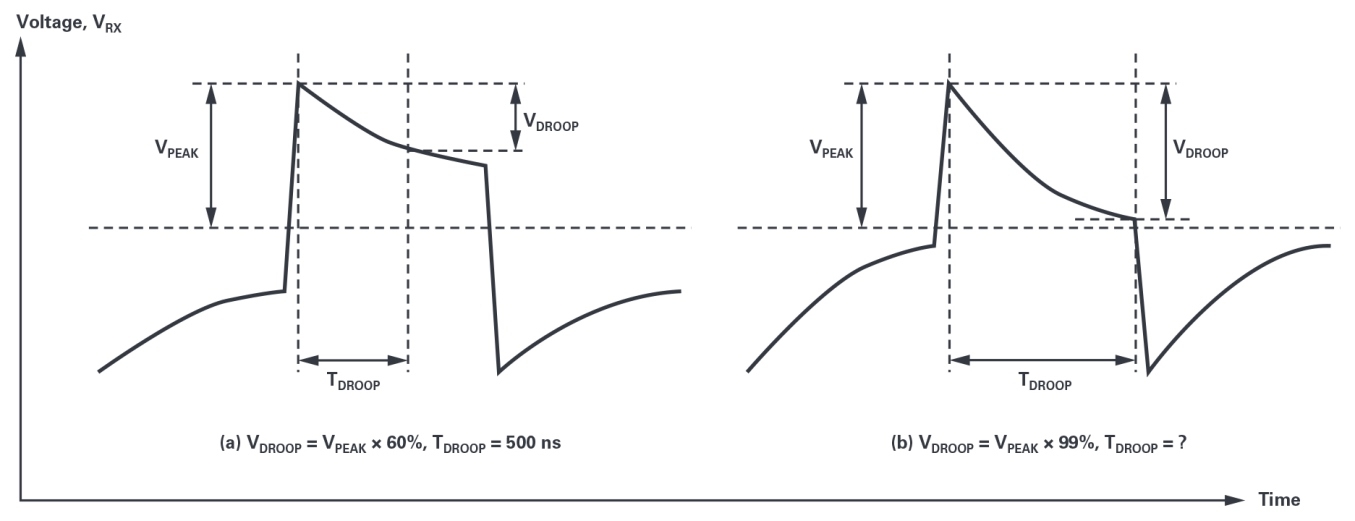

挑选电感(L)和电容(C)值时,需求考虑最大的RS-485/RS-422总线压降和压降时刻,如图6所示。存在一些规范,例如关于单根双绞线以太网2,指出的最大可答应压降和压降时刻如图6a所示。关于有些体系,最大的可答应压降和压降时刻值或许更大,受信号极性交越点约束,如图6b所示。

压降和压降时刻可与图5中的仿真配对,以确认体系的高通频率。

关于衰减超卓的体系,高通滤波器截止频率和压降要求之间的联系如公式1.3所示

在SPI至RS-485/RS-422通讯体系中添加虚伪电源时,很显然可答应的最低SPI SCLK速率会受虚伪电源滤波器元件约束。

为了完成不含位过错的牢靠通讯,需求考虑最糟糕场景下的最低SPI SCLK,例如,当一切的SPI MISO采样位处于逻辑高电平时,如图7所示。假如一切的MISO采样位都处于逻辑高电平,会导致位数据数率低于体系SPI SCLK。例如,假如SPI SCLK为2 MHz,且一切16个位都处于逻辑高电平,那么虚伪电源LC滤波器网络的速率相当于125 kHz的SPI MISO位数率。

如“时刻同步和电缆长度”部分所示,电缆长度越长,需求的SPI SCLK速率越低。可是,虚伪电源会约束最低的SPI SCLK速率。要平衡这些敌对的要求,就需求当心挑选和确认无源滤波器元件的特性,尤其是电感。

图5.RS-422发射数据途径和RS-485/RS-422接纳数据途径的二阶高通滤波器。

无源元件挑选

在挑选适宜的功率电感时,需求考虑许多参数,包含满意的电感、额外/饱和电流、自谐振频率(SRF)、低直流电阻(DCR)和封装尺度。表1供给挑选的功率电感和参数。

额外电流需求满意或超越长途供电的MEMS传感器节点的总电流要求,额外饱和电流需求更大。

此电感不会给沟通数据形成高于其SRF的高阻抗,在到达某个点之后,会开端呈现电容性阻抗特性。挑选的电感SRF会约束在SPI至RS-485/RS-422物理层上运用的最大SPI SCLK,如图1所示。在长电缆上运用时,或许不会接触到SRF电感;例如,电缆超越10米时,或许无法到达11 MHz SPI SCLK速率(产品型号为744043101的SRF)。在其他情况下,在长电缆上运转时,电感SRF或许到达更低的SPI SCLK速率(2.4 MHz、1.2 MHz)。如前所述,在虚伪电源滤波器网络中运用时,电感也会约束可答应的最低SCLK速率。

值更大的电感能够选用12.7 mm × 12.7 mm封装,值更小的电感能够选用4.8 mm × 4.8 mm封装。

挑选适宜的直流电压阻隔电容时,受限要素包含瞬态过电压额外值和直流电压额外值。直流电压额外值需求超越最大的总线电压偏置值,详细如图3所示。电路或衔接器短路时,电感电流会失衡,会被端电极阻抗耗费。呈现短路时,需求设置隔直电容的额外值,以完成峰值瞬态电压。例如,在低功率体系中,电感饱和电流约为1 A时,对应的隔直电容额外值至少为4直流50 V4。

图6.RS-422接纳器的压降和压降时刻。

表2显现在经过权衡这些敌对要求,以最小化电感尺度时,会由于物理约束(内部绕组)等受到约束。

| 表1.挑选的功率电感参数 | |||||

|---|---|---|---|---|---|

|

产品型号 |

L (µH) |

IRATED (mA) |

自谐振频率 (SRF)(MHz) |

直流电阻 (DCR)(Ω) |

封装尺度 (mm) |

|

744043101 |

100 |

290 |

11 |

0.6 |

4.8 × 4.8 |

|

LPS8045B-105 |

1000 |

230 |

1.3 |

3.22 |

8.0 × 8.0 |

|

76877530 |

300 |

2.4 |

3.3 |

7.8 × 7.0 |

|

|

SDR0805-102KL |

210 |

3.0 |

4.5 |

7.8 × 7.8 |

|

|

7687714222 |

2200 |

260 |

1.2 |

6.5 |

10 × 10 |

|

SRR1208-222KL |

280 |

0.65 |

4.2 |

12.7 × 12.7 |

|

| 表2.功率电感——对封装尺度的约束 | |

|---|---|

|

参数 |

对封装尺度的影响 |

|

满意高的电感 |

电感值越高,内部绕组越多,封装尺度越大。 |

|

更高的SRF |

SRF越高,内部绕组越少,封装尺度越小。 |

|

更高的额外和饱和电流 |

内部绕组更少,但封装尺度更大。 |

|

低DCR |

要完成更低的DCR,电缆需求更粗,且削减绕组。 |