简介

在当今的许多细分商场,交错型模数转化器(ADC)在许多运用中都具有多项优势。在通讯基础设施中,存在着一种推进要素,使ADC的采样速率不断进步,以便支撑多频段、多载波无线电,除此之外满意DPD(数字预失真)等线性化技能中更宽的带宽要求。在军事和航空航天范畴,采样速率更高的ADC可让多功能体系用于通讯、电子监控和雷达等多种运用中——此处仅举数例。工业仪器仪表运用中一直需求采样速率更高的ADC,以便充沛准确地丈量速度更高的信号。

首要,必定要准确地了解交错型ADC是什么。要了解交错,最好了解一下实践发生的状况以及它是怎么完成的。有了根本的了解后,再评论交错的优点。当然,咱们都知道,天下没有免费的午饭,因而需求充沛评价和验证交错型采样相关的技能难点。

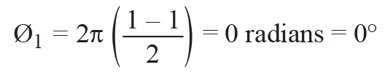

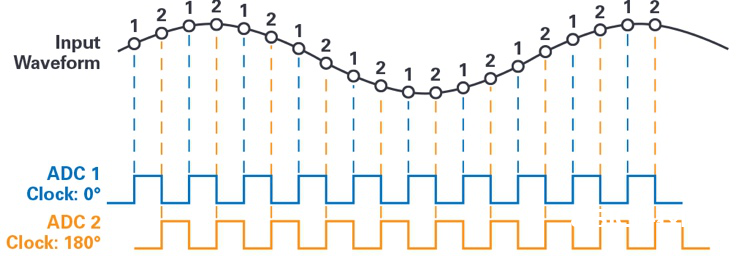

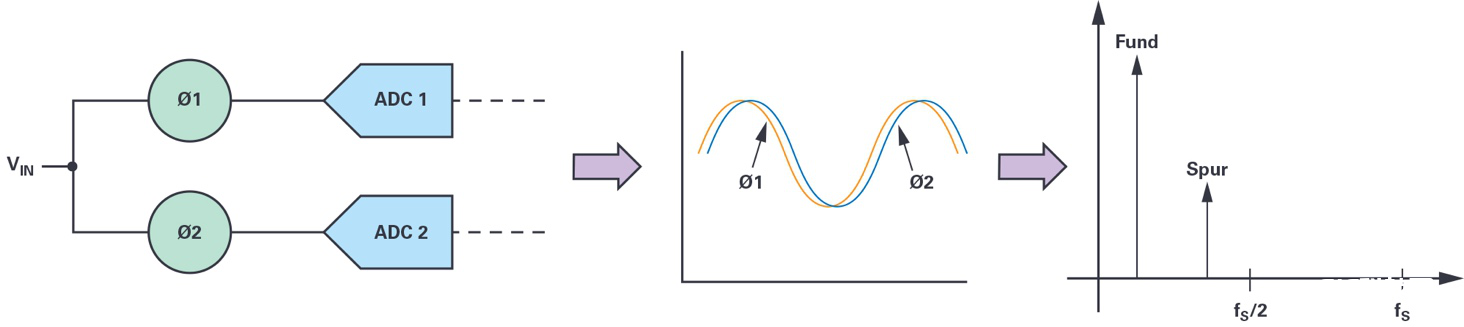

图1.两个交错型100 MSPS ADC — 根本原理图。

关于交错

若ADC为交错型,则两个或两个以上具有固定时钟相位差联系的ADC用来同步采样输入信号,并发生组合输出信号,使得采样带宽为单个ADC带宽的数倍。运用m个ADC可让有用采样速率添加m倍。为简洁起见并易于了解,咱们要点调查两个ADC的状况。这种状况下,假如两个ADC的每一个采样速率均为fS且呈交错型,则终究采样速率为2× fS。这两个ADC有必要具有确认的时钟相位差联系,才干正确交错。时钟相位联系由等式1给出,其间:n是某个特定的ADC,m是ADC总数。

|

|

(1) |

举例而言,两个ADC采样速率均为100 MSPS且呈交错型,因而采样速率为200 MSPS。此刻,等式1可用来推导出两个ADC的时钟相位联系,如等式2和等式3。

|

|

(2) |

|

|

(3) |

留意,假如已知时钟相位联系,便可确认不同量化值的组合输出。图1以图形阐明时钟相位联系,以及两个100 MSPS交错型ADC的样本结构。留意180°时钟相位联系,以及样本是怎么交错的。输入波形也可由两个ADC进行采样。在这种状况下,选用经过2分频的200 MHz时钟输入,并所需的时钟相位发送至每个ADC,便可完成交错。

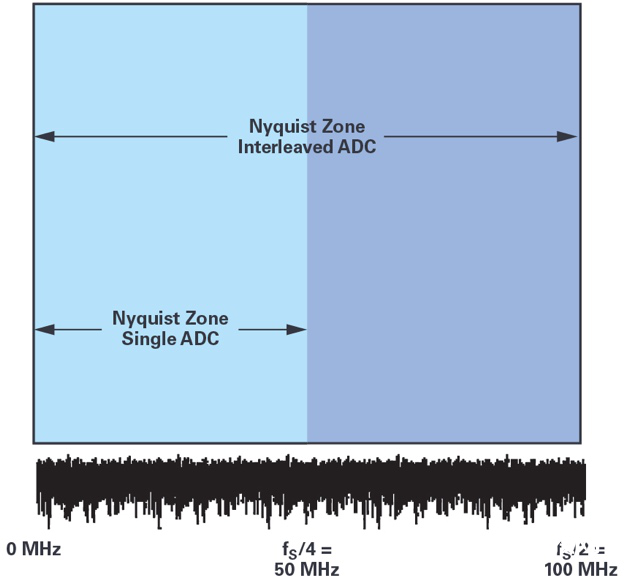

此概念还能够另一种办法表达,如图2所示。经过将这两个100 MSPS ADC以交错办法组合,采样速率便能添加至200 MSPS。这样每个奈奎斯特区能够从50 MHz扩展到100 MHz,使作业时的可用带宽翻倍。添加的作业带宽可为多个商场范畴的运用带来许多优势。无线电体系能够添加其支撑的频段数;雷达体系能够添加空间分辨率;而丈量设备能够完成更高的模仿输入带宽。

图2.两个交错型100 MSPS ADC — 时钟和样本。

交错的优势

交错结构的优势可惠及多个细分商场。交错型ADC最大优点是添加了带宽,由于ADC的奈奎斯特带宽更宽了。相同,咱们举两个100 MSPS ADC交错以完成200 MSPS采样速率的比如。图3显现经过交错两个ADC,能够大幅添加带宽。这为多种运用场景发生了许多收益。就像蜂窝规范添加了通道带宽和作业频段数相同,对ADC可用带宽的要求也越来越高。此外,在军事运用中,需求更好的空间辨认才能以及添加后端通讯的通道带宽,这些都要求ADC供给更高的带宽。由于这些范畴对带宽的要求越来越高,因而需求准确地丈量这些信号。因而,为了正确地获取和丈量这些高带宽信号,丈量设备也需求更高的带宽。许多规划中的体系要求其实领先于商用ADC技能。交错型结构能够补偿这一技能距离。

添加采样速率能够为这些运用供给更多的带宽,而且频率规划更轻松,还能下降通常在ADC输入端运用抗混叠滤波器时带来的杂乱性和本钱。面临这些优势,咱们必定想知道需求为此支付什么价值。就像大多数工作相同,天下没有免费的午饭。交错型ADC具有更高的带宽和其他有用的优势,但在处理交错型ADC时也会带来一些应战。

图3.两个交错型ADC——奈奎斯特区

交错型ADC的应战

在交错组合ADC时存在一些应战,还有一些留意事项。由于与交错型ADC相关的缺点,输出频谱中会呈现杂散。这些缺点根本上是两个正在交错的ADC之间不匹配。输出频谱中的杂散导致的根本不匹配有四种。包含失调不匹配、增益不匹配、时序不匹配和带宽不匹配。

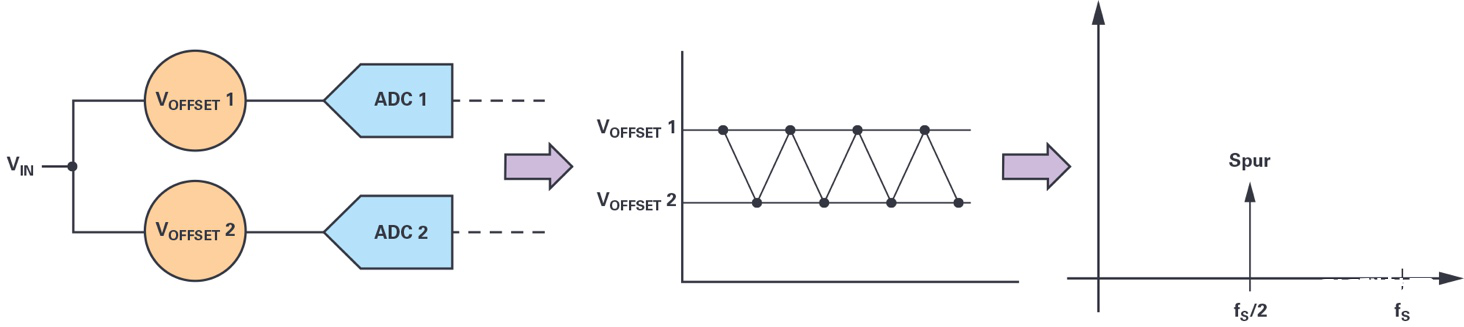

其间最简略了解的或许是两个ADC之间的失调不匹配。每个ADC都会有一个相关的直流失调值。当两个ADC交错并在两个ADC之间来回替换采样时,每个接连采样的直流失调会发生变化。图4举例阐明了每个ADC怎么具有自己的直流失调,以及交错输出怎么有用地在这两个直流失调值之间来回切换。输出以fS/2的速率在这些失调值之间切换,将导致坐落fS/2的输出频谱中发生杂散。由于不匹配自身没有频率重量,而且仅为直流,因而呈现在输出频谱中的杂散频率仅取决于采样频率,并将一直呈现在fS/2频率下。杂散的起伏取决于ADC之间失调不匹配的起伏。不匹配值越大,杂散值就越大。为了尽或许削减失调不匹配导致的杂散,不需求彻底消除每个ADC中的直流失调。这样做会滤除信号中的一切直流成分,不适合运用零中频(ZIF)架构的体系,该架构信号成分杂乱,DC量实践是有用信号。相反,更适宜的技能是让其间一个ADC的失调与另一个ADC匹配。挑选一个ADC的失调作为基准,另一个ADC的失调设置为尽或许挨近的值。失调值的匹配度越高,在fS/2发生的杂散就越低。

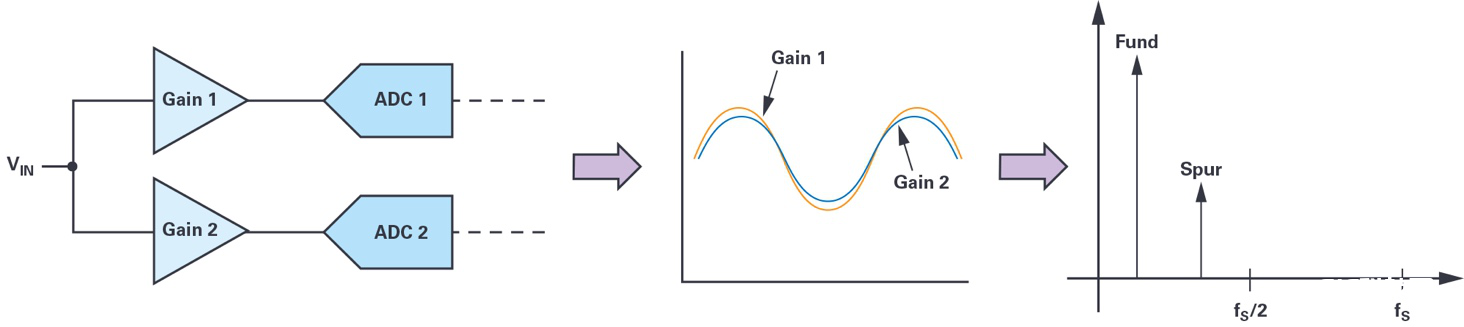

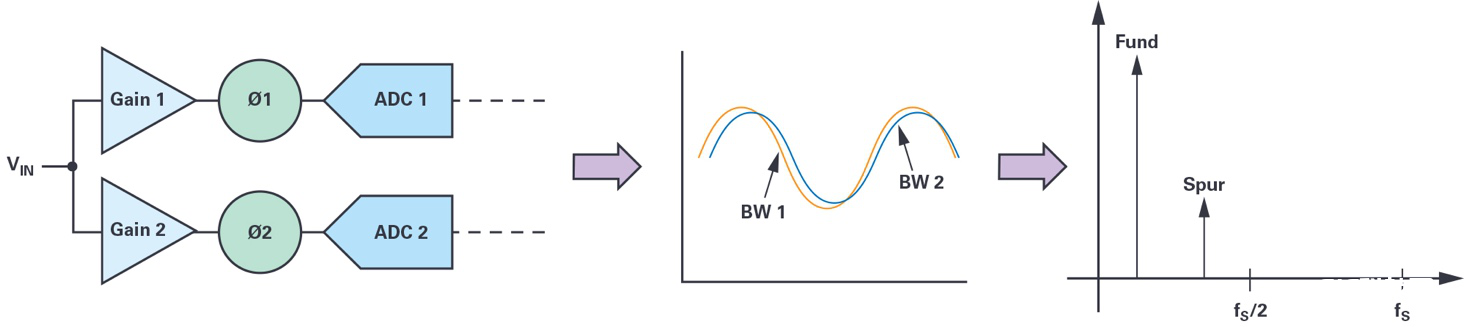

交错时要留意的第二个不匹配是ADC之间的增益不匹配。图5显现了两个交错型转化器之间的增益不匹配。在这种状况下,有一个不匹配频率重量。为了调查这种不匹配,有必要向ADC施加信号。关于失调不匹配,无需信号即可检查两个ADC的固有直流失调。关于增益不匹配,假如不存在信号,就无法丈量增益不匹配,因而无法了解增益不匹配。增益不匹配将会发生与输入频率和采样速率相关的输出频谱杂散,呈现在fS/2 ± fIN处。为了最大程度地下降增益不匹配引起的杂散,选用了与失调不匹配相似的战略。挑选其间一个ADC的增益作为基准,另一个ADC的增益设置为尽或许挨近的值。每个ADC增益值的匹配度越高,输出频谱中发生的杂散就越小。

接下来,咱们有必要评论两个ADC之间的时序不匹配。时序不匹配有两个重量:ADC模仿部分的群推迟和时钟相位误差。ADC中的模仿电路具有相关的群推迟,两个ADC的群推迟值或许不同。此外还有时钟相位误差,它也包含两个重量:各ADC的孔径不确认性和一个与输入各转化器的时钟相位精度相关的重量。图6以图形阐明ADC时序不匹配的机制和影响。与增益不匹配杂散相似,时序不匹配杂散也与输入频率和采样速率呈函数联系,呈现在fS/2 ± fIN处。

图4.失调不匹配

为了尽或许下降时序不匹配引起的杂散,需求运用适宜的电路规划技能使各转化器模仿部分的群推迟恰当匹配。此外,时钟途径规划有必要尽量共同以使孔径不确认性差异最小。最终,有必要准确操控时钟相位联系,使得两个输入时钟尽或许相差180°。与其他不匹配相同,方针是尽量消除引起时序不匹配的机制。

最终一个不匹配或许最难了解和处理:带宽不匹配。如图7所示,带宽不匹配具有增益和相位/频率重量。这使得处理带宽不匹配问题变得更为困难,由于它含有别的两个不匹配参数的重量。但是,在带宽不匹配中,咱们可在不同的频率下看到不同增益值。此外,带宽具有时序重量,使不同频率下的信号经过每个转化器时具有不同的推迟。超卓的电路规划和布局布线实践是削减ADC间带宽失配的最好办法。ADC之间的匹配越好,则发生的杂散就越少。正如增益和时序不匹配会导致在输出频谱的fS/2 ± fIN处发生杂散相同,带宽不匹配也会在相同频率处发生杂散。

图5.增益不匹配

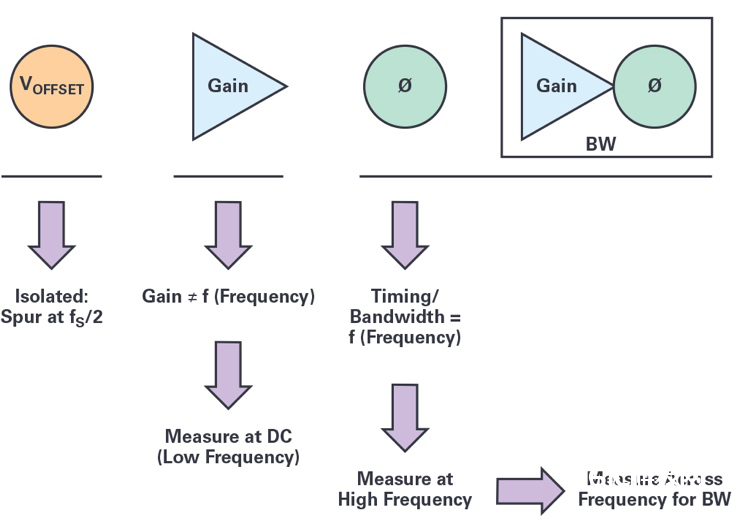

现在咱们现已评论了交错ADC时引起问题的四种不同的不匹配,能够发现有一个共性。四个不匹配中有三个会在输出频谱的fS/2 ± fIN处发生杂散。失调不匹配杂散很简略辨认,由于只要它坐落fS/2处,并可轻松地进行补偿。增益、时序和带宽不匹配都会在输出频谱的fS/2 ± fIN处发生杂散;因而,随之而来的问题是:怎么确认它们各自的影响。图8以简略的图形办法辅导怎么从交错型ADC的不同不匹配中辨认杂散来历。

假如仅仅调查增益不匹配,那么它便是一个低频(或直流)类型的不匹配。经过在直流邻近履行低频增益丈量,然后在较高的频率处履行增益丈量,可将带宽不匹配的增益重量与增益不匹配别离。增益不匹配与频率无函数联系,而带宽不匹配的增益重量与频率呈函数联系。关于时序不匹配,能够选用相似的办法。在直流邻近履行低频丈量,然后在较高的频率下履行后续丈量,以便将带宽不匹配的时序重量与时序不匹配别离。

图6.时序不匹配

定论

最新通讯体系规划、顶级雷达技能和超高带宽丈量设备好像一直领先于现有的ADC技能。在这些需求的推进下,ADC的用户和制作商都想方设法,企图跟上这些需求的脚步。与进步典型ADC转化速率的传统办法比较,交错型ADC能够更快的速度完成更宽的带宽。将两个或更多ADC交错起来,能够添加可用带宽,并以更快的速度满意体系规划要求。但是,交错型ADC并非没有价值,ADC之间的不匹配不容忽视。尽管不匹配的确存在,但了解其本质及怎么正确处理它们,规划人员就能愈加明智地运用这些交错型ADC,并满意最新体系规划不断增加的要求。

图7.带宽不匹配

参考文献

Had、Jim、Mark Looney和Rob Reeder。“ 推进 多通道 模数转化器技能发展 。”《模仿对话》,第39卷第5期,2005年5月。

图8.交错型不匹配的相互联系

作者简介

Jonathan Harris是ADI公司高速转化器部(北卡罗来纳州格林斯博罗)的一名产品运用工程师。作为一名产品支撑运用工程师,他在射频业具有超越七年的经历。Jonathan具有奥本大学电子工程硕士学位和北卡罗来纳大学夏洛特分校电子工程学士学位。平常喜爱移动音频、nitro RC、大学橄榄球,以及陪同两个孩子。