关断形式常常会保存存储器内容,发动时刻更短,漏电流超低,而假定堵截电源,这一切都不复存在。 可是,假定不需求这些特性呢? 规划人员会让电源坚持稳定并运用关断形式而糟蹋电源吗? 为何不能简略地经过堵截电源来下降漏电流? 关断形式是否存在一些根本的深层次的要求? 感到疑惑不解? 请看下文。

引诱与危险

现代体系包含丰厚的特性,这是经过多层次的杂乱规划完成的,常常涉及到不止一个芯片。 功耗是许多运用都关怀的,比如便携式医疗设备,因而这些芯片常常包含一种或多种关断形式。 这些形式供给存储器内容保存、外设运用和快速敞开等特性,而耗费的电源电流十分少。 另一种办法是彻底关断电源。 这会彻底堵截芯片的电源,不允许任何电流进入电源引脚。 尽管能够下降功耗,但这种办法存在一些严峻的副效果。

考虑一个包含多个芯片的杂乱体系,这些芯片经过多路复用总线相连。 假定该体系规划用于功耗受限的运用,简略地堵截未在运用的芯片电源好像有利可图,尤其是在不需求关断形式供给的其他特性的时分。 堵截电源可下降漏电流,但没有电源时,引脚对输入信号或许起到低阻抗节点的效果,导致不行猜测的操作和潜在的体系级要挟。 尽管断电选项或许很诱人,但关断形式对杂乱体系有着根本上的长处: 它使各芯片处于已知的、期望的状况,即便芯片在低功耗与高功能形式之间循环,也能坚持安全可靠的操作。 详细状况可经过调查一个I/O节点来了解。

简略示例

图1中的引脚衔接到一个复用节点,其操作由一个经验证的体系架构设定。 作为I/O引脚,它一起具有输入和输出功用。

图1. 简化的I/O电路

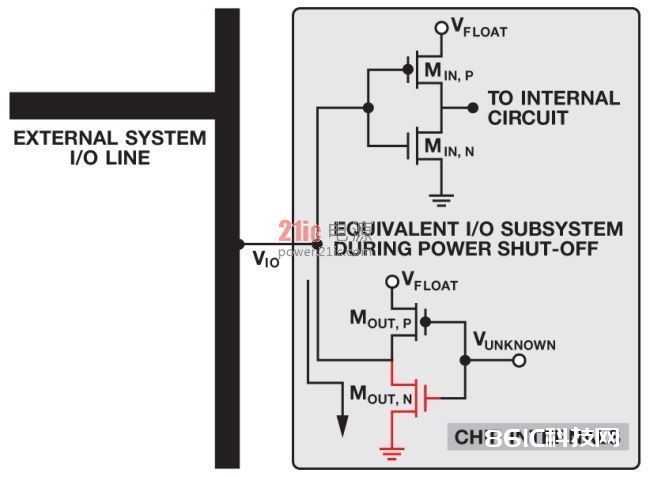

不考虑功率开关所用器材的问题,断开此芯片的电源(假定不需求任何芯片操作)将导致图2所示的状况,芯片内核处处都是不知道状况。 在最坏状况下,浮置栅极输出器材(MOUT, p和MOUT, n)或许会在休眠时露出于意想不到的外部电压下。 关于本例所示的CMOS I/O,这或许产生一个经由NMOS漏极衔接的对地低阻抗衔接(赤色亮显)。 高电流将导致前一级的驱动才能透支,然后危害芯片中的MOS电路,乃至芯片自身。 即便未危害体系,其功能也会下降。

图2. 断电形式下的I/O电路。 留意内部栅极处于不知道状况。

关断形式

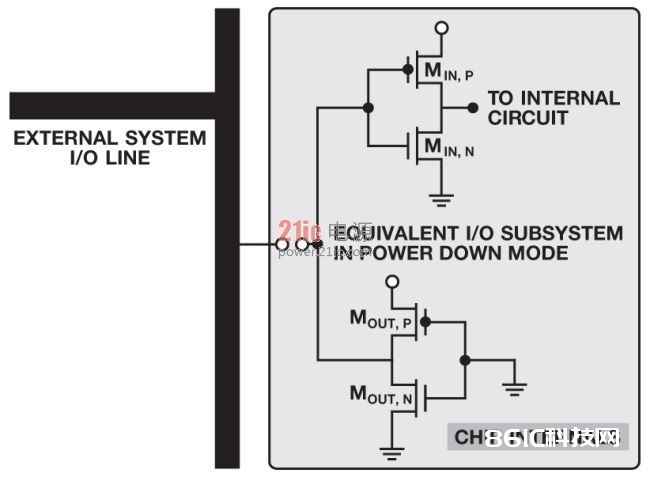

关断形式为芯片供给额定的一重维护,可防备上述意外工作状况。 完成办法会因不同的形式、产品系列和供货商而异,但重点是在芯片内核休眠时供给安全的I/O鸿沟,坚持已知的、可信赖的低功耗状况。 长处是体系器材之间的I/O操作(例如经过体系级多路复用总线)不会要挟到休眠中的器材。 一个完成计划是在低功耗形式下将I/O引脚置于高阻态,使衔接到鸿沟引脚的内部节点处于已精确界说的状况。 图3显现了一个简化的完成计划。 信号对内部电路无影响,从根本上保证其安全。 其他完成计划(例如浅休眠形式)也能够让I/O外设坚持上电,一起保证在关断形式期间芯片外设与内核之间的操作得到验证。 这使得芯片在坚持低功耗的一起,能够处理激活状况下的运用景象。 此外,该体系下降了功率开关的本钱;如若不然,将需求运用一个很大的低电阻器材,其漏电流和导通状况功耗均会相当大。

图3. 关断形式下的I/O电路。 留意一切内部节点都已精确界说。

关断形式因芯片和供货商而异,因而,“浅休眠形式”之类称号的意义并不总是相同。 有些支撑保存存储器内容,有些则供给更多的中止数或其他相似特性。 与彻底断电比较,这些形式的一个杰出优势是能够缩短体系呼应时刻。 有些电路供给独自的I/O电源和内核电源。 这种别离的一个长处是,电路板规划人员能够堵截内核电源以下降漏电流,而I/O则坚持上电。 强烈建议必定要从产品数据手册取得精确的详细信息,保证所需的特性和维护办法遭到产品的支撑。

尺度不断缩小的影响

作为器材尺度缩小的天然结果,现代IC工艺技术供给更高密度的封装,使得关断形式的优化运用越来越重要。 不过,这也下降了器材的压力处理才能。 例如,28nm器材的栅极氧化物就比相应的180nm器材要薄。 这样,断电形式下栅极电压所施加的压力更有或许损坏较小的器材。 此外,布局相关的参数也或许导致尺度较小的器材产生灾难性毛病。