1、导言

20世纪70年代,CCD图画传感器和CMOS图画传感器一起起步。CCD图画传感器由于灵敏度高、噪声低,逐步成为图画传感器的干流。但由于工艺上的原因,灵敏元件和信号处理电路不能集成在同一芯片上,构成由CCD图画传感器拼装的摄像机体积大、功耗大。CMOS图画传感器以其体积小、功耗低在图画传感器商场上别出心裁。但开端商场上的CMOS图画传感器,一向没有脱节光照灵敏度低和图画分辨率低的缺陷,图画质量还无法与CCD图画传感器比较。

假如把CMOS图画传感器的光照灵敏度再进步5倍~10倍,把噪声进一步下降,CMOS图画传感器的图画质量就能够到达或稍微超越CCD图画传感器的水平,一起能坚持体积小、分量轻、功耗低、集成度高、价位低一级长处,如此,CMOS图画传感器代替CCD图画传感器就会成为事实。

由于CMOS图画传感器的运用,新一代图画体系的开发研发得到了极大的开展,而且跟着经济规划的构成,其出产成本也得到下降。现在,CMOS图画传感器的画面质量也能与CCD图画传感器相媲美,这首要归功于图画传感器芯片规划的改进,以及亚微米和深亚微米级规划添加了像素内部的新功用。

实践上,更切当地说,CMOS图画传感器应当是一个图画体系。一个典型的CMOS图画传感器一般包含:一个图画传感器中心(是将离散信号电平多路传输到一个单一的输出,这与CCD图画传感器很相似),一切的时序逻辑、单一时钟及芯片内的可编程功用,比方增益调理、积分时刻、窗口和模数转化器。事实上,当一位规划者购买了CMOS图画传感器后,他得到的是一个包含图画阵列逻辑寄存器、存储器、守时脉冲发生器和转化器在内的悉数体系。与传统的CCD 图画体系比较,把整个图画体系集成在一块芯片上不只下降了功耗,而且具有分量较轻,占用空间削减以及整体价格更低的长处。

图1 前期的CCD图画传感器

2、根本原理

从某一方面来说,CMOS图画传感器在每个像素方位内都有一个扩大器,这就使其能在很低的带宽情况下把离散的电荷信号包转化成电压输出,而且也仅需求在帧速率下进行重置。CMOS图画传感器的长处之一便是它具有低的带宽,并添加了信噪比。由于制作工艺的约束,新近的CMOS图画传感器无法将扩大器放在像素方位以内。这种被称为PPS的技能,噪声功用很不抱负,而且还引来对CMOS图画传感器的种种搅扰。

可是今日,跟着制作工艺的进步,使在像素内部添加杂乱功用的主意成为或许。现在,在像素方位以内现已能添加比如电子开关、互阻抗扩大器和用来下降固定图形噪声的相关双采样坚持电路以及消除噪声等多种附加功用。实践上,在Conexant公司(前Rockwell半导体公司)的一台先进的CMOS 摄像机所用的CMOS图传感器上,每一个像素中都规划并运用了6个晶体管,测验到的读出噪声只要1均方根电子。不过,跟着像素内电路数量的不断添加,留给感光二极管的空间逐步削减,为了避免这个份额(又称占空因数或填充系数)的下降,一般都运用微透镜,这是由于每个像素方位上的细微透镜都能改动入射光线的方向,使得本来会落到连接点或晶体管上的光线重回到对光灵敏的二极管区域。

由于电荷被约束在像素以内,所以CMOS图画传感器的另一个固有的长处便是它的防光晕特性。在像素方位内发生的电压先是被切换到一个纵列的缓冲区内,然后再被传输到输出扩大器中,因而不会发生传输进程中的电荷损耗以及随后发生的光晕现象。它的晦气因素是每个像素中扩大器的阈值电压都有细微的不同,这种不均匀性就会引起固定图画噪声。可是,跟着CMOS图画传感器的结构规划和制作工艺的不断改进,这种效应现已得到明显弱化。

这种多功用的集成化,使得许多曾经无法运用图画技能的当地现在也变得可行了,如孩子的玩具,愈加涣散的保安摄像机、嵌入在显示器和膝上型核算机显示器中的摄像机、带相机的移动电路、指纹识别体系、甚至于医学图画上所运用的一次性照相机等,这些都已在某些规划者的考虑之中。

3规划考虑

可是,这个职业还有一个遭到遍及重视的问题,那便是丈量办法,具体方针、阵列巨细和特性等方面还缺少一致的规范。每一位工程师在比较各种资料一览表时,或许会发现在一张表上列出的是关于读出噪声或信噪比的资料,而在另一张表上或许仅仅着重关于动态规模或最大势阱容量的资料。因而,这就要求规划者们能够判别哪一个参数对他们最重要,而且尽或许充分利用多产品的CMOS图画传感器宗族。

一些要害的功用参数是任何一种图画传感器都需求重视的,包含信噪比、动态规模、噪声(固定图形噪声和读出噪声)、光学尺度以及电压的要求。应当知道并用来比照的重要参数有:最大势阱容量、各种作业状态下的读出噪声、量子功率以及暗电流,至于信噪比之类的其它参数都是由那些根本丈量推导出来的。

关于像保安摄像机一类的低照度级的运用,读出噪声和量子效应最重要。可是关于象野外拍摄一类的中、高照度级的运用,比较大的最大势阱容量就显得更为重要。

动态规模和信噪比是最简单被误解和误用的参数。动态规模是最大势阱容量与最低读出噪声的比值,它之所以引起误解,是由于读出噪声常常不是在典型的运转速度下测得的,而且暗电流散粒噪声也常常没有被核算在内。信噪比首要决议于入射光的亮度级(事实上,在亮度很低的情况下,噪声或许比信号还要大)。

所以,信噪比应该将一切的噪声源都考虑在内,有些资料一览表中常常疏忽散粒噪声,而它恰恰是中、高信号电平的首要噪声来历。而SNRDARK得到阐明,实践上与动态规模没有什么两样。数字信噪比或数字动态规模是另一个简单引起混杂的概念,它标明的仅仅模仿/数字(A/D)转化器的一个特性。尽管这或许很重要,但它并不能精确地描绘图画的质量。一起咱们也应清楚地认识到,当图画传感器具有多个可调模仿增益设置时,模仿/数字转化器的分辨率不会对图画传感器的动态规模发生约束。

光学尺度的概念的含糊,是由于传统观念而致。运用光导摄像管只能在部分规模内发生有用的图画。它的核算包含衡量单位的转化和向上舍入的办法。选用向上舍入的办法,先以毫米为单位丈量图画传感器的对角线除以16,就能得到以英寸为单位的光学尺度。例如0.97cm的尺度是1.27cm而不是 0.85cm。假设你挑选了一个光学尺度为0.85cm的图画传感器,很或许呈现图画的四周旮旯上的映影(暗影)现象。这是由于有些资料一览表诈骗性地运用了向下舍入的办法。例如,将0.97cm的尺度称为0.85cm,理由很简单:0.85cm光学尺度的图画传感器的价格要比1.27cm光学尺度的图画传感器的价格低得多,可是这对体系作业功用发生晦气影响。所以,规划者应该经过核算试用各种不同的图画传感器来得到想要的功用。

CMOS图画传感器的一个很大的长处便是它只要求一个单电压来驱动整个设备。不过规划者仍应慎重地安置电路板驱动芯片。依据实践要求,数字电压和模仿电压之间尽或许地分脱离以避免串扰。因而杰出的电路板规划,接地和屏蔽就显得非常重要。尽管这种图画传感器是一个CMOS设备并具有规范的输入/输出(I/O)电压,但它实践的输入信号适当小,而且对噪声也很灵敏。

到现在为止,已规划出高集成度单芯片CMOS图画传感器。规划者力求使有关图画的运用更简单完结多功用,包含主动增益操控(AGC)、主动曝光操控(AEC)、主动平衡(AMB)、伽玛样正、布景补偿和主动黑电平校对。一切的五颜六色矩阵处理功用都集成在芯片中。CMOS图画传感器答应片上的寄存器经过I2C总线对摄像机编程,具有动态规模宽、抗浮散且几乎没有拖影的长处。

4、CMOS APS的潜在长处和规划办法

4.1CMOS APS胜过CCD图画传感器的潜在长处

CMOS APS胜过CCD图画传感器的潜在长处包含[1]~[5]:

1)消除了电荷重复搬运的费事,免除了在辐射条件下电荷搬运功率(CTE)的退化和下降。

2)作业电流很小,能够避免单一振荡和信号闭锁。

3)在集成电路芯片中可进行信号处理,因而可供给芯迹线,模/数转化的自调理,也能供给由电压漂移引起的辐射调理。

4.2CMOS APS的规划办法

CMOS APS的规划办法包含:

1)为了下降暗电流而进行研发立异的像素结构。

2)运用耐辐射的铸造方,再研发和开发中等尺度“dumb”(哑)成像仪(经过重复地开发最佳像素结构)。

3)研发在芯片上进行信号处理的器材,以习惯主动调理自身电压Vt的漂移和动态规模的丢失。

4)研发和开发耐辐射(单一扰动环境)的守时和操控设备。

5)研发和加固耐辐射的模/数转化器。

6)寻觅低温作业条件,以便在接受最大幅射强度时,找到并证明最佳的作业温度。

7)研发和开发大尺度、全数字化、耐辐射的CMOS APS,以便出产。

8)测验、点评和判定该器材的功用。

9)引进今世最高水平的组合式光学通讯/成像体系测验台。

5、像素电路结构规划

现在,已规划的CMOS图画传感器像素结构有:空地堆集二极管(HAD)型结构、光电二极管型无源像素结构、光电二极管型有源像素结构、对数变换积分电路型结构、埋葬电荷堆集和灵敏晶体管阵列(BCAST)型结构、低压驱动埋葬光电二极管(LV-BPD)型结构、深P阱光电二极管型结构、针型光电二极管(PPD)结构和光栅型有源像素结构等。

5.1CMOS PPS像素结构规划

光电二极管型CMOS无源像素传感器(CMOS PPS)的结构自从1967年Weckler初次提出以来实质上一向没有改动,其结构如图1所示。它由一个反向偏置的光敏二极管和一个开关管构成。当开关管敞开时,光敏二极管与笔直的列线连通。坐落列线结尾的电荷积分扩大器读出电路坚持列线电压为一常数,并减小KTC噪声。当光敏二极管存贮的信号电荷被读出时,其电压被复位到列线电压水平,与此一起,与光信号成正比的电荷由电荷积分扩大器转化为电荷输出。

单管的PD CMOS PPS答应在给定的像素尺度下有最高的规划填充系数,或许在给定的规划填充系数下,能够规划出最小的像素尺度。别的一个开关管也能够选用,以完结二维的X Y寻址。由于填充系数高且没有许多CCD中多晶硅叠层,CMOS PPS像素结构的量子功率较高。可是,由于传输线电容较大,CMOS PPS读出噪声较高,典型值为250个均方根电子,这是丧命的缺点。

5.2 CMOS APS的像素结构规划

几乎在CMOS PPS像素结构创造的一起,科学家很快认识到在像素内引进缓冲器或扩大器能够改进像素的功用。尽管CMOS图画传感器的成像设备将光子转化为电子的办法与CCD相同,但它不是时钟驱动,而是由晶体三极管作为电荷感应扩大器。在一些CMOS图画传感器中,每组像素的顶端有一个扩大器,每个像素只要一个作为阈值电流值开关的三极管。开关像素中的电荷为扩大器充电,其进程相似DRAM中的读取电路,这种传感器被称为PPS。PPS的结构很简单,它具有高填充系数。各像元没有许多的多晶硅层掩盖,其量子功率很高,可是PPS的读取搅扰很高,只习惯于小阵列传感器。

在CMOS APS中每一像素内都有自己的扩大器。CMOS APS的填充系数比CMOS PPS的小,集成在外表的扩大晶体管削减了像素元件的有用外表积,下降了“封装密度”,使40%~50%的入射光被反射。这种传感器的另一个问题是,怎么使传感器的多通道扩大器之间有较好的匹配,这能够经过下降剩余水平的固定图形噪声较好地完结。由于CMOS APS像素内的每个扩大器仅在此读出期间被激起,所以CMOS APS的功耗比CCD图画传感器的还小。与CMOS PPS比较,CMOS-APS的填充系数较小,其规划填充系数典型值为20%~30%,挨近内线转化CCD的值。

5.2.1 光敏二极管CMOS APS(PD CMOS APS)的像素结构

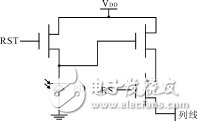

1968年,Noble描绘了PD CMOS APS。后来,这种像素结构有所改进。PD CMOS APS的像素结构如图2所示。

高功用CMOS APS由美国哥伦比亚大学电子工程系和喷气推动实验室(JPL)在1994年初次研发成功,像素数为128×128,像素尺度为40μm×40μm,管芯尺度为6.8mm×6.8mm,选用1.2μmCMOSn阱工艺试制,动态规模为72dB,固定图形噪声小于0.15%饱满信号水平。固定图形噪声小于0.15%饱满信号水平。1997年***东芝公司研发成功了640×480像素光敏二极管型CMOS APS,其像素尺度为 5.6μm×5.6μm,具有五颜六色滤色膜和微透镜阵列。2000年美国Foveon公司与美国国家半导体公司选用0.18μmCMOS工艺研发成功 4096×4096像素CMOS APS[10],像素尺度为5μm×5μm,管芯尺度为22mm×22mm,这是迄今为止世界上集成度最高、分辨率最高的CMOS固体摄像器材。有关CMOS APS的作业原理、开展现状及其运用,笔者已作过具体介绍[6]~[8]。

由于光敏面没有多晶硅叠层,PD CMOS APS的量子功率较高,它的读出噪声由复位噪声约束,典型值为75均方根电子~100均方根电子。PD CMOS APS的每个像素选用3个晶体管,典型的像元距离为15μm。PD CMOS APS适宜于大多数低功用运用。

5.2.2 光栅型CMOS APS(PG CMOS APS)的像素结构

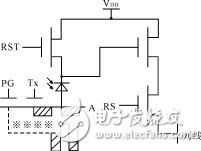

1993年由JPL最早研发成功PG CMOS APS并用于高功用科学成像的低光照明成像。PG CMOS APS结合了CCD和X Y寻址的长处,其结构如图3所示。

光栅信号电荷积分在光栅(PG)下,浮置分散点(A)复位(电压为VDD),然后改动光栅脉冲,搜集在光栅下的信号电荷搬运到分散点,复位电压水平与信号电压水平之差便是传感器的输出信号。

当选用双层多晶硅工艺时,PG与搬运栅(TX)之间要恰当交叠。在光栅与搬运栅之间刺进分散桥,能够选用单层多晶硅工艺,这种分散桥要引起大约100个电子的拖影。

光栅型CMOS APS每个像素选用5个晶体管,典型的像素距离为20μm(最小特征尺度)。选用0.25μmCMOS工艺将答应到达5μm的像素距离。浮置分散%&&&&&%的典型值为10-14F量级,发生20μV/e的增益,读出噪声一般为10均方根电子~20均方根电子,已有读出噪声为5均方根电子的报导。

CMOS图画传感器的规划分为两大部分,即电路规划和工艺规划,CMOS图画传感器的功用好坏,不只与资料、工艺有关,更重要的是取决于电路规划和工艺流程以及工艺参数规划。这对规划人员提出更高的要求,规划人员面要宽,在规划中,不但要懂电路、工艺、体系方面的常识,还要有较深的理论常识。这个年代对规划者来说是一个令人兴奋和充溢应战的年代。核算机辅助规划技能为规划者供给了极大的便利,但图画体系的用处以及方针用户的规模由制作商决议。假如用户装有Windows95的体系,那么就要确认图画体系不是Windows98的。假如你仅仅为了获取并存储很多的低分辨率图画,那就不要挑选一个能够供给优质图画但一起会发生更多数据以致于无法存储的高分辨率图画传感器。现在还存在许多非规范的接口体系。现在仅供数字相机所运用可装卸存储介质就包含 PCMCIA卡、东芝(Toshiba)的速闪存储器及软磁盘。重要的是,要依据产品未来地点的作业环境,对样品进行详尽的功用评价。

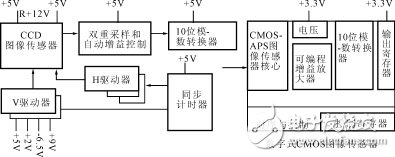

5.3 CCD和CMOS体系的规划

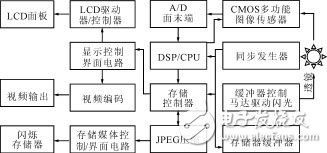

CCD图画传感器和CMOS图画传感器在规划上各不相同,关于CCD图画传感器,不能在同一芯片上集成所需的功用电路。因而,在规划时,除规划光灵敏部分(即CCD图画传感器)外,还要考虑规划供给信号和图画处理的功用电路,即信号读出和处理电路,这些电路需求在别的的基片上制备好后才干拼装在 CCD图画传感器的外围;而CMOS图画传感器则不同,特别是CMOS APS能够将一切的功用电路与光灵敏部分(光电二极管)一起集成在同一基片上,制作成高度集成化的单芯片摄像体系。与前者比较,成本低、制备简单、体积小、微型化、功耗低,尽管开端有人以为光照灵敏度不如CCD图画传感器的高,而且暗电流和噪声比较大,近来由于改进了电路规划,选用亚微米和深亚微米光刻技能,使CMOS图画传感器的功用得到改进。现已具有与CCD图画传感器进行竞赛的条件,21世纪,CMOS摄像器材将成为信息获取与处理范畴的佼佼者。到那时,单芯片摄像机和单芯片数码相机将进入千家万户。这些都得益于 CMOS APS为人们供给了高度集成化的体系,如图4

所示。图5示出CMOS数码相机的框图,从中可见数码相机规划的杂乱性。

6结语

CMOS图画传感器的出路是光亮的,跟着多媒体、数字电视、可视通讯等商场的添加,CMOS图画传感器的运用远景愈加宽广。CMOS APS为MIS/CCD图画传感器规划供给了另一挑选计划,它把电荷转化成电压所需的晶体管装在每个像素内。在这种器材内均不用进行电荷搬运, 由于数据读取是在单个像素内完结的。与CCD图画传感器比较,这种器材有很老练的CMOS%&&&&&%工艺,在下降成本方面有潜力。预期CMOS APS在许多非科学运用范畴内将终究代替CCD图画传感器。