自从激光器在1960年创造以来,在激光通信中现已成为了不行或缺的关键设备,半导体激光器(LD)是用于高速率光传输体系的有吸引力的光源,但是,惋惜的是LD的阈值随温度和寿数改动,且因器材的不同体现呈现较大的差异。LD的阈值跟着温度的升高而显着增大。LD阈值的漂移,给运用带来很大的不便利,假如选用固定的偏流,则必定引起输出光脉冲峰值功率的起浮,并且,阈值的漂移破坏了现已规划好的作业点,然后引起有害光电推迟、张弛振动等现象。在LD高速作业时,这种现象的损害是不行忽视的。为了战胜这些弊端,有必要对输出功率进行操控,使LD的作业能够维持在正确的作业点上。

姚嘉陵等曾规划依据模仿电路的APC主动激光功率操控电路,经过反应来主动调整预偏置电流来到达安稳LD输出功率的操控。基本原理是一方面将LD背向输出的光功率经背向光探测器PD进行检测,然后经过扩大器1进行扩大,送到比较器的反相输入端;另一方面,输入信号和从直流稳压电源中取出的直流参阅电压经过扩大器2扩大后送入比较器的同相输入端,比较器的输出作为反应被送到LD的驱动端,调理偏流,到达安稳LD输出功率的意图。

模仿电路办法完结的长处是增益操控比较安稳,缺陷是需求参加的器材较多,且跟着运用时间的添加,模仿器材老化会影响反应操控的差错,别的,输出的激光功率固定不行变,不能完结多级功率的操控。

笔者提出一种依据FPGA的全数字激光器功率主动操控体系,不光能够大大简化电路结构,削减本钱,一起消除由器材老化带来差错,还能够便利的改动激光器的输出功率和完结激光器多级功率的操控。

1 主动功率操控体系全体结构

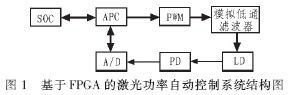

依据FPGA的激光功率主动操控体系结构如图1所示其作业原理是:将半导体激光器LD背向输出的光功率经背向光探测器PD进行检测后,转化成模仿电压信号,该模仿电压信号经过A/D转化芯片的采样和转化,转化成代表LD实践输出功率的数字信号,该数字信号被送入FPGA芯片中的APC(主动功率操控模块)进行分类、比较和处理,终究输出调整后的激光器数字偏流信号,数字偏流信号经过FPGA内部的PWM模块和外部的模仿低通滤波器转化成模仿信号,来驱动半导体激光器LD。SOC用于设置多级激光器输出功率设置,APC的作业、中止等操控。

如图1所示,本文所规划的全数字激光器主动功率操控体系由A/D转化器、FPGA功用规划模块和模仿低通滤波器3个部分组成。

2 FPGA模块规划

本规划运用的是Avnet Design Services公司规划的FPGA评价板,该评价板运用的是Xilinx公司XC4VLX25-FF668型FPGA芯片。一起,板上还有32MB的DDR SDRAM和8MB的Intel StrataFlash,10/100M自适应以太网接口、USB2.0接口和RS232串行接口,128×64的OLED(Organic Light Emitting Diode)图形显现,3组140针通用I/O衔接器(AvBus)等硬件结构组成。

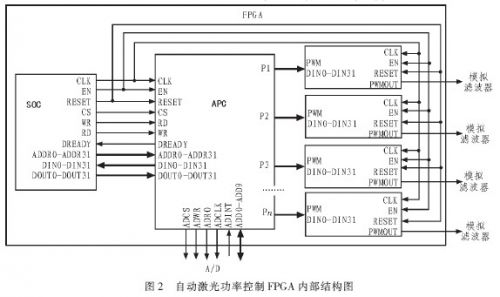

如图2所示,本文中FPGA规划包含3个部分,SOC、APC和PWM。

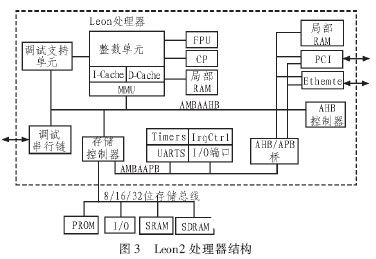

SOC是选用的由GaislerResearch公司于2003年研发完结的一款32位、契合IEEE-1754(SPARCVS)结构的免费CPU处理器核Leon2。它的前身是欧空局研发的Leon以及ERC32。Leon2的方针首要是权衡功用和价格、高的可靠性、可移植性、可扩展性、软件兼容性等,其内部硬件资源可裁剪(可装备)、首要面向嵌入式体系,能够用FPGA/CPLD和AS%&&&&&%等技能完结。Leon2处理器的片上资源如下:别离的指令和数据Cache、硬件乘法器和除法器、中止操控器、具有盯梢缓冲器的调试支撑单元(DSU)、2个24位定时器、2个通用异步串口(UART)、低功耗形式、看门狗电路、16位I/O端口、灵敏的存储操控器、以太网MAC和PCI接口。Leon2的VHDL模块能够在大多数归纳东西上进行归纳,能够在任何契合VHDL-87规范的仿真器上进行仿真;选用AMBA AHB/APB总线结构的用户规划新模块,能够很简略参加到Leon2中,完结用户的定制运用。其结构如图3所示。

文中SOC首要完结的功用是操控各个子体系的复位(RESET)与使能(EN),为各个子体系供给时钟信号(CLK),并能够经过读(RD)、写(WR)、片选(CS)3个操控信号、32位的数据输入总线(DIN0~DIN31)、32位的输出数据总线(DOUT0~DOUT31)、32位的地址总线(ADDR0~ADDR31)与各个子体系进行读、写操作。关于APC子体系,SOC首要完结APC模块和PWM模块的体系复位、使能,为APC模块、PWM模块供给时钟,设置APC模块的操控、状况寄存器等功用。

APC结构是激光功率主动操控体系的主体结构。首要功用有两个:1)完结对A/D芯片的操控,包含A/D芯片作业方式的设定(经过设置A/D芯片的操控寄存器)、A/D芯片的操控信号的发生(时钟信号ADCLK、使能信号ADCS、读操控信号ADRD、写操控信号ADWR、并接纳A/D转化完结信号ADINT和A/D转化成果ADD0~ADD9);2)对A/D转化的成果(ADD0~ADD9)进行处理,行将采样并转化的激光发射器的输出功率与设置的多级功率进行比较,区分出功率等级,再将规范等级的功率值与实践采样转化功率值进行比较,并依据比较成果给出新的LD驱动功率值。

PWM是依据APC模块输出的新的LD驱动功率值,经过调制方波的占空比来改动输出的直流重量,经过低通滤波器后得到需求的模仿电压信号,来驱动LD。运用PWM模块一能够用数字电路规划替代贵重的D/A转化器,二是能够灵敏的添加或削减被操控LD的数量。

3 主动激光功率操控规划的A/D转化模块规划

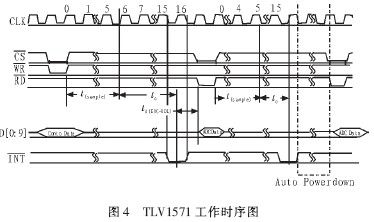

本规划中的模/数转化芯片选用的是TI公司出产的TLV1571芯片,TLV1571是一款10位单通道模仿输入的模/数转化器,内部有两个8位的操控寄存器CR0、CR1来操控ADC的作业形式,包含软件转化或硬件转化开端挑选、内部或外部时钟挑选、二进制或二进制补码输出、硬件或软件装备等作业形式。本规划经过将TLV1571的两个操控寄存器设置在外部时钟信号,软件操控转化作业方式,其作业时序如图4所示。

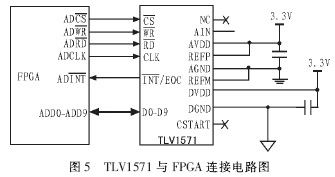

当CS和WR信号均为低电平时,写TLV1571的操控寄存器,设置完TLV1571的操控寄存器后,在WR的上升沿开端A/D采样,采样继续6个时钟周期后,主动进行A/D转化,转化需求10个时钟周期,转化完结后,INT变低,告诉FPGAA/D转化现已完结,一起,将AD转化后的数字信号在D0~D9数据总线上准备好,在RD信号的下降沿,数据被读入FPGA内进行下一步处理。TLV1571的时钟信号CLK、CS、WR、RD均由FPGA发生。D0~D9与FPGA的10个双向I/O端口相连,用于完结TLV1571两个操控寄存器的设置以及A/D转化成果的传递。图5为TLV1571与FPGA衔接电路图。

4 模仿低通滤波器的规划

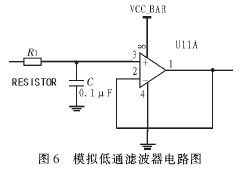

本规划的模仿低通滤波器选用简略的一阶有源滤波器,其电路结构如图6所示。

5 结束语

挑选半导体激光器LC25,设定输出功率要求为2 W,PD选用InGaAs PIN光电探测器,PD检测的成果既用于主动功率操控的输入,还作为主动功率操控的成果查验。假如主动功率操控杰出,则PD的输出将安稳在额定值上。运用泰克示波器对PD检测信号进行检测,本文规划的主动功率操控完结了对半导体激光器输出功率的安稳操控。

本文规划的新式全数字主动激光功率操控规划运用FPGA规划运用硬件资源少,节省本钱;能够经过设置相应功率等级寄存器的值就能够很简略的改动功率等级区分的规范,大大添加了功率操控的灵敏性;经过添加PWM模块和简略的模仿器材,就能够完结多个激光器的操控,大大缩短规划周期。