导言

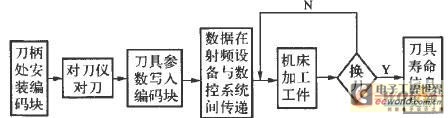

中国石油集团测井有限公司在近几年相继开发了根据DTB和CAN这2套通讯协议办法的测井体系,使7芯电缆传输速率别离到达了100 kbit/s和430 kbit/sc。因为现在这2套体系及相关仪器并存,必定添加仪器出产、运用环节的复杂度。因而.有必要开发一套综合测验设备,能一起配接2套体系的井下仪器,用于测井仪器的自检、修理和新产品的开发,进步作业效率。

本文运用DSP和FPGA高集成度数字芯片构成中心电路,经过DSP软件开发和FPGA逻辑规划,规划并完结了1个可用于DTB和CAN这2套通讯协议办法测井体系的井下仪器综合测验设备。

1 体系规划

综合测验设备体系架构见图1。该测验设备共供给了3个总线接口,别离为CAN总线接口、DTB总线接口和USB总线接口,CAN总线用于挂接430 kbit/s传输速率的仪器,DTB总线挂接100kbit/s传输速率的仪器,USB则是测验设备与计算机之间的接口。这些总线接口之间数据格局转化别离由USB/CAN转化模块和CAN/DTB转化模块完结。

CAN/DTB转化模块用于完结CAN总线和DTB总线转化。CAN总线上为该模块分配1个m,使该模块作为一个虚拟的430 kbit/s传输速率的井下仪器,挂接在CAN总线上。USB/CAN转化模块则是对CAN总线上挂接的430 kbit/s传输速率仪器的数据进行转化后,由USB总线送往计算机,计算机中运转仪器的测验软件,可存储、显现、打印接纳的数据。因而,DTB总线上挂接100 kbit/s传输速率的井下仪器数据,需求先转化到CAN总线,再转化为USB总线后送人计算机。2个总线转化模块中,USB/CAN转化模块使用很广,而CAN/DTB转化模块则成为该测验设备开发的首要作业。

为能够满意上述CAN/DTB转化功用需求,该接口转化模块的硬件选用DSP+FPGA的电路架构.由FPGA供给逻辑资源,完结DTB接口信号之间的时序联系。DSP则具有高速的软件处理才干,可用于完结程序流程操控、数据缓存和CAN总线接口。两者均为高集成度器材,都具有完善的开发手法,内部程序可便利地进行修正,规划上具有较大灵活性。在此中心电路的基础上,合作其他外部电路,如RAM、DTB电平转化模块、CAN驱动器等芯片,构成完好的接口转化模块,其结构见图2。

图1 综合测验设备使用架构

图2 CAN/DTB转化模块框图

转化模块的数字电路部分均可由FPGA和DSP完结,DTB电平改换部分首要经过模仿开关、三极管等模仿元件,将FPGA输出的+3.3 V的数字信号转化为契合DTB总线规范的信号方式,并供给必定的电流驱动才干,其电路原理相对比较简单。DSP内嵌的CAN操控器接口与CAN驱动器MAX3050合作,可便利完结CAN总线数据的发送、接纳。

2 FPGA的内部逻辑功用规划

FPGA内部逻辑首要用于完结DTB接口信号的发生和串行数据的接纳作业,由DSIG信号发送单元、UCLK及GO信号发送单元、IJlDATA信号接纳单元和存储器接口单元等4个相对独立的单元构成(见图3)。

图3 FPGA内部逻辑规划

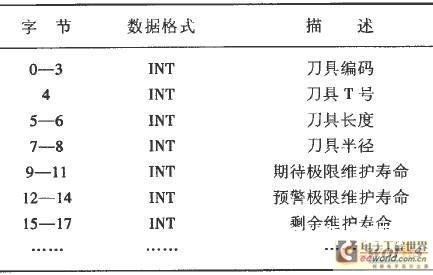

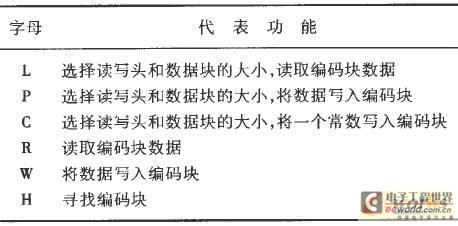

DTB总线由3根56Ω同轴电缆线组成,用于井下遥测单元与井下仪器之间进行双向数据传输。这3根信号线别离是DSIG(向下信号线)、UCLK(上行时钟线)和UDATA/GO(上行数据/发动线)。DSIG用于遥测单元给井下仪器发送指令,选用双极性归零码,有3个电平:+1.2 V表明“1”,一1.2 V表明“0”,无信号时为0 V。UCLK为上传时钟线.信号起伏为十1.2 V,周期为10μs.井下仪器的数据是在UCLK的效果下,串行地将数据发送至上行数据线上。UDATA/GO是双向信号线,每帧开端时,井下遥测单元经过发送1个起伏为+3.6V的GO脉冲.告诉井下仪器预备开端传送数据。320μS后,井下仪器在UCLK的上升沿,将收集的数据经过该信号线发送至遥测单元。

DSIG信号发送单元中.指令寄存器用于寄存要送往井下仪器的指令和接纳该指令的仪器的ID。然后将指令和仪器lD依照必定的帧格局进行安排,加上帧头帧尾以及校验等数据后,经过并/串转化电路。将DSIG信号串行发送出去。

UCLK和GO信号发送单元依照DTB数据传输的信号时序要求发生UCLK和GO信号。DTB总线上挂接的井下仪器的数据传输均是按帧进行,帧周期为80 ms。因而能够规划1个模为8 000、输入时钟频率为100 kHz的计数器完结。在每帧的开端,即计数器为0时发生GO信号,作为1帧数据传输的开端,发动井下仪器的数据传输。时钟寄存器由DSP写入,寄存每帧发往井下仪器的UCLK时钟脉冲的数目,计数器根据该寄存器的值,发生UCLK的使能信号。

井下仪器在UCLK的上升沿时将收集的数据串行送人UDATA,UDATA信号接纳单元则在UCLK的下降沿对UDATA信号进行采样,并每8bit进行1次串/并转化,将数据并行输入FIFO。详细规划时,FIFO无需占用FPGA的内部逻辑资源,而是由器材内部供给的可装备存储器完结。引出FIFO的半满指示信号送往DSP的硬件中止管脚,并经过地址译码电路,将FIFO映射到DSP的外部I/0读地址。当FIFO中的数据到达容量的一半时,对DSP发生硬件中止,使DSP进入硬件中止程序,DSP可循环读取FIFO的I/o映射地址,即可将FIFO中的数据悉数读出。

需求留意的是,一切的FPGA发生或输入的信号均需经过电平改换后,才干送往DTB总线。存储器接口单元使用DSP供给的总线信号,完结FPGA与DSP之间并行的双向数据传输。其根本办法是使用地址译码电路,将FPGA中完结的指令寄存器、状况寄存器和FIFO等具有数据存储功用的部件映射到DSP的外部I/O地址上,DSP经过读写I/O地址,能够对FPGA中存储的数据进行拜访。