导言:一年前开端用TI公司的x14x系列超低功耗单片机MSP430F149,感觉与一般的51系列比较,各个外设的功用强壮了一些,运用起来没有很大的差异,但有一个重要的差异便是外部晶振需求正确装备才干运用。现在在用TI的x54x系列的MSP430F5418芯片,发现它的各个外设的集成度更高了(比方一切的外部时钟和内部时钟由一个Unified Clock System(UCS)模块一致管理,内部Uart,IIC,SPI之类的串行接口由Universal Serial Communication Interfaces(USCI)模块一致管理),运用起来更灵活了,由此带来的影响便是装备起来也就更麻烦了。(呵呵,要想具有更强壮的功用,还不得花更多的精力去研讨它的运用方法?)

刚方才把F5418的UCS模块调通,特此庆祝一番~~

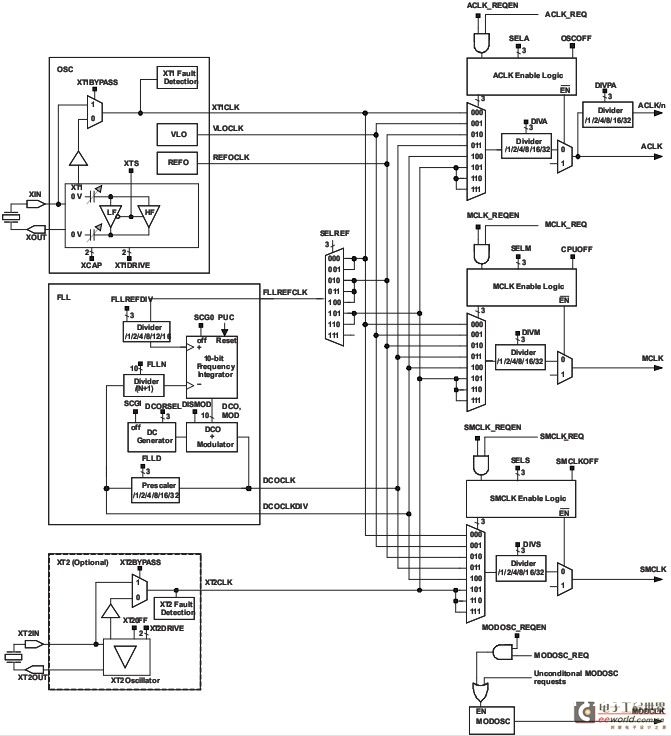

着手之前,首先要阅览TI供给的430x54x Family User Guide(slau208d)和MIXED SIGNAL MICROCONTROLLER,了解一下这种全新的芯片的时钟模块的框图,有个全体掌握:

下面是我翻译的MIXED SIGNAL MICROCONTROLLER第18页对UCS的介绍(觉得翻译欠好可别拍砖哦):

@振动器和体系时钟 (MIXED SIGNAL M%&&&&&%ROCONTROLLER, P18)

在MSP430x5xx宗族的器材中,时钟体系由一致时钟体系Unified Clock System(UCS)模块供给,它包括了一个32KHz挂钟石英晶体(XT1 LF Mode),一个内部低功率,低频率震动器(VLO),一个内部平衡的低频震动器(REFO),一个集成的内部数字可控震动器(DCO),和一个高频石英晶体振动器(XT1 HF形式或XT2).这个UCS模块的规划契合了体系对低成本和低功耗的要求,它包括数字锁频环(FLL),经过衔接一个数字的调制器,使DCO频率安稳成一个可编程倍数的挂钟石英晶体频率.其内部DCO供给了一个快速敞开的时钟源,并能够在低于5us内安稳.

一致时钟体系模块供给了如下时钟信号:

·Auxiliary辅佐时钟(ACLK),可由32KHz挂钟晶体,高频晶体,内部低频振动器(VLO),平衡的低频振动器(REFO)或内部数字操控振动器(DCO)供给.

·Main体系时钟(MCLK),供CPU运用,信号供给与ACLK相同.

·Sub-Main体系子时钟(SMCLK),供外设模块运用,信号供给与ACLK相同.

·ACLK/n,由ACLK分频后缓冲输出,分频系数可为1,2,4,8,16,32.

当你不做任何时钟装备时,你依然能够像运用一般单片机相同正常运用它,那么它是时钟默许是怎样装备的呢?这时候你就得了解USC模块的默许装备了,这部分在430x54x Family User Guide中第64页有解说。我的翻译:

@Unified Clock System(UCS)操作—430x54x Family User Guide slau208d,P64

在上电铲除信号(PUC)之后,UCS模块的默许装备是:

·XT1 低频形式被挑选为XT1CLK时钟的振动器。XT1CLK被挑选为ACLK的时钟源。

·DCOCLKDIV作为MCLK的时钟源。

·DCOCLKDIV作为SMCLK的时钟源。

·FLL(锁频环)运转被使能,XT1CLK作为FLL参阅时钟,即FLLREFCLK。

·XIN和XOUT引脚被设置为通用IO时,XT1坚持禁能直到IO口置为XT1操作形式。

·假如XT2IN和XT2OUT引脚被设置为通用IO,XT2被禁能。

在初始状况,FLL以XT1为参阅时钟的运转默许使能,但XT1被制止。要使能XT1,相应管脚的PSEL位有必要置位。当一个32.768KHz的晶振用作XT1CLK时,犯错的操控逻辑电路直接形成REFOCLK作为ACLK的时钟源,由于XT1不会当即安稳。一旦振动开端信号被获取到了,FLL就使MCLK和SMCLK安稳到1.048576MHz,f(DCO)=2.097152MHz。

状况寄存器操控位(SCG0,SCG1,OSCOFF和CPUOFF)装备MSP430的运转形式,还使能或禁能UCS模块的部分功用(参阅体系复位,中止,运转形式等章节)。寄存器UCSCTL0到UCSCTL8装备UCS模块。

废告别太多,下面直接看程序:

假如想将MCLK、SMCLK的时钟源设为外部高速晶振(我接的是16MHz),在初始化时参加以下程序段

//运用XT2振动器

P5SEL |= BIT2 + BIT3;//装备管脚为晶振输入

UCSCTL6 &= ~XT2OFF; //翻开XT2振动器

do

{

UCSCTL7 &= ~(XT2OFFG; //铲除振动器XT2失效标志

SFRIFG1 &= ~OFIFG; // 铲除振动器失效标志

//上面这句有必要有,不然起振了也不会分配成功

}

while (UCSCTL7 & XT2OFFG); //判别XT2是否起振

UCSCTL6 &= ~XT2DRIVE0;//设置驱动电流最小以降低功耗

UCSCTL4 |= SELM__XT2CLK + SELS__XT2CLK; //挑选MCLK、SMCLK为XT2

//UCSCTL5 |= DIVS__2;//SMCLK设为2分频

假如想让外部的XT1,XT2和内部DCO一起运用,并从端口输出以便于测验,衔接图暗示(参阅ti例程)

// MSP430F5418

// —————–

// /| | XIN|-

// | | | 32kHz

// —|RST XOUT|-

// | |

// | |

// | XT2IN|-

// | | HF XTAL or Resonator (add capacitors)

// | XT2OUT|-

// | |

// | P1.0|–> ACLK = 32kHz Crystal Out

// | |

// | P1.6|–> SMCLK = High Freq Xtal or Resonator Out

// | |

// | P2.0|–> MCLK = Default DCO Frwequency

// | |

// | |

在初始化是参加以下程序段:

P1DIR = BIT6 + BIT0; //

P1SEL = BIT6 + BIT0; // 装备管脚为时钟 SMCLK, ACLK输出

P2DIR = BIT0; //

P2SEL = BIT0; // 装备管脚为时钟 MCLK输出

P5SEL |= 0x0C; // 装备管脚为晶振XT2输入

P7SEL |= 0x03; // 装备管脚为晶振XT1输入

UCSCTL6 &= ~(XT1OFF + XT2OFF); // 翻开XT1,XT2振动器

UCSCTL6 |= XCAP_3; // 为XT1加载内部%&&&&&%

// 循环直到XT1,XT2 和 DCO 安稳起振

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + XT1HFOFFG + DCOFFG);

// 铲除振动器XT2,XT1,DCO失效标志

SFRIFG1 &= ~OFIFG; // 铲除振动器失效标志

}while (SFRIFG1&OFIFG); // 判别一切晶振是否起振

UCSCTL6 &= ~XT2DRIVE0; // 依据晶振频率减小XT2驱动电流以降低功耗

UCSCTL4 |= SELA__XT1CLK + SELS__XT2CLK;

// 挑选SMCLK时钟源为XT2, ACLK时钟源为XT1,MCLK默许为DCO/2