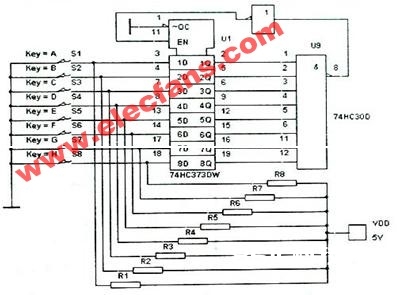

8(八)路触发锁存电路

图所示为8路触发锁存电路。图中,74HC373为8D锁存器,一开始,当一切开关均未按下时,锁存器输出全为高电平,经8输入与非门和非门后的反应信号仍为高电平,该信号作为锁存器使能端操控信号,使锁存器处于等候接纳触发输入状况;当任一开关按下时,输出信号中必有一路为低电平,则反应信号变为低电平,锁存器刚刚接纳到的开关被锁存,这时其它开关信息的输入将被封闭。由此可见,触发锁存电路具有时序电路的特征,是完成抢答器功用的要害。

也能够选用JK触发器来完成触发锁存电路的功用,详细完成办法请自己考虑。