下面咱们进入正题,今日咱们讲时序

一、从静态时序剖析说起

我了解的静态时序剖析,便是咱们在不加鼓励的状况下,经过对电路进行时序的推迟核算,估量电路的作业流程,对电路提出咱们需求的一些束缚条件,比方咱们需求从A寄存器到B寄存器的推迟不能大于10ns,假如咱们不增加时序束缚,归纳东西或许会有好几条途径,依照它自己的要求来布局布线,那么从A寄存器到B寄存器的时刻就有或许是20ns或许15ns之类的途径,而咱们需求的是不能大于10ns,因而,咱们需求增加时序束缚,再依据特定的时序模型,使咱们的体系抵达规划要求。

这儿的时刻推迟或许包含咱们的PCB板的走线推迟,也包含FPGA内部的走线推迟,时钟推迟等等,这儿咱们增加的时序束缚,就相当于咱们在没有下板之前,经过核算,来模仿仿真下板后的推迟状况,并经过时序陈述检查有哪些违规途径,以及树立坚持时刻不平衡的状况,经过时序优化使其抵达一个安稳状况的进程。

小墨在做SDRAM时序束缚的时分深有体会,即便咱们老老实实的依照时序核算公式将延时核算出来增加到工程中去,时序陈述也显现时序收敛并且也简直抵达了树立坚持时刻的平衡状况,前后仿真也没什么问题,认为全部安排妥当了,可是下板后便是跑不起来,终究我仍是改动了一下束缚参数,有时分乃至改动起伏与核算起伏比较较大,当然仍是在确保时序收敛的状况下,下板之后居然跑起来了,或许是我榜首次触摸时序这个巨大上的概念,经历不足吧,有的时分真是碰运气….当然等会我将源码同享的时分,咱们还需求自己进行时序束缚,因为咱们的FPGA芯片类型,PCB布局,SDRAM类型都不太相同,那么跑起来是件很困难的作业,所以咱们还需求自己亲自学一下这部分的常识,自己去探索。

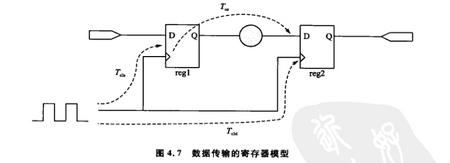

咱们直接来看这个图,

要看懂这个图,当然还需求有一个模型

时序图上的榜首个时钟,即咱们的源时钟,或许说是咱们的晶振时钟,从晶振抵达源寄存器,这段旅程肯定是有推迟的,咱们把这段推迟叫做Tc2s,也即咱们的clk1.

时序图上的第二个时钟,是咱们的源时钟抵达意图寄存器的时钟,即咱们的锁存寄存器的时钟,它到意图寄存器的推迟,咱们称为Tc2d,也即咱们的clk2

clk1 抵达源寄存器的时分,将输入的数据锁存器到源寄存器,意图寄存器没有锁存值,比及第二个时钟周期,clk2 抵达意图寄存器的时分,将源寄存器的输出数据锁存,数据有必要在clk2 抵达之前坚持安稳,从数据抵达意图寄存器到clk2抵达这段时刻,称为树立时刻,当然,数据被锁存之后,还需求坚持安稳一段时刻,这段时刻称为坚持时刻。

从数据被源寄存器锁存开端,到数据出现在意图寄存器的这段时刻,咱们称为数据的传输时刻Tco

咱们做这样一个考虑,假如Tco很长,也便是说,数据从被源寄存器捕获,到出现在意图寄存器的延时时刻较长,乃至长到clk2抵达意图寄存器的时分还没有抵达,那么,咱们就说这段途径,树立时刻违规,数据不能被正确捕获,这时分,咱们就能够给其增加束缚,让数据在多少纳秒之内抵达,确保数据被捕获,然后归纳东西就会依据咱们的要求,寻觅最佳途径,然后确保树立时刻满意长。

同理,假定Tco很短,短到clk2到来的时分,原本应该被捕获的数据,还没有坚持必定的安稳时刻,就被下一个要捕获的数据给覆盖了,或许说咱们捕获到的是下一个要捕获的数据,然后形成坚持时刻违规

所以,Tco的时刻既不能太长,也不能太短,有必要在一个合理的范围内,尽量让意图寄存器的捕获时钟在数据的有用窗口内,所以,树立坚持时刻有必要满意下列公式,公式的由来彻底来自于时序图

其间,Tc2d – Tc2s叫做时钟偏斜,这两个公式,是咱们下面剖析SDRAM时序的两个重要公式

再来看一下这两个公式,已然咱们要做时序剖析,得要知道咱们要剖析的是哪一部分吧,Tclk咱们无法改动,便是体系时钟嘛,时钟偏斜咱们也改动不了,因为关于一个特定的FPGA器材,时钟偏斜相对固定,所以咱们能够改动的便是Tco,怎样改动呢,便是增加咱们的时序束缚,让归纳东西依照咱们的要求寻觅契合咱们束缚的途径,然后满意树立坚持时刻的要求。

二、输入输出模型以及I/O束缚

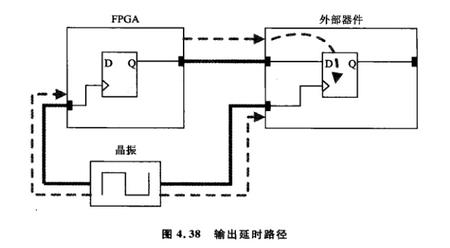

1、先来看输出模型

当然这个输出模型并不是很契合咱们的FPGA 和SDRAM的输出模型,是我从网上找来的一张图片,不过不要紧,做一下修正就好了。

咱们的源时钟需求进入FPGA的PLL中,然后输出给咱们的FPGA做内部时钟,在输出到外部做SDRAM的作业时钟,所以上图中,晶振到外部器材的时钟途径,应该是PLL的输出到SDRAM的输出途径

还有,咱们之前做的静态时序剖析,是依据在FPGA内部的,所以数据的推迟时刻只需Tco一个参数,可是,咱们的这个输出模型,是源寄存器在FPGA内部,而意图寄存器在咱们的SDRAM内部,所以,咱们的数据输出途径的推迟,还需求加上一部分,即咱们的外部PCB走线推迟

这样,咱们的输入推迟 = 数据在FPGA内部传输推迟 Tco + 外部PCB走线推迟

带入咱们的静态时序剖析的树立时刻公式得

Tco < Tclk - Tsu - 外部PCB推迟 + 时钟偏斜

由所以输出模型,所以,Tco即咱们的束缚部分,Tsu即SDRAM的树立时刻,又因为,altera官方供给的材料,不必时钟偏斜这一概念,用的是时钟网络延时,

即时钟网络延时 = – 时钟偏斜,即 Tc2s – Tc2d

所以,咱们得出输出模型的一个终究公式

Tco < Tclk - Tsu - 外部PCB推迟 - 最大时钟网络延时

其间 Tsu + 外部PCB推迟 + 最大时钟网络延时 称为最大输出延时

也即 Tco < Tclk - 最大输出延时

咱们到时分给时序剖析东西增加的,便是这个最大输出延时,有人会问,为什么咱们增加的不是 Tclk – 最大输出延时,这个问题我之前也想过,我了解的便是,最大输出延时是实在存在的,当咱们下板之后,这些延时会直接影响体系的,而Tclk的确固定的,因而,咱们只需求算出最大输出延时,其实Tco就现已确认了,归纳东西会依据这个确认值寻觅途径

同理,咱们依据静态时序剖析的公式算出最小输出延时

即Tco + 外部PCB走线推迟 + 时钟偏斜 > Th

即 Tco > Th – 外部PCB走线延时 + 最大时钟网络延时

其间,最小输出延时 = Th – 外部PCB走线延时 + 最大时钟网络延时

即 Tco > 最小输出延时

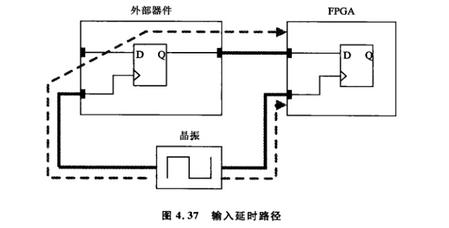

2、再来看输入模型

输入模型无非便是跟输出模型相反算了,本来FPGA作为输出,现在作为输入,仍是要考虑咱们之前静态时序剖析的时分推出的那两个公式

即 Tclk + 时钟偏斜 > Tco + 外部PCB走线延时 + Tsu

那么Tco + 外部PCB走线延时 + 时钟网络延时 < Tclk - Tsu,

小于号左面便是咱们的最大输入延时 ,这儿的Tco就不再是FPGA内部的了,而是数据经过SDRAM的延时了。Tclk便是FPGA的内部时钟了,Tsu当然也是FPGA的树立时刻。到了这个当地我就有点不懂了,已然是输入延时,为什么不把FPGA的树立时刻考虑在内呢?要知道咱们在推输出延时的时分也是把SDRAM的树立时刻考虑在内了啊,为什么这儿就不把FPGA的树立时刻考虑在内呢?

我是这么了解的,会不会是因为咱们只需求算数据到FPGA引脚的延时就能够了,剩余的途径,包含数据从FPGA引脚到数据被锁存这段时刻,也便是现已包含了FPGA的树立时刻在内了的原因,这段时刻是归纳东西依据咱们的输入延时来分配道路的。

这个问题,期望看到的大神给个定见吧

当然了,最小输入延时也是依据那个公式求得

即Tco + 外部PCB走线延时 +时钟网络延时 > Th

即最小输入延时 > Th

3、下面咱们做一个总结

最大输出延时 = 外部器材的Tsu + 外部PCB最大推迟 + 最大时钟网络延时

最小输出延时 = 外部器材的Th – 外部最小PCB走线延时 + 最大时钟网络延时

最大输入延时 = 外部器材最大Tco + 外部PCB最大走线延时 + 最大时钟网络延时

最小输入延时 = 外部器材最小Tco + 外部PCB最小走线延时 + 最小时钟网络延时

下面再来解说一下最大最小问题,看到这咱们肯有点看不懂了,方才还觉得能够,加了一些最大最小就看不懂了,其实咱们要做的输出,不仅仅是有一个引脚输出,拿咱们的SDRAM来说,有12根地址线,还有16根数据线还有其他的操控信号线要输出,那么,咱们应该选其间最长的,或许最短的来考虑,只需最长的或许最短的满意要求了,其他的天然也就满意要求了,即咱们用最坏的打算来考虑咱们的束缚途径。

还有最大最小时钟网络延时,因为这儿咱们只需一跟时钟线,就无所谓最大最小了,这么说便是为了标准

最大最小外部器材的Tco,数据经过SDRAM的时分,并不是时刻都是相同的,总有些快慢问题,这儿咱们也取极限,便是数据经过SDRAM的最大时刻和最小时刻,这个时刻在datasheet里边是有参数的

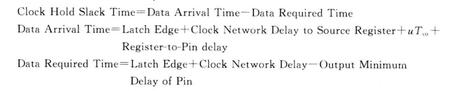

仔细的朋友或许会发现 最小输出延时核算的时分,为什么是减去 最小PCB走线延时呢,为什么不是最大?为什么不是加上最大时钟网络延时呢?为什么不是最小?其实,时序剖析东西剖析的时分是依照必定的公式核算数据抵达时刻和数据需求时刻的,这个公式见下图

在核算坚持时刻余量,数据需求时刻的时分,公式是减去 output minimum delay of pin

为什么是减去呢,按理说应该是加上咱们的输出最小延时才对,小墨其时也不了解,所以就当是记住吧,也便是说

这儿的 output minimum delay of pin = – 输出最小延时

这样了解的话,那么输出最小延时越大,那么output minimum delay of pin 就越小了,也便是为什么是减去最小PCB延时的原因吧

后边咱们到时序剖析东西里边看时序陈述图的时分就会发现,假如咱们束缚的最小输出延时是负数的话,里边显现的却是正数,所以,咱们就暂时记住好了,因为真的是欠好了解。

三、参数核算

依据咱们方才揣度出来的那几个公式,咱们就能够进行参数核算了,先来看看咱们需求什么参数

输出模型的时分,咱们需求的是SDRAM的树立时刻,坚持时刻,外部PCB走线延时,输入模型的时分,咱们需求的是外部器材的最大最小Tco

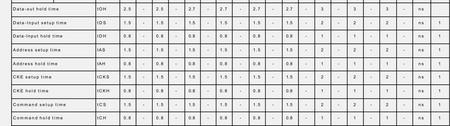

SDRAM的树立坚持时刻能够从datasheet里边找到

依据器材类型,咱们挑选树立时刻为 1.5 ns ,坚持时刻为 0.8ns,外部PCB走线延时这个不怎样好算,只能估量吧,因为板子不是我画的,长度也不知道,依据经历,咱们知道,信号在PCB上的延时大约为0.18ns /1000mil,那我就估量为最大0.3ns,最小0.1好了

然后是时钟网络延时,也便是源时钟抵达源寄存器 – 抵达意图寄存器的值,因为咱们的时钟是总PLL宣布的,时钟从FPGA管脚输出后再送给SDRAM,因而这个值必定是负值,并且也是时钟在PCB上的走线延时,这个值咱们预算为-0.1ns好了,因为真的无法算我觉得。

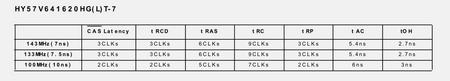

然后是数据经过外部器材的最大最小延时,这个值咱们在SDRAM的理论篇里边说了,便是Tac参数和Toh参数,不懂得朋友能够到前面去补补课,这个值咱们在datasheet里边也找得到

所以咱们取最大Tco 为5.4ns 最小Tco为2.7ns

经过核算得咱们的束缚参数

最大输出延时 =外部器材的Tsu+外部PCB最大推迟+最大时钟网络延时

=1.5+0.3-0.1=1.7ns

最小输出延时 = 外部器材的Th – 外部最小PCB走线延时 + 最大时钟网络延时

= -(0.8 – 0.1 – 0.1 ) = – 0.6ns

最大输入延时 = 外部器材最大Tco + 外部PCB最大走线延时 + 最大时钟网络延时

= 5.4 + 0.3 – 0.1=5.6ns

最小输入延时 = 外部器材最小Tco + 外部PCB最小走线延时 + 最小时钟网络延时

= 2.7 + 0.1 -0.1 = 2.7ns

四、大局时钟束缚

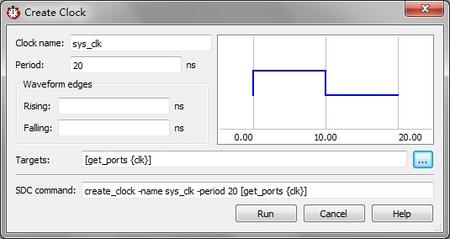

因为咱们的时钟是由晶振源传到PLL,然后再由PLL输出给SDRAM和FPGA内部寄存器的,因而咱们需求对输入的时钟进行束缚,束缚其为50M的时钟,并对应好咱们的端口时钟clk,即束缚咱们的输入时钟为50M,并给这个时钟取一个在时序剖析时钟的姓名,即sys_clk,关于timequest的运用,咱们还需自行学习,这儿仅仅只是说束缚办法

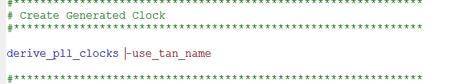

而关于PLL输出时钟的束缚,咱们仅需在.sdc文件相应的的方位,手动输入束缚即可,仅需求一条句子 ,这条指令输进去今后,时序剖析东西会主动的为咱们束缚好PLL的输出时钟

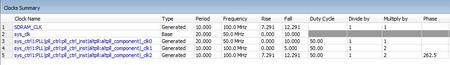

咱们能够经过检查时序陈述,能够看到,咱们的时钟都跑到了咱们束缚的条件,假如咱们不加这条句子的的话,那么PLL的输出时钟是达不到这个要求的,那样的话,咱们的时钟都不安稳,更别提体系安稳性了

五、关于虚拟时钟

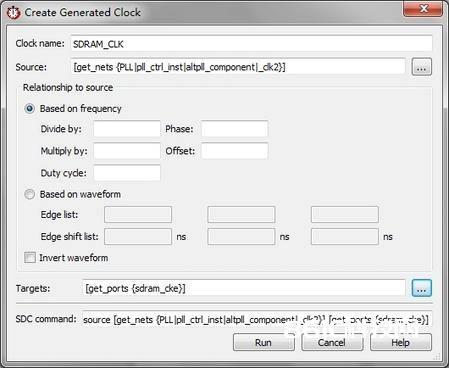

上图中,仔细的朋友或许会看到,榜首行有一个SDRAM_CLK,这个时钟是怎样来的呢?这个时钟,其实便是咱们给外部的芯片模仿了一个时钟,因为外部器材的时钟是咱们PLL生成,送到外部管脚去的,并不是咱们FPGA的内部时钟,已然不是内部时钟,那么咱们就无法对其进行束缚,咱们只能界说这么一个虚拟的时钟,来尽或许模仿SDRAM的作业时钟。 例如,输入的时分,源寄存器在SDRAM中,意图寄存器在FPGA中,数据的传输是在SDRAM作业时钟下进行的,可是时序剖析东西不知道这个时钟,所以咱们界说一个虚拟时钟,连接好它的途径,即从哪输出,输到哪,这儿的话便是从PLL的clk2输出,到SDRAM的时钟输入引脚了。因为这儿是时序束缚模型为源同步时序模型,即时钟都是由FPGA发生,在不是源同步时序模型的状况下,就不需求指明虚拟时钟的源和意图,只需求指明周期即可。

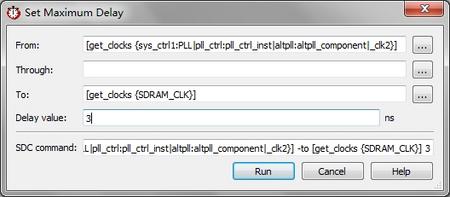

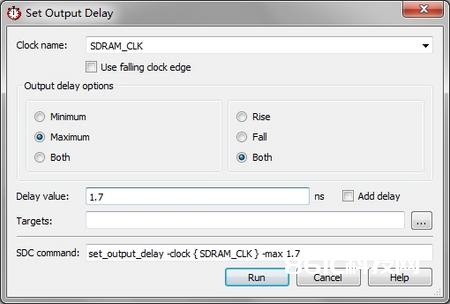

已然是模仿,那咱们也应该考虑到这个时钟从PLL输出,到FPGA引脚的这段时刻的延时,咱们对其进行最大,最小延时束缚

同理,咱们束缚最小值为0ns,这儿就不做演示了,办法是相同的

六、I/O时序束缚

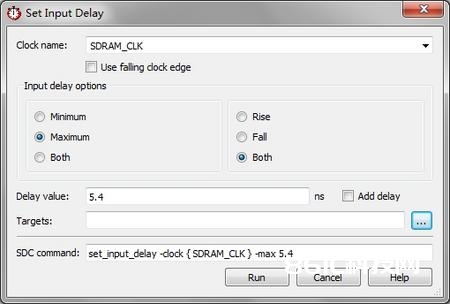

因为篇幅所限,这儿就不能一点点的做了,只举个比如吧,做最大输入延时的束缚,咱们点击 constraints ———> set input delay

时钟姓名咱们选的便是咱们生成的虚拟时钟,为什么呢?因为咱们做的是IO束缚,即FPGA和SDRAM相互交流数据,已然交流数据肯定是树立在时钟的基础上的,这个时钟,便是虚拟时钟。这个当地比较难懂了,我了解的也不是太好。究竟咱们是要看得是时序陈述,时序陈述便是树立在虚拟时钟的基础上的一个模仿进程。先了解到这儿吧,也不知道该怎样解说了,还请看到的大神给点拨一二吧~

下面咱们做最大输入延时的束缚,设置咱们最大的输入延时为5.4ns

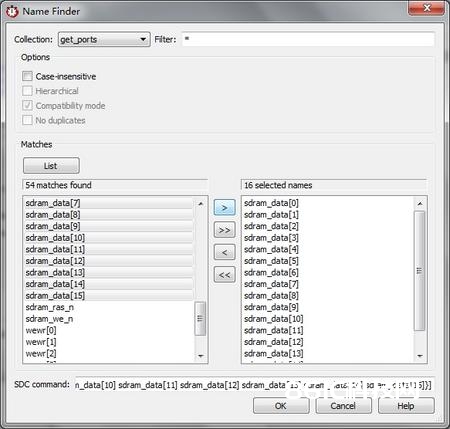

设置输入途径,因为只需SDRAM_data途径是双向的,做输入的时分仅考虑这个途径即可

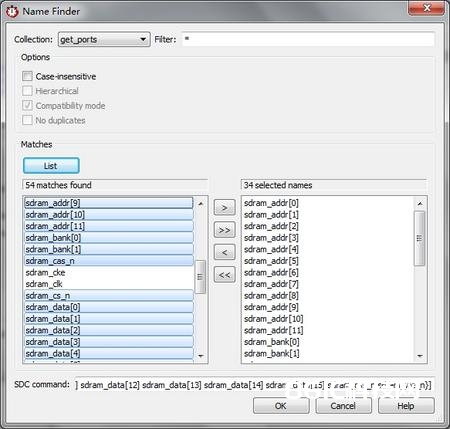

然后咱们再做一个输出最大延时的束缚,输出最大延时为1.7ns ,输出途径包含除了时钟和时钟有用信号sdram_cke信号外的一切的SDRAM引脚,当然也包含sdram_data信号,为什么不包含cke信号呢?因为cke信号从头到尾没有多少次的改变,也便是说对时序要求不严厉,关于这种信号,相似还有片选信号,数码管片选,位选等,咱们只需对其进行false途径束缚即可,即对时序没有严厉要求的途径

剩余的途径我就不再做了,都是相同的,将一切途径束缚好之后,咱们需求开端调sdram作业时钟的相位偏移了

因为篇幅所限,剩余的内容我放到下篇中讲,谢谢咱们~