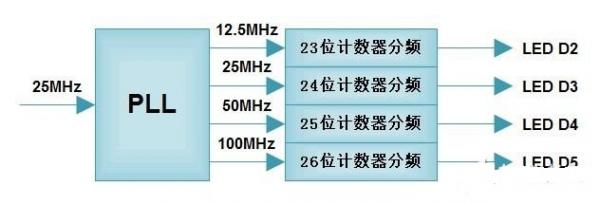

如图8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,装备PLL使其输出4路别离为12.5MHz、25MHz、50MHz和100MHz的时钟信号,这4路时钟信号又别离驱动4个不同位宽的计数器不断的计数作业,这些计数器的最高位终究输出用于操控4个不同的LED亮灭。因为这4个时钟频率都有必定的倍数联系,所以咱们也很简单经过调整合理的计数器位宽,到达4个LED闪耀共同的操控。

cy4.v模块代码解析

先来看cy4.v模块的代码,它是工程的顶层模块,主要做接口界说和模块例化,一般不会在这个模块中做任何的详细逻辑设计。

首先是接口部分,只要时钟、复位和8个LED信号。

module cy4(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有用

output[7:0] led //8个LED指示灯接口

);

接着这儿声明5个wire类型的信号,一切在不同模块间接口的信号,在它们的上级模块中都有必要界说为wire类型,这儿有4个不同频率的时钟以及由PLL的lock信号引出的复位信号sys_rst_n。

wire clk_12m5; //PLL输出12.5MHz时钟

wire clk_25m; //PLL输出25MHz时钟

wire clk_50m; //PLL输出50MHz时钟

wire clk_100m; //PLL输出100MHz时钟

wire sys_rst_n; //PLL输出的locked信号,作为FPGA内部的复位信号,低电平复位,高电平正常作业

PLL是咱们装备的IP核模块,它需要在咱们的代码中例化,如下所示。

//————————————-

//PLL例化

pll_controller pll_controller_inst (

.areset ( !ext_rst_n ),

.inclk0 ( ext_clk_25m ),

.c0 ( clk_12m5 ),

.c1 ( clk_25m ),

.c2 ( clk_50m ),

.c3 ( clk_100m ),

.locked ( sys_rst_n )

);

终究4个LED闪耀操控模块的例化,它们的源码都是led_controller.v模块,但它们的称号不相同,别离为uut_led_controller_clk12m5、uut_led_controller_clk25m、uut_led_controller_clk50m、uut_led_controller_clk100m。这样的界说方法终究完成作用不同于软件的函数调用,软件的函数调用只要一个函数,分时复用;而FPGA的这种代码例化却会完成4个彻底相同的硬件逻辑。当然了,这4个模块还略有不同,便是两个称号中心的“#(n)”,n有23、24、25和26,这个是输入到led_controller.v模块的一个参数,咱们别急,后边咱们立刻就会说到它。

//————————————-

//12.5MHz时钟进行分频闪耀,计数器为23位

led_controller #(23) uut_led_controller_clk12m5(

.clk(clk_12m5), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有用

.sled(led[0]) //LED指示灯接口

);

//————————————-

//25MHz时钟进行分频闪耀,计数器为24位

led_controller #(24) uut_led_controller_clk25m(

.clk(clk_25m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有用

.sled(led[1]) //LED指示灯接口

);

//————————————-

//25MHz时钟进行分频闪耀,计数器为25位

led_controller #(25) uut_led_controller_clk50m(

.clk(clk_50m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有用

.sled(led[2]) //LED指示灯接口

);

//————————————-

//25MHz时钟进行分频闪耀,计数器为26位

led_controller #(26) uut_led_controller_clk100m(

.clk(clk_100m), //时钟信号

.rst_n(sys_rst_n), //复位信号,低电平有用

.sled(led[3]) //LED指示灯接口

);

//————————————-

//高4位LED指示灯封闭

assign led[7:4] = 4'b1111;

endmodule

led_controller.v模块代码解析

led_controller.v模块代码如下,这儿要点留意咱们上面刚刚说到的输入参数。在代码中,有“parameter CNT_HIGH = 24;”这样的界说,若是例化这个模块的上层接口中不界说“#(n)”,则表明“parameter CNT_HIGH = 24;”句子收效,若是界说的“#(n)”中的n值与代码中界说的24不同,那么以n为终究值。

module led_controller(

input clk, //时钟信号

input rst_n, //复位信号,低电平有用

output sled //LED指示灯接口

);

parameter CNT_HIGH = 24; //计数器最高位

//————————————-

reg[(CNT_HIGH-1):0] cnt; //24位计数器

//cnt计数器进行循环计数

always @ (posedge clk or negedge rst_n)

if(!rst_n) cnt <= 0;

else cnt <= cnt+1'b1;

assign sled = cnt[CNT_HIGH-1];

endmodule