导言

在信号传输范畴占控制位置的高速串行体系速度正不断创新:USB3.0的5Gbps数率比起USB2.0的480Mbps而言进步了10倍,PCI Express总线在几年之内也从开始的2.5Gbps扩展到8Gbps,数据存储范畴的SATA和SAS也现已进化到第三代6Gbps,还有DDR内存总线、以太网、HDMI、DisplayPort等等均无一破例的进步速度至更高水平。推进串行数据率不断攀升的动力来自于互联网年代的生计规律:快鱼吃掉慢鱼,而非大鱼吃小鱼。

职业的开展和技能的前进离不开规范的拟定,为确保各厂家制作的产品能满意互操作性,即能彼此兼容,各职业安排为此都拟定了一套测验规范,要求厂家出产的产品有必要经过测验后方能上市出售,这便是一致性测验(Compliance Testing),比方USB-IF担任拟定USB2.0和USB3.0的一致性测验规范,PCI-SIG担任PCI Express G1 /G2/ G3一致性测验规范。虽然各种串行协议的具体内容千差万别,但一致性测验的结构和思路都是相似的,涉及到的共性问题都包含测验仪器的挑选,规范测验报文的生成、测验夹具的运用、怎么判别测验项目合格,甚至终究测验报告的生成。

关于5Gbps速率以下的信号而言,由于setup time和hold time的窗口margin较大,一般只需考虑发送端测验即可,而关于5Gbps速率以上超高速信号,由于自身margin就较小,再加上高频重量在信道传输时衰减相对更大,到接纳端时呈现误码的概率也就增大许多。发送端能经过一致性测验,送出的信号质量也很好,并不表明接纳端就必定不会呈现误码。为了应对这么高数据率的应战,新一代串行协议比方USB3、SATA3都规则接纳端容限测验已不再是可选项,而是必测项目。串行信号速率进步之后带来的别的一类问题是电缆、探头、测验夹具或背板(可统称为信道channel)的影响已不行疏忽,需求有某种方法来补偿信道对信号的衰减效应,这也体现在下一代串行协议的一致性测验规程中。

发送端测验

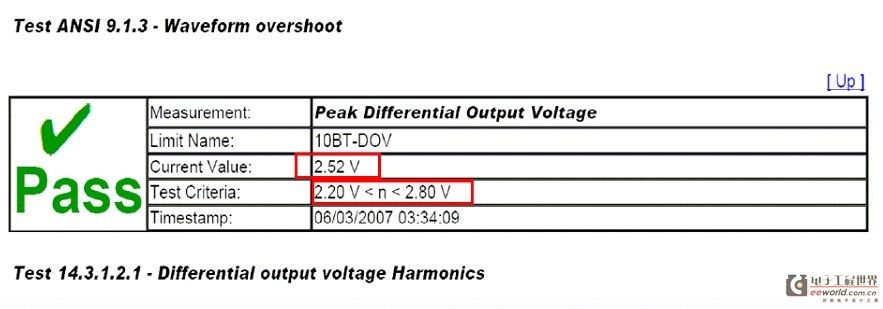

对Transmitter测验主要由示波器或专门的串行数据剖析仪SDA完成,高保真复原信号需求能收集到5次谐波重量,对应的示波器带宽最低要求为数据率的2.5倍,比方USB3.0测验要求示波器带宽为12.5GHz以上,SATA 6G要求15GHz带宽以上,而做较低速的PCI E G1就不需求这么高带宽,6GHz带宽即满意。力科公司的SDA 8Zi是新一代更高速串行信号发送端测验的最佳渠道,由于它能供给从4GHz到30GHz带宽规模,最高80GS/s采 样率,彻底能应对当时最快速串行信号的带宽需求。各种协议的发送端测验项目不尽相同,但大都可分为三类:时序特性、电气特性和时钟特性。时序测验从单个样 本来说便是树立时刻和坚持时刻的测定,从大样本的核算视点来说,便是眼图模板和颤动剖析。一致性规范都会界说某个参数的合格规模,比方下图1所示为百兆以太网峰值差分输入起伏,测验规范为2.2伏至2.8伏之间,实测值为2.52V,契合规范要求,所以是合格的。

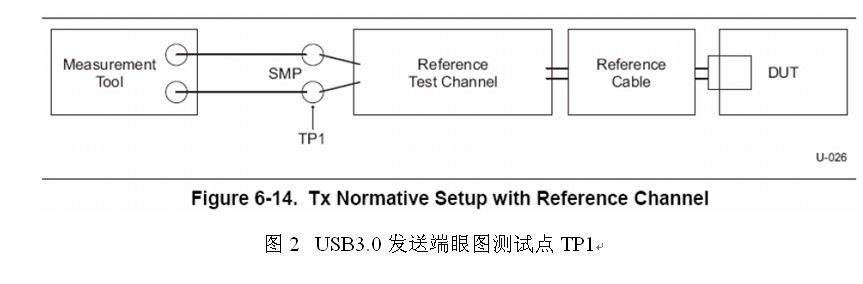

损耗和反射,背板、电缆对信号起伏的衰减和对相位的畸变,不然眼图和颤动剖析成果与实际情况差之千里。在USB3.0的发送端眼图中,丈量的是待测验信号经过参阅测验信道后TP1点的眼图和颤动。如下图2中的Reference test channel即为参阅测验信道,在规范中界说了long channel、short channel和3米电缆三种参阅测验信道。假如运用long channel或许较长电缆,信号抵达接纳端时衰减比较大,眼图现已闭合,USB3.0芯片接纳端运用了CTLE均衡器对信号进行均衡后,信号眼图的质量将大大改进,对应的测验仪器要求能仿真剖分出CTLE均衡器处理后信号的眼图和颤动。

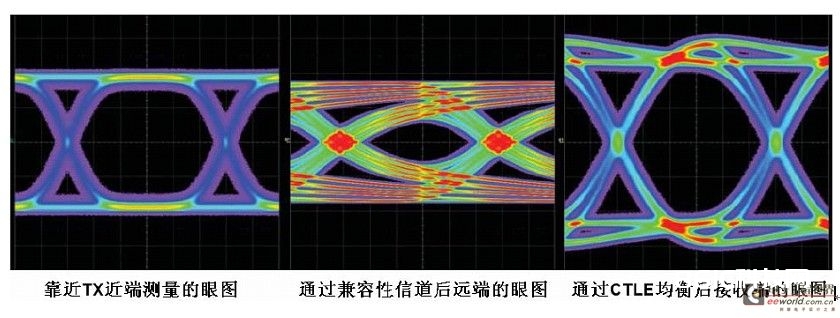

上图是力科Eye Doctor II软件对USB3.0 Tx波形运用CTLE均衡后的成果,左面的眼图是接近TX近端丈量到的眼图;中心的眼图是经过兼容性信道(参阅测验信道)后丈量的眼图,可见眼图的打开程度较小,颤动较大;右边的眼图是仿真CTLE均衡后的眼图,可见眼高和颤动都得到改进。信号越高,越需求对信号进行均衡处理。基于此,USB3.0、SATA III、PCI-E G2都规则一致性测验有必要包含均衡仿真功用。而力科Eye Doctor II软件供给CTLE、FFE 、DFE三种最盛行的均衡算法,能全面满意下一代串行信号的发送端测验需求。

接纳端容限测验

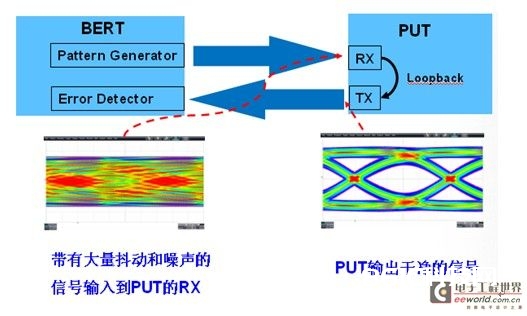

许多工程师认为在接近接纳端丈量眼图或颤动便是Receiver测验,这是个误解,形成这种误解的原因主要是在过去接纳机测验在板级的硬件研制中不是必测项目。接纳机测验的精确界说为:Recevier能够忍受的不发生误码的输入信号最大颤动值。下图为接纳机测验的示意图。所需的仪器包含误码率测验仪(简称BERT),BERT一般包含码型发生器(Pattern Generator)和误码检测器(Error Detector)两部分。在接纳机测验时,码型发生器输出特定码型的、带有很多颤动和噪声的信号到PUT的RX,DUT接纳到后经过时钟与数据恢复电路(简称CDR)、判别电路和解码得到1和0组合的比特流,然后环回到输出寄存器,从PUT的TX缓冲器发送出去,PUT的TX衔接到了BERT的误码检测器,误码检测器中的CDR、判别电路处理后解码得到1与0组 合的数据比特流,然后与码型发生器输出的特定码型数据比照,假如两者彻底符合则没有误码,不然,记载下误码的数量和接纳到的码流的比特总数,前者除以后者 即误码率,一起记载接纳到误码时码型发生器输出信号的颤动值。修正码型发生器输出信号的随机颤动、固有颤动、信号起伏等参数,能够快速评价PUT的接纳机对颤动的容限功能。

在接纳机容限测验中,需求处理因SKP码型带来的误码率核算错误问题。一般为了补偿链路两头频率误差,发送端在数据流中每354个symbol要刺进两个SKP(即K28.1码),接纳端需求能辨认和删去SKP,这是USB3.0、SATAIII 或PCI Express G3等新式协议才具有的特色,而传统的BERT由于不能辨认SKP码,会将正确码流误认为误码。力科的误码率剖析仪PeRT3由于具有协议层通讯才能,能够智能的增加和删去SKP后,再来核算是否有误码,所以是业界仅有一款能真实进行接纳端容限测验的误码率剖析仪。

生成规范测验报文

简直一切的串行数据一致性测试规程都要求DUT能宣布规范的测验序列,并且每一个测验项目对应的测验报文都不尽相同。一般芯片厂家都会供给相应的软件程序控制芯片进入测验形式,发生特定的测验报文。比方Intel的LanConfig软件适用于一切Intel的网卡芯片,工程师能够经过该软件修正网卡芯片寄存器使其进入百兆测验形式或千兆Mode 1,2,3,4形式中的一种。再比方USB-IF供给的HSElectricalTestTool发包程序(可从www.usb.org下载),能够针对Host或Device的不同测验项目宣布不同的测验报文。比较其他协议,USB3.0规范报文是最杂乱的。在USB3.0规范中界说CP0-CP8九种测验码型。在TX测验中,需求用到CP0/CP1/CP7/CP8四种码型:CP0用于眼图与颤动、共模电压丈量;CP1用于SSC展频丈量、随机颤动丈量;CP7用于去加剧丈量;CP8用于差分电压起伏丈量。关于测验工程师而言,假如没有厂家供给的发包程序,很难让DUT宣布不同的测验码型,而力科的PeRT3则能够很好处理这个问题,由于其具有协议层通讯才能,会宣布Ping.LFPS指令到DUT,DUT每接纳到1个Ping.LFPS后,输出的码型就切换一次,从CP1到CP2,CP2到CP3, 直到CP8后再切换回CP0,不具有协议层通讯才能的信号源是很难进行USB3.0、SATAIII、PCIe G3等下一代高速数据的一致性测验的。

结语

串行数据率在进步到5Gbps以上后,需求有全新的一致性测验思路和手法,仅仅在发送端做眼图和测验现已不行,还需求引进接纳机颤动容限测验、均衡仿真等,一起还有必要支撑与DUT链路层通讯的才能以生成杂乱的规范测验码型。力科PeRT3是业界仅有具有链路/协议层会话才能的误码率剖析仪,与高功能的串行数据剖析仪SDA 8Zi合作运用,能够为最新串行协议USB3.0、SATA III、SAS III、PCI Express G3等供给完好的端到端一致性测验处理方案。