异步周期完毕方法

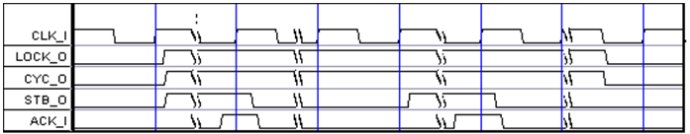

块读/写操作每次读/写数据屡次。块读/写操作实际上是由次序进行的多个单次读/写操作组合而成的。在一起存在多个主设备时,块读/写操作十分有用,一个块读写一般是不能打断的,比方一次DMA,如图9所示,在一次块操作中,CRC_O信号有必要坚持为高。一起为了确保整个块操作不被打断,LOCK_O也能够置为高,可是LOCK_O不有必要为高。典型地,主设备进行一次DMA接连传输4个或许8个总线宽度单位的数据,然后自动开释总线,其后又企图占用总线从头进行DMA,直到一切的数据都传输完毕。这样做的优点是答应其他优先级更高的主设备在两次DMA之间刺进操作以完结愈加紧迫的使命。

图1Wishbone总线块操作中CYC_O信号的用法

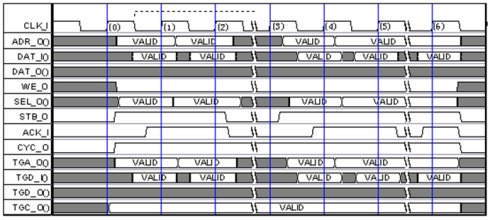

块读操作如图2所示。块操作最多能够在每个时钟周期进行一次数据读或许写,可是主设备和从设备都能够经过刺进等候周期操控块操作的速度。一次块操作包含屡次子操作。每一次子操作都是块操作的一个阶段,完结一次数据读或许写。图10的块操作由五次读操作完结,其进程如下:

在时钟上升沿0,主设备将地址信号ADR_O()、TGA_O()放到总线上,将WE_O置为低标明读操作,将恰当的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位,将CYC_O和TGC_O()置高标明操作正在进行,将STB_O置高标明一次子操作开端。CYC_O和TGC_O()从无效变为有用能够产生在上升沿0曾经的任何时刻。

在时钟上升沿1抵达之前,从设备检测到主设备建议的操作,将恰当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的呼应。

在时钟上升沿1,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完结榜首次子操作。主设备将新地址信号ADR_O()、新TGA_O()放到总线上,将新的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位。

在时钟上升沿2抵达之前,从设备检测到主设备建议的第2次操作,将恰当的数据放到主设备的DAT_I()和TGD_I(),持续将主设备的ACK_I置高。

在时钟上升沿2,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完结第2次子操作。主设备将STB_O信号置低标明刺进等候周期。

在时钟上升沿3抵达之前,从设备检测到STB_O信号为低,将ACK_I置低。

在时钟上升沿3,主设备建议第三次操作,将新的地址信号ADR_O()、新的TGA_O()放到总线上,将WE_O置为低标明读操作,将恰当的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位,将STB_O置高标明第三次子操作开端。

在时钟上升沿4抵达之前,从设备检测到主设备建议的第三次子操作,将恰当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的呼应。

图2Wishbone总线的块读操作(异步周期完毕方法)

在时钟上升沿4,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完结第三次子操作。主设备一起建议第四次子操作,将新地址信号ADR_O()、新TGA_O()放到总线上,将新的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位。

在时钟上升沿5抵达之前,从设备检测到主设备建议的第四次子操作,将恰当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的呼应。

在时钟上升沿5,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,完结第五次子操作。主设备一起建议第六次子操作,将新地址信号ADR_O()、新TGA_O()放到总线上,将新的SEL_O()信号置高告诉从设备将数据放在数据总线的恰当方位。

在时钟上升沿5往后,从设备检测到主设备建议的第五次子操作,可是因为数据没有预备好,它在新上升沿抵达之前将ACK_I信号置低标明刺进等候周期。

上升沿5和6之间被刺进了多个等候周期。当从设备预备好数据,在时钟上升沿6抵达之前,将恰当的数据放到主设备的DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的呼应。

在时钟上升沿6,主设备发现ACK_I信号为高,将DAT_I()和TGD_I()采样,并将STB_O和CYC_O置为低标明整个块读操作完结。从设备发现STB_O置低后,也将主设备的ACK_I置低。

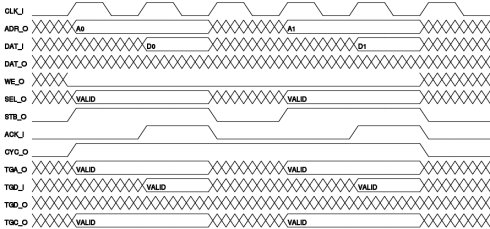

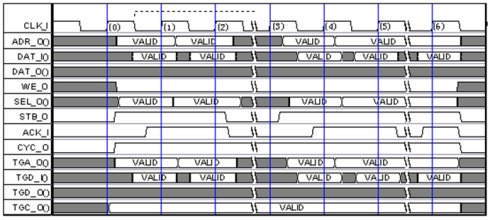

同步周期完毕方法

图3Wishbone总线的块读操作(同步周期完毕方法)

在时钟上升沿0:

- Master在[ADR_O()]和[TGA_O()]宣布有用的地址

- Master拉低[WE_O],标明是一个读周期

- Master宣布有用数据挑选信号[SEL_O()]标明哪些数据是有用的

- Master宣布[CYC_O]和[TGC_O()]标明总线周期的开端

- Master宣布[STB_O]标明操作的开端

留意:Mater有必要在时钟上升沿1或之前宣布[CYC_O]和/或[TGC_O()]

在时钟上升沿1:

- Slave检测到主设备建议的操作,宣布[ACK_I]

- Slave在[DAT_O]和[TGD_O()]宣布有用的数据

- Slave宣布[ACK_I]应对[STB_O],标明数据有用,能够读取数据了

- Master发现[ACK_I],预备锁存[DAT_I]和[TGD_I()]

在时钟上升沿2:

- Master锁存[DAT_I]和[TGD_I()]

- Master拉低[STB_O]刺进等候周期(-WSS-)

在时钟上升沿3:

- Master在[ADR_O()]和[TGA_O()]宣布有用的地址

- Master拉低[WE_O],标明是一个读周期

- Master宣布有用数据挑选信号[SEL_O()]标明哪些数据是有用的

- Master宣布[STB_O]标明操作的开端

在时钟上升沿4:

- Slave检测到主设备建议的操作,宣布[ACK_I]

- Slave在[DAT_O]和[TGD_O()]宣布有用的数据

在时钟上升沿5:

- Master锁存[DAT_I]和[TGD_I()]

- Master拉低[STB_O]和[CYC_O],完毕总线周期

声明:本文内容来自网络转载或用户投稿,文章版权归原作者和原出处所有。文中观点,不代表本站立场。若有侵权请联系本站删除(kf@86ic.com)https://www.86ic.net/yingyong/5g/232820.html