处理器内部集成的硬件加速器能够完结三种广泛运用的信号处理操作:FIR(有限冲激响应)、IIR(无限冲激响应)和FFT(快速傅里叶变换)。硬件加速器减轻了核处理器的担负,能潜在的进步处理器的核算吞吐率超越两倍。本文以下一代音频体系为例,阐明硬件加速器在这方面的运用。

1 为什么运用硬件加速器

FIR滤波器、IIR滤波器和FFT操作在数字信号处理器中运用十分遍及,且具有规矩的结构,因而能够用硬件直接完结,特别是用硬件加速器。硬件加速器是专用的定点功用外设,用于完结重复核算杂乱的单个使命。它们减轻了主处理器的担负,主处理能够首要做一些在结构上简直没有什么规则的通用使命。

因为体系规划者既具有通用处理器的灵活性,又具有专用硬件的核算优势,因而,运用硬件加速器就供给了一种高性价比的办法,以添加处理器总的核算才干。

因而,这类加速器在满意很多运用领域日益杂乱的体系需求方面具有重要价值。其间一个运用是其通道数不断上升的音频体系。家庭影院体系通道数从5.1通道开展到6.1通道,现在现已到 7.1通道,而高端轿车功放一般运用12个或许更多的扬声器,使听者沉浸于美好的音乐中。

此外,音频源内容现在选用高清(HD)格局,其相关的解码器扩展了体系资源。HD算法还以更高的采样率处理数据。曾经,数据的峰值采样率很少超越48 kHz,有了HD算法,现在采样率一般都是96kHz,有时,乃至到达了192kHz。

为了更好的了解是怎么添加核算需求的,以现代化的家庭影院接纳体系为考虑,它集成了杂乱的室内均衡算法,用以补偿驱动响应和扬声器摆放方位的不同所引起的误差。算法首要运用麦克风剖析室内环境,并丈量实时传递函数。在多个方位进行丈量再组合剖析,然后为每个扬声器规划一个补偿滤波器。

更准确的室内均衡算规律运用FIR滤波器来校对整个频率范围上的响应函数,滤波器长度与采样率直接成份额。低频操控越准确,需求滤波器长度越长。采样率为48kHz,一般滤波器长度为256点,为了到达相同的频率分辨率,在96kHz则需求滤波器长度为512点。采样率和滤波器长度都加倍则导致所需的总核算量添加了四倍。

2 加速器结构

本节将以ADI公司近期推出的SHARC ADSP-2146x处理器为例介绍加速器的结构,该处理器具有更高的时钟速率(450MHz),并扩展了片上存储器(5Mb)。

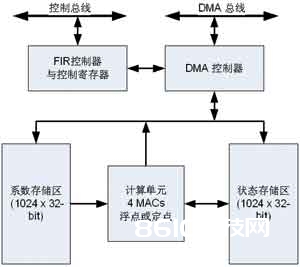

图1 FIR加速器的结构

此外,处理器还具有一系列硬件加速器,能够用以完结通用信号处理运算:FIR、IIR滤波器和FFT。而这些运算是通讯体系、医疗设备、消费产品和工业丈量与操控运用中的根本运算。这些加速器是SHARC ADSP-2136x系列处理器片内采样率转换器的有利弥补,而采样率转换器也能够看作硬件加速器。

SHARC ADSP-2146x处理器的三个加速器规划相同,图1所示的FIR加速器能很好的阐明硬件加速器的结构。

FIR加速器有以下功用模块。

● 系列操控寄存器——装备加速器的操作。

● DMA操控器——在主存储器与加速器的本地存储器之间传输数据,也能够用于装备操控寄存器。

● 两个本地存储器块——保存系数和状况变量(或许推迟存储器),并下降主存储器的带宽。

● 核算单元——包含合适加速器的算术操作,FIR的核算单元有4个并行的MAC。

运用链式DMA,加速器的操作能够主动完结,FIR加速器的典型操作有以下几步。

(1)将本通道的系数数据由内部存储器载入本地加速器系数存储区。

(2)将本通道的状况变量从内部存储器载入本地加速器系数存储区,这包含第一个输入样本。

(3)运用四个MAC单元核算输出样本。

(4)保存成果。

(5)假如还有需求处理的样本,则读取下一个输入样本,并写入状况变量存储器。

(6)重复过程(3)~(5),直到通道中的一切输出样本核算完。

(7)重复过程(1)~(6),核算一切输入通道。

3 加速器的实践运用

规划的运用软件有必要尽可能从硬件加速器获取最多的优点,应紧记加速器有必要装备成与主CPU并行操作,假如主CPU处于闲暇状况等候加速器操作完结,这不会带来任何优点。

加速器是实时环境中运转的大信号链的典型部分,与加速器接口需求双缓存的输入和输出数据,且体系规划人员也应该紧记加速器会带来一部分延时。

想象一个带有7.1通道的家庭影院体系,采样率96kHz,数据块巨细为32个采样点,假定室内均衡运用8个FIR滤波器,每个滤波器长度为512点,假如选用核CPU履行滤波操作,则至少需求每秒96kHz ×8×512=393MMAC个操作,或许占作业在450MHz的SHARC处理器运算量的44%。该FIR处理占了整个核算量的很大一部分,但在将来,这些都能够转由加速器来处理。FIR滤波器的输入和输出都选用双缓冲,这样就能够让加速器与音频信号处理链的最终环节并行处理。当然,双缓冲器会引进32个采样点的处理推迟,关于96kHz时推迟为333ms,是能够承受的。

而运用前面的核算公式,加速器需求50 056个外设时钟周期才干完结操作,假如外设时钟是225MHz,则需求223ms,这小于333ms的可用块处理时刻。

4 定论

音频处理技能的进一步开展对音频DSP提出了更高的要求,集成的硬件加速器为处理器全体处理功能的进步供给了重要的推动力,且将通用的信号处理操作——FIR滤波、IIR滤波和FFT操作——从内核处理器中释放出来,使内核能够专心于其他使命,这种高性价比的办法能进步处理器两倍以上的核算吞吐量。尽管本文首要评论音频运用,可是处理器核和加速器也是通用的,也十分合适于各种信号处理使命。