摘要:文中以TI公司的C5000系列通用型DSP芯片TMS320VC5509为中心,完结音频解码体系硬件渠道的规划与完结,并研讨MP3的解码算法以及其在该硬件渠道上的完结。整个体系的硬件渠道包含DSP中心模块、FLASH存储器、音频CODEC,电源等模块。该体系通过USB接口与核算机通讯,下载MP3格局的数据流,并将其存储在Flash中,然后由DSP读取FLash中的MP3数据流,完结解码作业,并通过CODEC播映。一起能够对DSP进行其他解码算法的软件编程,完结多种数据流格局的音频编、解码,具有很强的软件晋级灵敏性,还处理了低功耗的问题。

关键词:MPEG;音频解码;DSP;低功耗

MPEG(活动图画专家小组)是ISO/IEC安排的一个作业小组,担任制定有关活动图画、音频及其组合的紧缩宽和紧缩处理等方面的技能规范。MPEG-1 Layer3(即MP3)是MPEG-1世界音频规范(ISO/IEC 11172)中的第三层编、解码算法,它具有紧缩比高、声响复原质量好、算法杂乱度适中等长处,选用这种规范制造的MP3格局的音乐在数字音频的存储、互联网上的多媒体音频传输等范畴得到了广泛运用。

现在依据专用芯片的音频编解码计划软件晋级灵敏性不高,依据DSP的音频编解码计划又多依据C54x渠道,而处理低功耗的技能办法是值得研讨的问题。

依据上述布景,文中提出了依据DSP的音频解码体系的研讨与完结这一处理计划。本课题的首要意图是:以TI公司的C5000系列通用型DSP芯片TMS320VC5509为中心,完结体系硬件渠道的规划以及MP3的解码算法在该硬件渠道上的完结。整个体系的硬件渠道包含DSP中心模块、FLA SH存储器、音频CODEC,电源等模块。该体系通过USB接口与核算机通讯,下载MP3格局的数据流,并将其存储在Flash中,然后由DSP读取Flash中的MP3数据流,完结解码作业,并通过CODEC播映。一起能够对DSP进行其他解码算法的软件编程,完结多种数据流格局的音频解码,具有很强的软件晋级灵敏性,还处理了低功耗的问题。

1 硬件渠道的总体规划

现在业界对MP3解码体系的处理办法有两个计划:一是运用将解码算法固化到集成电路中去的专用芯片,这些芯片将一些片外资源集成到芯片内部,能够简化MP3解码体系完结所需的片外电路,便于整个体系的开发,但因为其算法固化到芯片内部,不能通过软件晋级,并且此类芯片遍及价格偏高。别的一个计划,便是运用通用的DSP来完结MP3解码体系,这种处理计划对规划人员的软硬件技能提出了很高的要求,不过其有很好的晋级特性,并且能够更便利的改善和优化解码算法,然后得到更好的音质回放作用,并且和第一种处理计划相同,其功耗比较低。

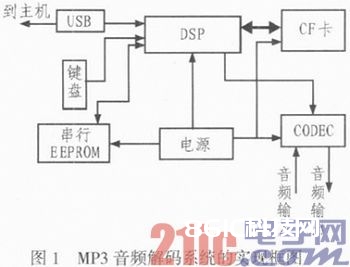

归纳各方面的好坏条件,咱们挑选了第二种处理计划,即依据通用DSP芯片来完结整个解码体系的硬件渠道。其硬件体系完结框图如图1所示。

这个框图大致的画出了解码体系的根本组成部分。在图中,咱们选用了512 k的串行EEPROM芯片用于完结bootloader,用CF卡存储MP3音乐及解码程序。中心的处理器选用了TI公司的TMS320VC5509 DSP芯片,考虑到其内部的RAM容量有256 kB,而咱们的程序巨细为80 kB,因而咱们在此规划中没有外扩RAM。

整个硬件渠道的作业流程如下:首要通过USB接口,从PC机中仿制MP3音乐,复制在大容量CF卡中。然后DSP读取CF卡的MP3数据进行解码,复原出PCM信号,再通过DSP的多通道带缓冲串口(McBSP)传送给音频CODEC芯片,终究播映出MP3音乐。

1.1 硬件渠道的详细完结

1.1.1 中心DSP芯片介绍

本计划选用的TMS320C55x系列是TI公司推出的继C5000系列C5x、C54x后的新式产品。它选用了增强型的哈佛结构,具有专门的硬件乘法器,运用流水线操作,供给特别的DSP指令,可用来快速地完结各种数字信号处理算法。为便利实践中的运用,C55X系列DSP具有各自不同的硬件结构,如在片存储器和片上外设等,可依据性价比和不同的运用场合灵敏选用。因为选用了高度并行硬件结构、模块化规划,使得C55X系列DSP具有功耗低、速度快等长处。首要用在音频紧缩、无线通讯等范畴。

与5000系列其他芯片比较,TMS320VC5509以其独有高性能低功耗和低价格特性,使得一推出就遭到业界用户的欢迎。

1.1.2 与核算机的接口规划

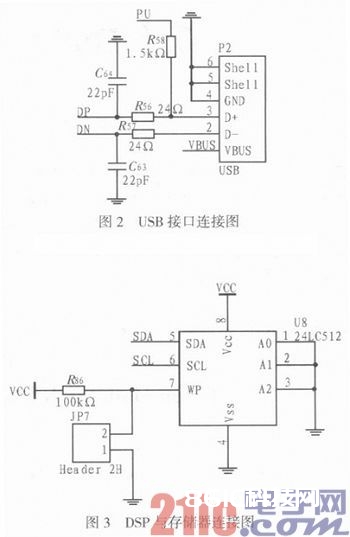

与核算机的接口规划运用的是当今十分盛行的USB接口,完结从核算机下载数据,5509自带的USB接口完全符合USB2.0全速接口规范,可与任何外部微操控器完结高速并行接口(12M比特/秒)。

1.1.3 存储器规划

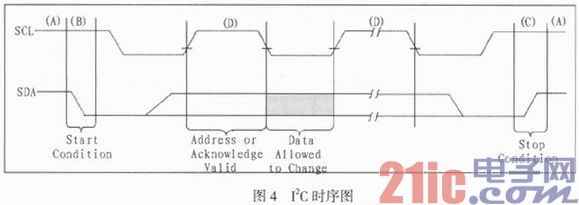

CF卡被用来存储音乐和数据文件,它通过DSP的外部存储器接口(EMIF)与DSP相连,它丁作在True—IDE形式和3.3 V的电压下。咱们能够依据体系需求挑选恣意容量的CF卡。选用Microchip Tethnology公司的64 kB的EEPROM 24LC512寄存的是发动程序,每当上电时,行将CF卡中的程序调入内存运转。

24LC512与DSP的接口选用I2C总线通讯。I2C(Inter—Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于衔接微操控器及其外围设备。I2C总线是由数据线SDA和时钟线SCL构成的串行总线,可发送和接纳数据。存CPU与被控IC之间、IC与IC之间进行双向传送,最高传送速率100 kbps。各种被操控电路均并联在这条总线上,但就像电话机相同只要拨通各自的号码才干作业,所以每个电路和模块都有仅有的地址,在信息的传输进程中,I2C总线上并接的每一模块电路既是主控器(或被控器),又是发送器(或接纳器),这取决于它所要完结的功用。CPU宣布的操控信号分为地址码和操控量两部分,地址码用来选址,即接通需求操控的电路,确认操控的品种;操控量决议该调整的类别(如音量等)及需求调整的量。这样,各操控电路尽管挂在同一条总线上,却互相独立,互不相关。其时序图如图4所示。

1.1.4 音频解码接口规划

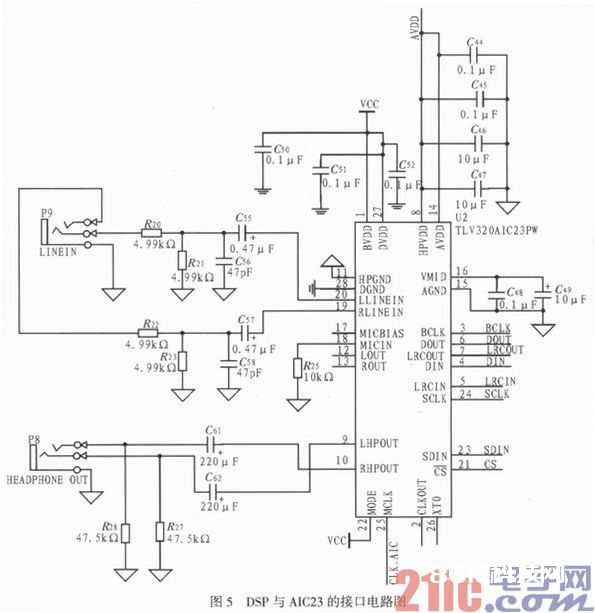

音频CODEC芯片选用的是TI公司的TLV320AIC23。它的首要作用是将DSP解码后的PCM音频流通过D/A改换,转化成模仿声响信号进行播映。

TLV320AIC23 DSP Codec是德州仪器公司2001年推出的高性能单片立体声编码解码器,数据转化字长16/20/24/32可选,作业电压与TMS320C55xDSP的中心和I/O电乐兼容,可完结与C55x DSP串行口的无缝衔接,功耗很低,带有的I2C和SPI总线兼容操控接口能使AIC23编码译码器与其他微处理器一起运用。

其首要特色如下:

1)高性能立体声编码解码器:支撑8~96 kHz采样频率,90DB ADC,100DB DAC转化信噪比,1.42~3.6 V内核数字供电电压,2.7~3.6 V模仿供电电压均与C55x DSP兼容。

2)可编程多种串行口数据传输规范:支撑I2C和SPI串口数据传输形式,均能够与C55x DSP的McBSP口兼容。

3)内置扩大的立体声输入输出(增益可调理),耳机扩大模块输出((30mW)。

4)低功耗电源办理:录音重放形式下19 mW,备用状况小于150 uW,中止状况小于15 uW。

音频CODEC与DSP的硬件接口电路如图5所示。

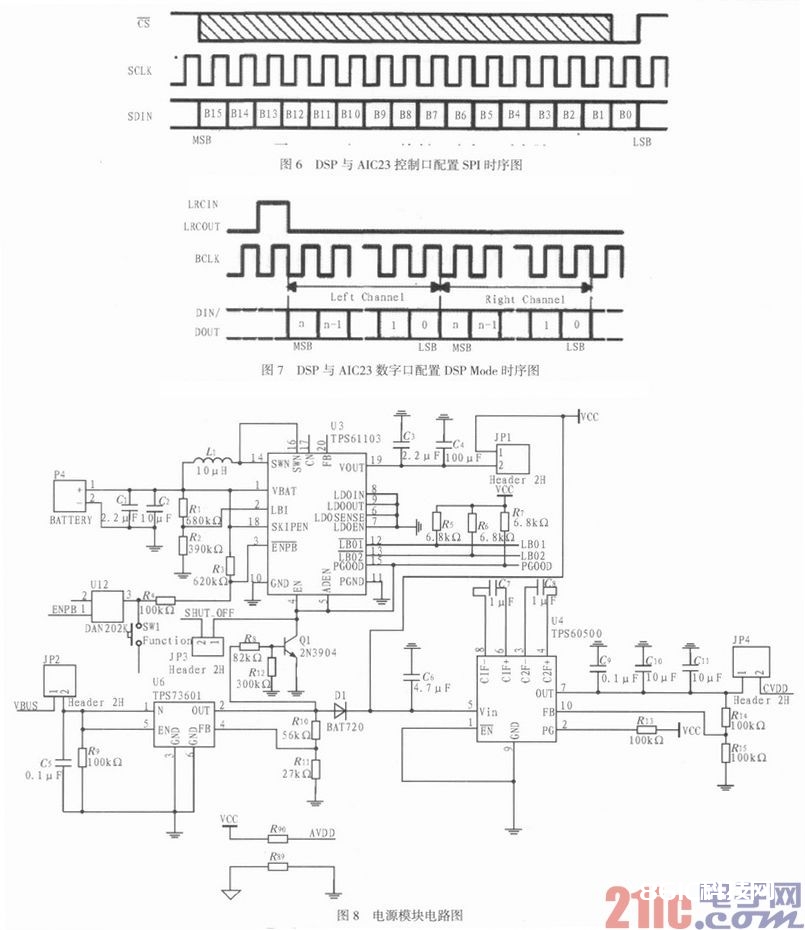

由上图咱们能够看出,DSP VC5509与AIC23的接口可分红两部分:操控接口部分(MeBSP1)和音频数据接口部分(MeBSP0)。其间DSP的McBSP1口完结AIC23的操控部分功用,此操控口装备为常用的SPI接口形式;而McBSP0口完结音频数据的传输功用,此数据口装备为DSP格局。

A%&&&&&%23的数字音频接口支撑4种数据格局:Right—Justified;Left—Justified;I2S格局;DSP格局。操控接口的SPI形式时序以及数字音频接口的DSP形式时序别离如图6和图7所示。

1.1.5 电源模块规划

在电源模块中,咱们选用了TI公司的三款芯片,别离是TPS61103,TPS60500,TPS73601。其间TPS61103用于将电池输入的1到3 V电压转化为固定的3.3 V,它为DSP的I/O及其他外设供电。TPS60500用于将3.3 V转化为DSP需求的内核电压1.6 V。此体系当通过USB接口与核算机相连时,就能够通过恰当的跳线设置不必接电池,TPS73601用于将USB接口供给的5V电压转化为3.3V。

2 软件研讨及算法完结

2.1 文件体系的完结

因为完结了FAT32文件体系,因而当此体系通过USB衔接到PC机时,在Windows操作体系下将看到它作为一个独立的存储器呈现,可是通过仿制粘贴操作将音乐文件复制到CF卡上。

2.2 MP3解码算法的完结

本计划进行软件的开发渠道是TI公司的C5000系列的集成开发环境Code Composer Studio 2.0。考虑到MP3解码软件的杂乱度和可读性,整个解码软件选用DSP的C言语编写。DSP的C言语具有与规范ANSI C言语相同的语法特色,一起还和DSP硬件相结合,能够直接操控DSP的在片或外围设备资源。跟着数字信号处理技能的不断发展,DSP的C言语编译器的编译功率也越来越高,5000系列的C言语编译器功率能到达

60%~70%,C6x系列的编译器功率高达80%。因而选用C言语来对DSP进行编程是必定的趋势。

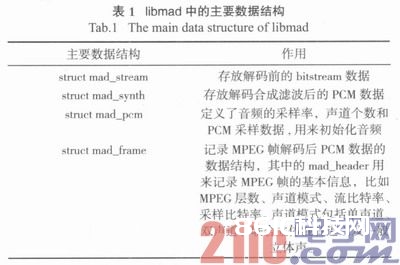

本计划在LIBMAD的基础上对软件进行规划。MAD(LIBMAD)是一个开源的高精度MPEG音频解码库,支撑MPEG-1(Laver I,Laver II和Laver III)。LIBMAD供给24-hit的PCM输出,完全是定点核算,十分适合在没有浮点支撑的渠道上运用。运用LIBMAD供给的一系列API,就能够十分简略地完结MP3数据解码作业。在LIBMAD的源代码文件目录下的mad.h文件中,能够看到绝大部分该库的数据结构和API等。

MP3解码算法尽管杂乱,可是整个解码进程分红各个模块进行,各个模块之间相对比较独立。在整个解码软件的规划进程中,对各个模块选用子函数,各个模块之间的联络就表现为函数的参数传递。整个解码软件由一个主函数操控,调度各个模块的有序运转。

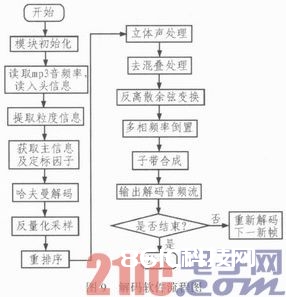

解码软件的程序流程如图9所示。从图中咱们能够看到对输入音频流解码先通过帧同步,读入同步头的信息,得到该MP3码流的采样频率、码流速率等参数,并记载现在所解码的MP3码流的帧数。然后取得粒度信息、主信息及定标因子,依据同步头中所得的MP3码流的紧缩类型来读取信息,取得对应于各自颗粒中的各自通道的相关参数。

然后对一帧中的两个颗粒进行解码,首要是从比特流中获取每个颗粒对应的定标因子,并对每个颗粒下的数据进行哈夫曼解码,这个哈夫曼解码进程需求32个哈夫曼码表之一来进行解码,能够依据边带信息中含有每个颗粒挑选码表的信息来进行挑选。通过哈夫曼解码的数据,接下来要通过反量化取样,在这步中,各个子带的数据依据所运用窗的类型,利用在边带信息中取得的参数反量化。接下来便是重排序和立体声处理模块,在这个模块中依据MP3码流所选用的紧缩类型来进行相应的处理。

这样当处理完一个颗粒中所有通道的数据后,就能够把这一颗粒已解码好的数据输出到输出缓冲区中,当把下一颗粒的数据解码结束并输出后,这样一帧数据就解码完结。这帧数据就能够输入到D/A部分进行播映,并将输出缓冲区清空,等候下一帧的解码数据的输入。解码程序一直到在比特流中再也找不到一帧的同步头时,就完结了这一音频流的解码。

3 结束语

MP3解码算法比较杂乱,并且市面上大部分便携式MP3播映器都选用的是硬件解码器,也便是选用专门的音频解码芯片来完结的,但是跟着数字信号处理技能的飞速发展,使得选用通用数字信号处理器(DSP)完结这一解码算法成为可能,并且存性价比、低功耗和软件晋级灵敏性上都优于选用硬件解码计划的mp3播映器,成为未来MP3商场的发展方向。