摘要 为有用进步视频监控使用领域中多屏幕画面显现的清晰度、分辩度等问题,提出了一种根据FPGA的实时视频图画处理算法。文中介绍了体系的全体结构,然后针对FPGA模块介绍了视频图画的缓存及图画切割,并针对视频的输出显现要求,要点介绍了根据双线性插值算法的完结。ModelSim的仿真成果表明,该算法契合多屏幕显现体系的要求。

关键词 视频监控;视频图画处理;双线性插值;FPGA;多屏幕

跟着网络信息化的开展,显现设备作为获取信息的直接手法,有着不可或缺的作用。为满意用户对更大屏幕的观看需求以及使信息显现更优化,大屏幕拼接技能应运而生。大屏幕图画尺度的增大使在一般显现器上不易发觉的细节暴露无遗,进步了可视化的准确性。高分辩率图形图画数据处理和可视化,用于处理根据单一硬件显现设备无法可视化的高分辩率图形图画。

而拼接操控器是大屏幕体系中的中心显现操控设备。拼接操控器的中心是其处理才能和稳定性,根据核算机体系构架的传统操控器,其功能和稳定性彻底取决于它所依靠的核算机,不管传统操控器怎么改善,最多只能算量的堆集,难以获得质的进步。选用大规模FPGA阵列式组合处理构架,全嵌入式硬件规划的拼接操控器集视频信号收集、实时高分辩率数字图画处理、二维高阶数字滤波等高端图画处理技能于一身,具有强壮的处理才能。

本文正是在这种布景下,规划了一种根据FPGA的视频图画处理算法,完结实时数字视频的切割、插值扩大,通过并行处理机制,确保了视频的实时处理和画面流通。

1 体系整体概述

文中将完结一路监控摄像头收集的画面在2×2的液晶拼接屏上显现一幅完好大图的作用。

体系的整体结构图如图1所示。由网络摄像头收集到的视频信号,通过DVI接收器后,宣布数据及操控信号供应FPGA。通过FPGA主控芯片对输入的视频信号进行切割、插值扩大等处理;视频输出模块将FPGA处理后的数据再通过DVI接口输出到屏幕上。

只需数据读出速度高于写入速度,就不会使图画产生骤变现象,然后到达实时处理的意图。

2 FPGA模块的完结

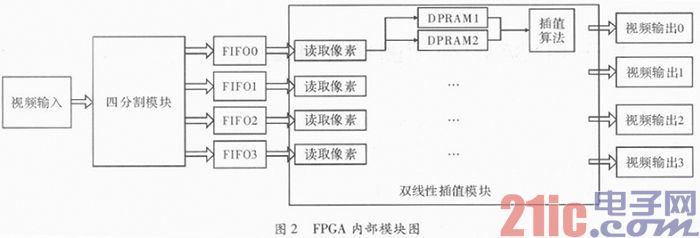

FPGA内部体系对视频图画的处理如图2所示。首要分为帧存储模块、切割模块、插值模块3部分。

2.1 帧模块及存储模块

DVI接口是将显卡中通过处理的待显现R、G、B数字信号与水平同步信号(Hsync,行同步信号)、笔直同步信号(Vsync,场同步信号)进行组合,按最小非归零编码,将每个像素点按10 bit(8 bit像素数据和2 bit操控信号)的数字信号进行并串转化,把编码后的R、G、B数字流与像素时钟4组信号依照最小化传输差分信号(Transition Minimized Differential Signal,TMDS)办法进行传输。

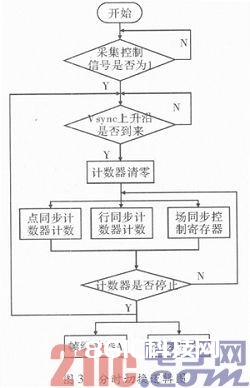

FPGA的分时切换逻辑是根据输入视频流的笔直同步操控信号Vsync产生由高电平到低电平的转化,以此作为新数据帧到来的标识,如图3所示。

当FPGA内部的信号操控收集信号为0时,收集体系中止工作,地址产生器不计数。当其为1时,体系处于收集状况。首要只要Vsync上升沿到来后,才答应Hsync通过,然后确保收集的图画为完好的一帧图画。当Vsync上升沿到来后,对一切计数器及触发器清零。Vsync上升沿后,场消隐延时用来对Hsync计数,场消隐期后,能够收集图画。行同步计数器对Hsync进行计数。在计数的每一行中,当Hsync上升沿到来时,行消隐延时对其计数。行消隐往后,点同步计数器开端对其计数。当行同步计数中止计数时,一帧图画收集结束,等候下一个Vsync到来。

数据缓冲区为两片SDRAM,以一帧图画为单位进行切换操控。选用乒乓存储机制完结数据的无缝缓冲与处理。乒乓操作能够通过“输入数据挑选操控”和“输出数据挑选操控”按节拍、彼此配合地进行来回切换,将通过缓冲的数据流没有中止地送到“后续处理”模块。

2.2 切割模块

因为一个像素的输出值只取决于输入图画的相应像素值,因而,可通过对每个输入像素顺次进行处理这种流水化的处理办法,来完结对图画的点操作。因为每个像素是独自处理的,所以点操作很简略并行完结。因而,能够把图画切割成若干部分,然后再对每个部分独自进行处理。

视频切割模块完结单帧视频图画的切割取舍,得到4路完好格局的子视频像素流,并操控4个子视频的彼此时序联系,各个拼接屏幕的像素点的扫描规则相同,均为逐行扫描办法,而且子视频像素点显现同步,即行同步和场同步。

2.3 双线性插值算法的完结

完结图片处理的插值办法有许多,例如最近邻插值、双线性插值、双三次插值等。最近邻插值是最简略的插值办法,但当图画中的像素灰度级有纤细改变时,该办法会在图画中产生人工的痕迹。双三次插值能够得到更滑润的成果,但在存储办理更杂乱,并增加了逻辑资源的耗费。因而,选取了双线性插值办法。

与点操作的图画切割不同,双线性插值归于几许改换,其输出的像素一般并不是来自同一个输入像素方位。因而需求一些办法的缓存来处理由几许形状改动而引起的推迟。

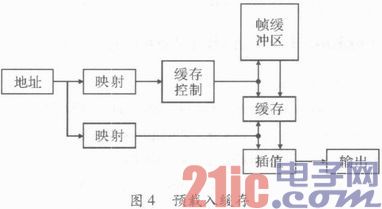

本文选用预载入缓存的办法来缓冲图画数据,并运用双端口RAM来完结行缓冲器的规划方案。

选用双口RAM可在一个时钟周期内一起在每一行上供给两个输入像素,即供给了一切的4个像素。然后将数据输送到插值核算模块。而整幅图画的存储将保存在外部的帧缓存中,每个时钟周期只能对其进行一次拜访。每个像素应仅从外部存储器中读取一次,然后暂存在片上缓存中用于随后的窗口。将数据预载入缓存,每次拜访时直接从缓存中读取像素,如图4所示。共需核算两次:一次用于载人缓存;一次用于履行插值。输入和输出像素间的映射选用前向映射。

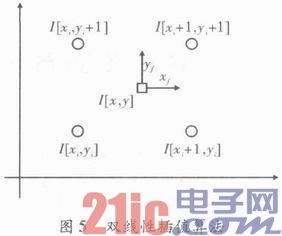

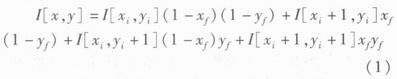

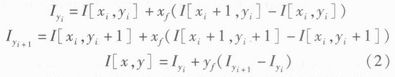

视频插值模块完结对视频按份额因子进行双线性插值扩大处理。双线性插值算法的基本原理如图5所示,图中的下标i和f表明各自坐标的整数和小数部分。双线性插值是选用可分离的线性插值将4个最近的像素值组合,如式(1)。

线性插值的成果与插值的次序无关。先进行y方向的插值,然后进行x方向的插值,所得成果相同。将式(1)进行分化,则有

当输入分辩率有所改变而引起缩放因子改变时,FPGA内的数字逻辑能实时核算出式(2)中的系数xf和yf。而非仅核算几种固定缩放份额,然后进步了算法模块的利用率。

若以将摄像机1 024×576分辩率的图转化为1 366×768的图为例,则水平缩放因子sc_x和笔直缩放因子sc_y均为0.75。若将水平因子直接带入编写程序,则会报错。选用浮点数表明法,转化后得到的10位16进制数,核算出系数xf和yf均为h300。

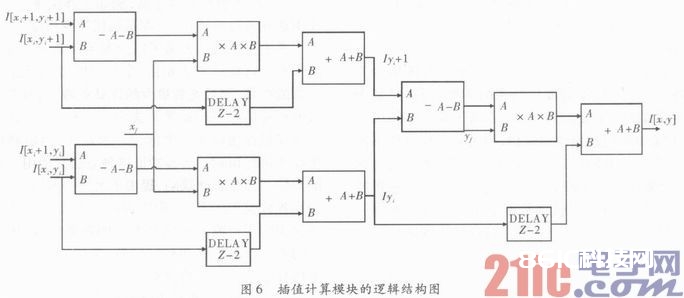

在实践规划中,为防止运算过于杂乱,把杂乱的运算分红几个过程,分别在不同的时钟周期完结。插值核算的逻辑结构模块如图6所示。

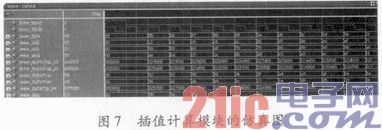

体系包括3种不同的时钟频率:原像素点频率clkin、输出像素点频率clkout和体系主时钟频率clksys。令体系主时钟频率为4倍的原像素点频率,则运用Verilog语言及ModelSim SE 10。1 a和Quartus II仿真环境进行编译,得到双线性插值核算模块的仿真波形如图7所示。为程序书写便利,将收集的4个像素值标为a、b、c、d,通过插值模块后的输出像素值为p。从仿真波形可看出,完结了双线性插值核算模块的完结。

3 结束语

针对大屏幕特色,从拼接操控器下手,提出了一种根据FPGA完结的视频实时处理体系。首要选用双线性插值法,评论了怎么用FPGA完结,并进行逻辑结构的优化,进步体系功能,并对双线性进行仿真,验证了算法在拼接显现体系中的可行性。环绕拼接操控器这个使用方向,还有更多的问题需求进行研讨,例如画面自在叠加与周游,单屏切割,主动图画识别重建等。