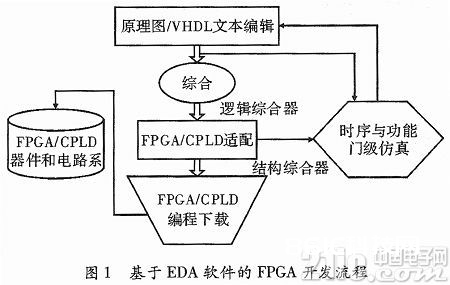

电子规划主动化(Electronic Design Automation,EDA)是以核算机为载体,在EDA软件渠道上,用硬件描绘言语VHDL完结规划文件,然后由核算机主动地完结逻辑编译、化简、切割、归纳、优化、布局、布线和仿真,直至关于特定方针芯片的适配编译、逻辑映射和编程下载等作业。EDA技能的呈现,大幅提高了电路规划的功率和可操作性,减轻了劳动强度。运用EDA东西,电子规划师可从概念、算法、协议等方面开端规划电子体系,很多作业可经过核算机完结,并可将电子产品从电路规划、功用剖析到规划出PCB地图的整个进程都在核算机上主动处理完结。根据EDA软件的FPGA开发已广泛应用于电子电路的规划与完结中,图1为根据EDA软件的FPGA开发流程。

1 电子表决器电路

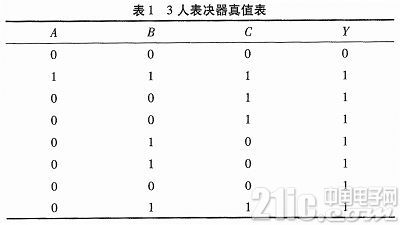

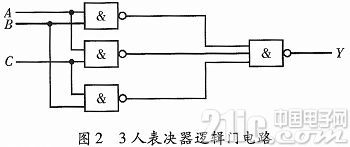

传统的电子表决器经过逻辑门电路完结、功用简略、不易扩展,表1是一种3人表决器的真值表,图2是由逻辑门组成的电路图。

2 根据FPGA的电子表决器

2.1 8人表决器电路

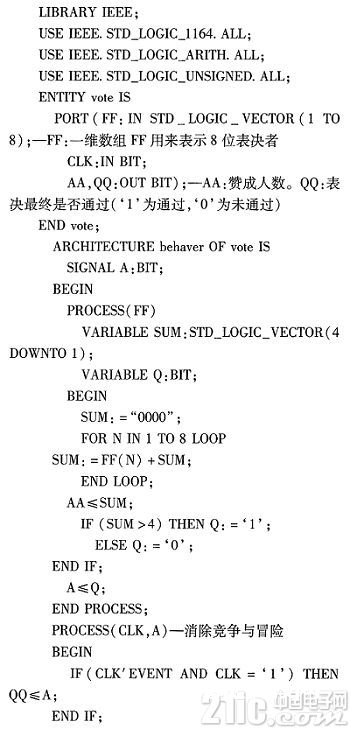

结合VHDL言语在FPGA渠道完结电子表决器电路规划,可减小体系面积,便利扩展晋级,以下程序是运用VHDL言语描绘的8人表决电路。

2.2 10人表决器电路

经过8人表决电路表决经过期电路状况的调查和验证,运用VHDL言语在FPGA渠道完结10人表决器电路规划。在8人表决器编程基础上修正程序,完结10人表决器电路的规划。编程中完结参加表决的每个人均可选择拥护、抛弃或放弃。一起,添加了操控键,可添加专人在进行表决进程中的操控,完结了表决的开端、完毕和数据的锁存。

3 电路仿真

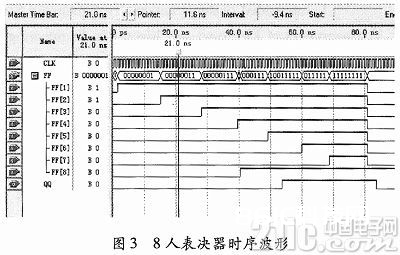

图3是8人表决器电路时序波形,从图中可看出程序完结了规划要求,在8人表决器程序的RTL生成电路界面显现有9个逻辑门和硬件资源组成电路。

按图4所示进行管脚确定后,即可在试验箱上进行验证,将程序下载到试验渠道后,获取试验成果,经验证契合规划要求。

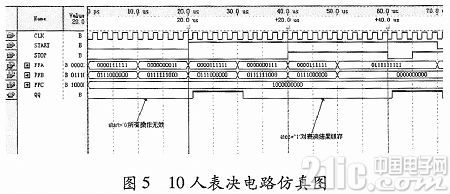

图5为程序仿真成果。在10人表决器的RTL电路界面图中可看出,其比8人表决器程序的RTL电路界面图多出了一些硬件资源,若独自运用逻辑门规划电路将是一件杂乱的作业,且不便于修正和测验。

而运用EDA进行规划,还可便利地进行体系扩展,如上述程序中只需添加几个输出端口,将SUMA,SUMB,SUMC的值赋给相应端口,在外接数码管便可显现出拥护、对立、放弃的人数。或添加声响模块,使体系更具实用价值。而进行这些作业只需改动程序,参加现成的%&&&&&%即可。

4 完毕语

电子表决器,做为投票体系中的客户端,是一种代表投票或举手表决的设备。根据FPGA电子表决器的规划处理了传统投票表决方法存在投票耗时长、计票任务重,且易于犯错、易受人操控等缺陷,故在表决、推举中获得了广泛应用。