3.3正交双鼓励数字相敏检波办法

3.3.1正交双鼓励数字相敏检波原理

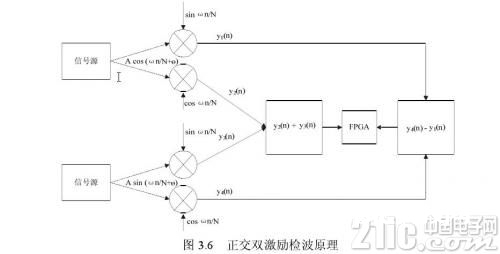

数字相敏检波技能能够有用提取被测信号的起伏和相位,跟着累积周期的添加,体系的全体差错将减小。可是跟着周期的添加,检波的时刻也跟着会添加,以这种办法检波时,将体系全体差错减小是以时刻为价值换来的。为处理单鼓励DPSD存在较大体系差错的缺陷,本文提出一种正交双鼓励数字相敏检波办法(D-DPSD),其丈量原理如图3.6所示。

正交双鼓励数字相敏检波办法充分使用鼓励源宣布的信号的特征,在两路信号进入被测网络前确保其正交,即让余弦鼓励信号 经过待测网络,与一组同频率正交信号相乘得到y1(n)和y2( n ),然后让同频正弦鼓励信号经过待测网络,得到y3( n )和y4( n ),将得到的信号经过线性运算即可消除高频重量。

经过待测网络,与一组同频率正交信号相乘得到y1(n)和y2( n ),然后让同频正弦鼓励信号经过待测网络,得到y3( n )和y4( n ),将得到的信号经过线性运算即可消除高频重量。

3.3.2正交双鼓励数字相敏检波理论剖析

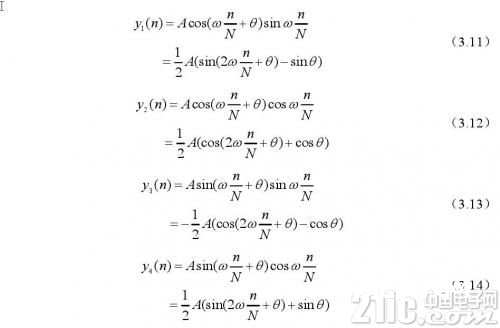

正交双鼓励数字相敏检波办法是在DPSD算法基础上提出的,在理论上还连续着DPSD的部分中心思维。例如,D-DPSD仍是选用数字正弦波或余弦波进入被测网络,每路信号经过被测网络之后仍是选用与正交同频信号相乘的办法解调。不同的是,D-DPSD检测办法的用两路坚持正交的信号进入被测网络。首先让余弦鼓励信号 经过待测网络,与一组同频率正交信号相乘得到y1(n)和y2( n ),然后让同频正弦鼓励信号经过待测网络,得到y3( n )和y4( n ),如下所示:

经过待测网络,与一组同频率正交信号相乘得到y1(n)和y2( n ),然后让同频正弦鼓励信号经过待测网络,得到y3( n )和y4( n ),如下所示:

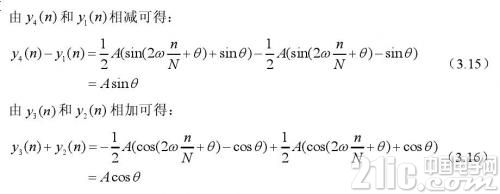

再由(3.15)、(3.16)得到的A sinθ和A cosθ进行以下运算,即可求得目标值θ*和A*:

3.4 DPSD与D-DPSD仿真剖析

3.4.1仿真试验为验证数字正交鉴幅鉴相成果,在System Generator上建立了模型体系进行仿真试验。

System Generator是Xilinx公司的体系级建模东西,在许多方面扩展了MathWorks公司的similink渠道,供给了合适硬件规划的是数字信号处理(DSP)建模环境,加快了、简化了FPGA的DSP体系级硬件规划,所建立的体系可直接出产比特流在FPGA中运转。System Generator供给了体系级规划才能,答应在相同的环境内进行软硬件协同仿真、履行和验证,并不需要书写VHDL代码。在System Generator规划中,使用其强壮的信号处理才能,调用各个功能模块,完成单鼓励数字相敏检波和正交双鼓励数字相敏检波办法的仿真,其间AD采样数据经挂接在PLB总线上的IP Core进行处理后传给System Generator处理单元,数据进入处理单元后首先进行数据类改换,然后别离送入乘法器进行正交相乘运算,将运算成果送到上位机进行处理。

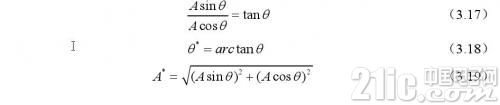

针对本文单鼓励数字相敏算法,建立的仿真体系图如图3.7所示。

其仿真成果能够在Wavescope中显现,也能够经过软件从文件中调出加以检测。本文经过MATLAB中的Editor东西调用System Generator中所发生的两个文件:cos.mat和sin.mat.

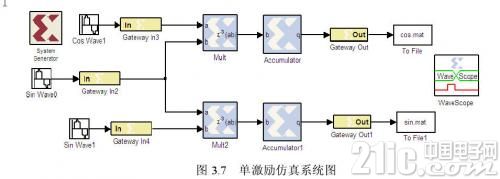

相同,按正交双鼓励数字相敏检波办法建立D-DPSD仿真体系,体系图如图3.8所示。

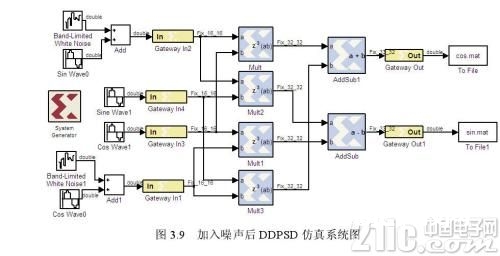

图3.8为纯洁情况下的仿真体系图,现实情况中,当鼓励信号输入体系时,往往伴有噪声输入。建立仿真体系时,参加白噪声和随机噪声进行仿真,如图3.9所示。将噪声参加正、余弦鼓励信号Wave0并与Wave0一同输入体系,与其同频的一组正交信号Wave1相乘,将最终所得成果存入cos.mat文件和sin.mat文件中,然后再用MATLAB中的Editor东西调用这两个文件显现仿真成果。

3.4.2 DPSD与D-DPSD仿真比照

将上一节中建立的三个体系的输出结构经过Gateway Out输出到cos.mat文件和sin.mat文件中,然后再用MATLAB中的Editor东西调用这两个文件,对其起伏相位进行处理后显现仿真成果,将其成果显现为相应的三角函数值。

要提取信号的起伏和相位值,最有用的办法是先提取信号的正弦和余弦值,假如这两个值在必定数值上平稳,则代表这种办法辨别信号起伏相位是有用的,越平稳,功能就越高。

3.4.2.1 DPSD仿真剖析

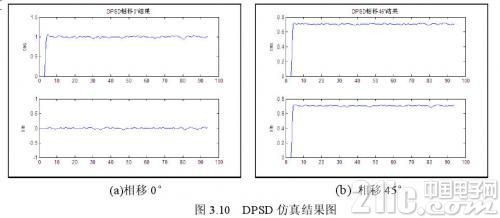

使用图3.7所示的仿真体系进行仿真,将参数设定为:输入信号一个周期的量化点数为10,输入信号的相位偏移别离为0°和45°。可得到成果如图3.10所示的仿真成果图。

仿真成果图中,横坐标为累加的点数,纵坐标为相应的三角函数值。由图3.10的仿真成果表明,信号经过网络后,被提出来的正余弦值与设定相位的正余弦值根本共同,因而这种办法是可行的。

3.4.2.2 D-DPSD仿真剖析利

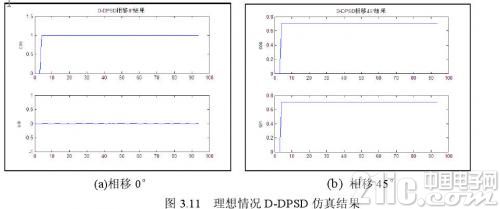

用图3.8所示的仿真体系进行D-DPSD办法仿真。将参数设定为:输入信号一个周期的量化点数为10,输入信号的相位偏移别离为0°和45°。可得到如图3.11所示的仿真成果图。

仿真成果表明,信号经过网络后,被提出来的正余弦值与设定相位的正余弦值共同,因而这种办法能够更准确的计算出信号的起伏和相位。

现实情况中,当鼓励信号输入体系时,往往伴有随机噪声和白噪声输入。运转图3.9所建立的仿真体系,得到加噪情况下的仿真成果如图3.12所示。

仿真成果表明,信号经过网络后,被提出来的正余弦值与设定相位的正余弦值根本共同,信号平稳,因而这种办法能够得到信号的起伏和相位。

3.4.2.3 D-DPSD与DPSD仿真剖析

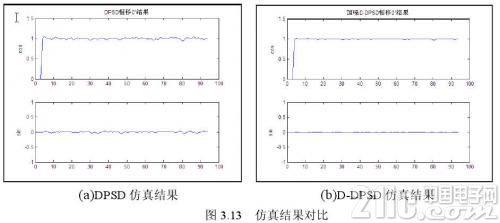

比照D-DPSD算法在DPSD算法基础上提出,将D-DPSD仿真成果与DPSD在相同条件下的仿真成果进行比照,如图3.13所示。由图可知,D-DPSD算法仿真成果显着平稳,差错起浮规模有所减小。因而,D-DPSD减小了DPSD算法累积发生的差错,从而使整个体系的差错得到减小,进步了体系丈量信号起伏和相位的精度。

剖析丈量进程,丈量精度首要受AD采样、乘法器截断差错以及累加器截断差错影响。只需规划选用12位以上AD进行采样,并确保差分输入峰峰值为±1.024V.可计算其量化差错为:

量化规模为-V到+V,L为量化距离数。

为进步丈量精度,乘法器和累加器别离选用选用24位和40位,消除截断差错的影响,这样累加器输出的成果理论差错为0.0005V,只需确保AD输入信号起伏较大,体系差错能够远小于5%,可满意生物电阻抗丈量要求。