刚开端玩CPLD/FPGA开发板的时分运用的一块根据EPM240T100的板子,alter的这块芯片虽然功耗小体积小,可是资源仍是很小的,你写点略微杂乱的程序,假如不注意coding style,很简略就溢出了。其时做一个三位数的解码根本就让我苦死了,对coding style的重要性也算是有一个比较深入的认识了。

后来由于一直在玩xilinx的spartan3 xc3s400,这块芯片资源适当丰厚,乃至于我在它里边缓存了一帧640*480*3/8BYTE的数据都没有问题(VGA显现用)。而最近触摸EPM7128,它的资源好像也不丰厚,我写着写着有时不注意就无法布线了。由此可见coding style对规划的重要性,尤其是在资源严重或许速度要求较高的规划中。我个人对前者的领会深一些,高速的规划没有触及过,仅仅理解一些用流水线进步速度的办法。

能够步入正题了,先拿一段简略的代码开端吧。我先提一点,这回我用的是quartus II 7.0进行测验,其它的EDA东西归纳出来的RTL视图或许会不相同,所以仅作为在quartus II 7.0环境下的一些参阅吧。不过思路是相同的,能够学习的。

Ex1:

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0);

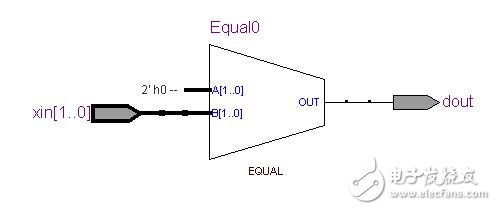

代码很简略,便是当xin==2’b0时dout=1,不然dout=0。上面这段程序的RTL视图如下:

其实便是一个比较器,假如xin=2’h0,那么输出OUT就为1。和想象相同。

下面是我在参阅一些他人的代码的时分看到他人一种常见的写法,它是用了?句子。

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0) ? 1'b1:1'b0;

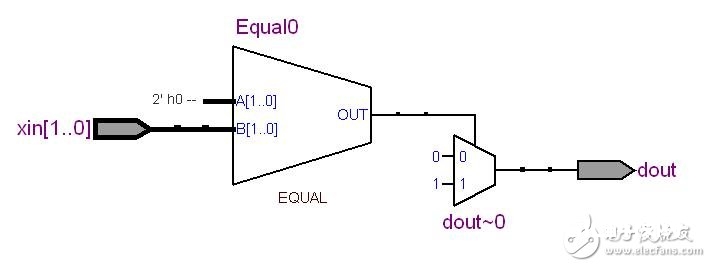

RTL如下:

是不是发现多了以一个选择器(或许不叫选择器吧,可是你理解意思就能够),这样无缘无故的就多耗用了一点资源,刚开端的时分我也是傻呵呵的跟着他人用这种写法,可是看到RTL视图后我就不这么干了,已然前者相同能够得到预期成果,为什么我还要弄巧成拙多一个选择器呢。所以,引荐运用前者。资源的节约是耳濡目染的~_~

(先说一点吧,其它的待我想起或许是感悟到了再提吧,以上也完全是我的个人鄙意,如有不当之处欢迎拍砖~_~)