资源的运用:

今日对FPGA中的srl16资源IP核进行的仿真,以研究其功用,芯片为XC7K325Tffg900。

1、SRL16的效果便是移位寄存器,Xilinx的FPGA中根本单元为CLB,CLB由两个slice构成,分为SliceL与SliceM,其间SliceM中的LUT能够装备为Distribute RAM或SRL;

2、SRL16的IP核名称为RAM-based Shift Register ,其装备参数有以下几个:

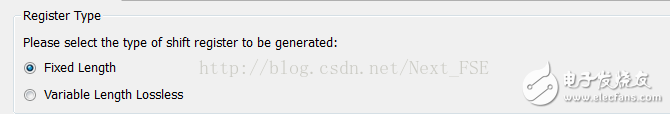

(1)、

这个参数确认的是移位寄存器的移位时钟个数。这个时钟个数取决于后边的Depth参数。其间第一个参数Fixed Length 指的是移位周期数是固定的(后边的Depth指定)。第二个参数指的是可变长度的,也便是说移位寄存器的移位长度是可变的,至于长度终究是多少,那就得看下面的参数Depth了,这个Depth代表的是移位寄存器的最大移位长度(由于是可变的),假如挑选这一项的话就意味着会启用一个外接寄存器来操控移位的真实长度,也便是A[]寄存器,这个输入来操控移位的真实长度(但是在Depth范围内)。

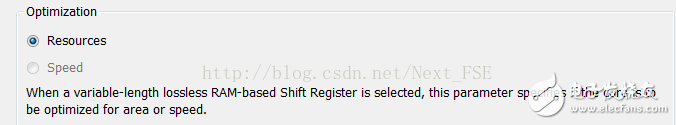

(2)、

这个参数指的是优化的参数,也便是面积与速度的挑选,当挑选可变的移位寄存器长度时,才能够挑选面积或许速度;当挑选固定长度时,只能挑选面积优化。

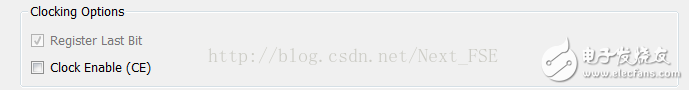

(3)、

时钟使能引脚

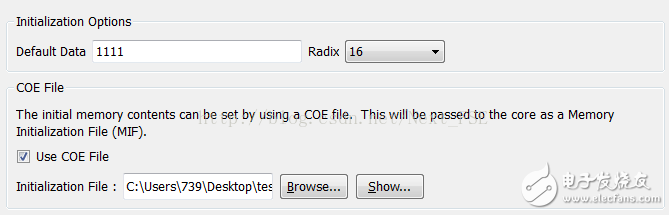

(4)、

第一个参数指的是确认输入数据的位宽,也便是输入数据是多少位的,第二个参数在固定长度移位寄存器中是移位寄存器移位的长度,在可变长度移位寄存器中指的是最大移位长度。

(5)、

先这样想,移位寄存器的意图是把现在输入的数据通过几个时钟周期延时后再输出,这样的话最开端有一段时刻(刚输入数据的时刻)输出信号线上终究是什么数据呢?第一要确认的是在上电之后,在1.5个时钟周期内输出的数据是之后咱们需求确认的默许数据,而在这1.5个周期之后到咱们真实数据移位完结开端输出的这一段时刻里数据是什么呢?便是上面的coe文件中的数据或许Default Data,它指的是在上电后一个半时钟周期后到真实的数据输出这段时刻内输出线上需求呈现的数据,也便是coe或许1111。经验证,coe文件的优先级要高于Dfault Data。

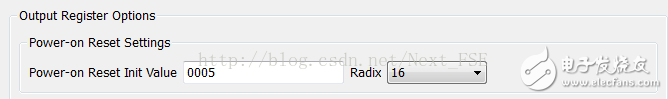

(6)、

这个参数便是1.5个时钟周期内输出的数据。