0 引 言

数字电位器是运用微电子技术制成的集成电路,它是依托电阻阵列和多路模仿开关的组合完结阻值的改动。它没有可动的滑臂,而经过按钮输入信号,或是经过数字输入信号改动数字电位器的阻值。数字电位器因为可调精度高,更安稳,定位更精确,操作更便利,数据可长时刻保存和随时改写等长处,在某些场合具有模仿电位器不行比较的优势。

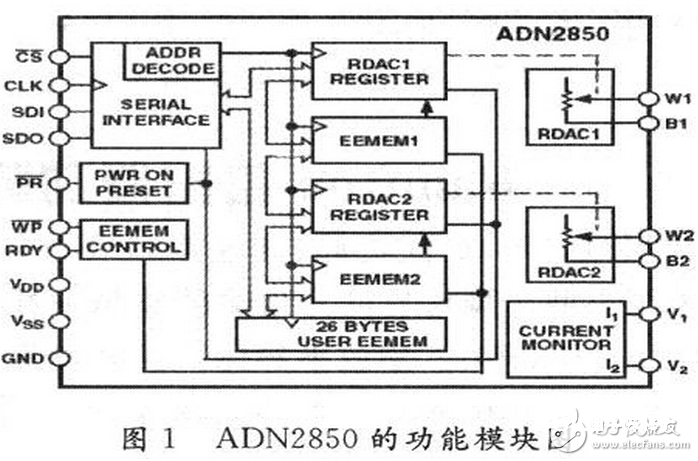

1 ADN2850的根本结构和作业原理

ADN2850是ADI公司的双通道,1 024阶非易失性数字电位器。温度系数仅为35 ppm/℃。其功用模块图如图1所示。它的输出电阻W和B之间的阻值首要由中心寄存器RDAC中存储的值决议。RDAC的值能够由外部指令直接赋予或许从内部非易失性存储器E2MEM中载入。E2MEM中的值能够被修正或许被维护。当RDAC中的值被改动后,新的值也能够被存入E2MEM中。之后,新的值将在体系从头上电后主动加载到RDAC中。

ADN2850的指令体系包括16种形式,经过一个规范SPI串行接口传送24位指令字决议,高位在先。24位指令字的前4位是指令,接下来4位是地址,后边16位是数据。这些指令能够用于RDAC的值的写入,E2MEM值的改写与恢复,电阻值的回读等。

2 SPI接口简介

SPI是一种高速的,全双工,同步的通讯总线,并且在芯片的管脚上只占用4根线,节约了芯片的管脚,一起为PCB的布局上节约空间。正是出于这种简略易用的特性,现在越来越多的芯片集成了这种通讯协议。

SPI的通讯以主从办法作业,这种形式一般有1个主设备和1个或多个从设备,一般需求4根线,事实上3根也能够(单向传输时)。其也是一切根据SPI的设备共有的,它们是SDI(数据输入),SDO(数据输出),SCLK(时钟),CS(片选)。由SCLK供给时钟脉冲,SDI,SDO则根据此脉冲完结数据传输。数据输出经过SDO线,数据在时钟上升沿或下降沿时改动,在紧接着的下降沿或上升沿被读取。完结1位数据传输,输入也运用相同原理。这样,在至少8次时钟信号的改动(上沿和下沿为1次),就能够完结8位数据的传输。ADN2850的SPI接口的4根引脚线分别是SDI,SDO,CLK,CS。

这儿运用FPGA对SPI接口进行装备。为了便利对输入SPI的指令的随时改动,而不需求程序的重复写入,24位指令经过串口输入到FPGA。串口通讯由微机上的串口调试帮手帮忙进行。因为少了从头写入程序的时刻,然后调试速度和功率显着增高。

3 串口简介

串口是核算机上一种通用的设备通讯的协议,能够用于获取长途收集设备的数据。

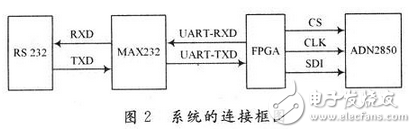

串口按位(b)发送和接纳字节。通讯运用3根线完结:地线、发送、接纳功用。因为串口通讯是异步的,端口能够在一根线上发送数据一起在另一根线上接纳数据。其他线用于握手,但不是有必要的。串口通讯最重要的参数是波特率、数据位、中止位和奇偶校验位。波特率是衡量通讯速度的参数,它表明每秒钟传送的bit的个数。数据位则是衡量通讯中实践数据位的参数。中止位一般是为了平衡两个体系的时钟而在实践数据位完毕后传送的。奇偶校验位是串口通讯中检错的一种办法,没有校验位也能够。整个体系的衔接框图如图2所示。

4 ADN2850的串口操控

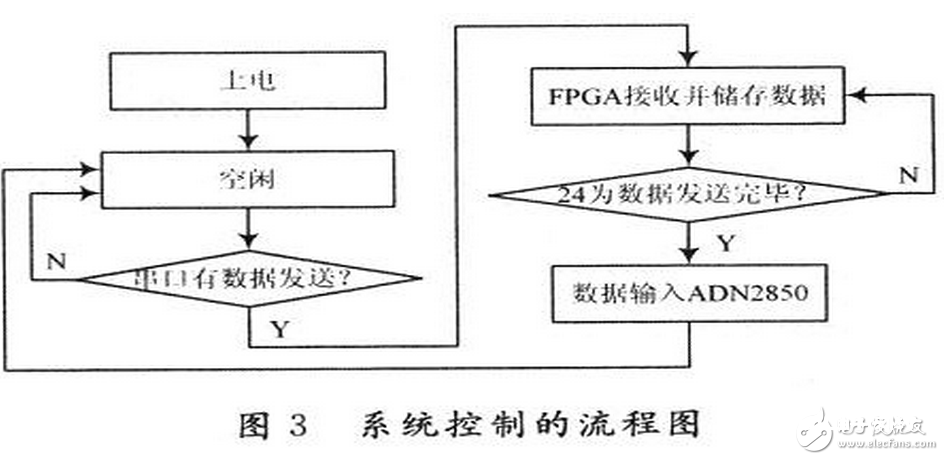

用串口操控ADN2850的流程图如图3所示。一旦有指令从串口发送,就从头经FPGA后写入ADN2850。

Verilog HDL程序分为3个模块,分别为复位rstgen模块,串口接纳datagen模块和SPI接口操作spi模块。24位指令由微机输入,经串口接纳模块后输出1个24位数据和1个标志位,用于SPI接口模块把数据传入ADN2850中。

datagen模块要害程序如下所示(相关变量声明省掉):

该程序现已经过前仿真,并在Altera公司的EP2C70 FPGA上经过了验证,达到了预期的作用。

5 结 语

经过串口的使用,ADN2850的操控进程变的很便利。而串口自身连线简略占用资源少,使用也比较广泛,所以数字电位器ADN2850的串口操控不失为一种可行的办法。