1 导言

振荡台的效果之一是将被测物件置于振荡台上丈量其受迫振荡时的体现,一般振荡台的振荡是由振荡分析仪操控的,可是因为振荡台体积形状和考虑到本钱等原因,不利于振荡分析仪的研制,所以规划振荡模仿器对振荡分析仪的研制有重要的现实含义。

振荡模仿器应尽量对振荡台的实践振荡状况进行模仿。振荡台自身的振荡将不可避免地遭到噪声的影响,导致它的振荡纷歧定是契合需求的振荡。所以要使振荡模仿器对振荡台的实践振荡状况进行模仿,就必需人为地在采样信号中参加噪声。而出于对振荡分析仪研制调试的需求,尽量将噪声规模处理成可控的,这样便于调试振荡分析仪。

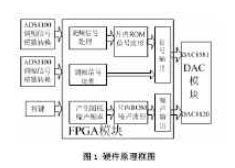

运用FPGA开发振荡模仿器研制开发费用低,不承当投片危险,通过开发工具在核算机上完结规划,电路规划周期短。所以本文选用FPGA完成振荡模仿器规划,由ADC模块接纳调频和调幅信号,传给FPGA模块,FPGA由调频信号核算出对应的时钟,且按此时钟输出经调幅的数字正弦波,驱动DAC输出模仿的正弦波,终究和模仿的噪声相叠加,完成对实践振荡台的模仿。

2 原理框图和根本规划思维

振荡模仿器的原理框图如图1所示,图中由ADC模块别离接纳调频和调幅信号给FPGA模块,FPGA模块将串行的调频和调幅信号,经串并转化,别离变成一个16位的并行调频信号和一个16位的并行调幅信号。FPGA输出经调频调幅的数字的正弦波,并驱动串行DAC(输出抱负信号)输出模仿的正弦波;用户通过按键确认想要发生的噪声的频率规模,FPGA经核算得到满意用户要求的频率,驱动并行DAC(输出噪声),发生模仿 •的噪声,经电流电压转化后由同相求和电路将信号与噪声相叠。

整个体系终究输出0.1~5KHz的振荡信号和200KHz以下的振荡噪声相叠的模仿量。

3 FPGA功能模块介绍

3.1 芯片挑选

在本规划中,选用Altera 公司的Cyclone系列,类型是EP1C6Q240C8的芯片,PQFP封装。这款芯片有240个引脚,其间用户可用185个引脚。有5980个逻辑单元,32列20行逻辑阵列块。有2个PLL锁相环,20个M4K的ROM,每块ROM为4Kbit,能够另加1位奇偶校验位。

3.2 原理阐明

FPGA模块接纳2个ADS1100的芯片,经串并转化,得到调频和调幅信号。

波形发生的根本原理是:对幅值是1的正弦波在一个周期内的波形按1/200倍周期的时刻距离取200个点,存储这200个时刻点所对应的波形的起伏,存储到FPGA的片内ROM中。正弦波起伏表仅需200×16bit=3.2kbit的存储空间,可用FPGA的一块片内ROM完成。通过查表法发生一系列的值,将这些值和调幅信号相乘就得到一系列的起伏值,即串行DAC的数字输入,而这些起伏的输出频率是调频信号值的200倍。相似的,运用FPGA一块片内ROM以存储200KHz以下噪声的正弦波起伏表(一个周期内的波形按1/20倍周期的时刻距离取20个点)。

调频信号和调幅信号的分辨率16比特,输出的正弦信号的分辨率是16比特。

4 AD、DA芯片与FPGA的接口

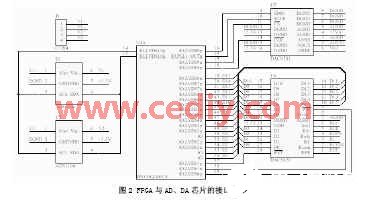

考虑到本体系需求较多的高频时钟,而若时钟办理不妥,则因DAC作业不稳定会导致体系作业犯错;因为连线和逻辑单元的推迟效果,使输出信号呈现毛刺,发生冒险现象。因而朴实依托传统的逻辑电路难以到达抱负的功能要求,这时就必须依靠FPGA内部的专用硬件电路PLL和引进高频时钟的办法发生无有害毛刺的同步时钟辅佐完成高功能的规划。

FPGA芯片和ADC、DAC芯片的接口电路原理图如图2所示。

4.1 FPGA对ADS1100芯片的操控

调频和调幅信号运用同一款芯片:ADS1100,16位串行,I2C接口,在本规划中数据更新率是8SPS,电压型输出。此芯片仅可在从件形式下作业。ADS1100将模数转化成果传给FPGA模块,由FPGA进行串并转化。

FPGA对ADS1100供给SCLK和SDA引脚,契合I2C协议。FPGA是主器材,在开端与ADS1100通讯前先对SDA写2个字节,别离确认和哪个ADS1100进行通讯和对ADS1100的装备寄存器(configuration register)进行写以确认对其的操作形式。FPGA外接24MHz的晶振,经分频得到4MHz的时钟,ADS1100按8SPS的数据更新率作业,FPGA勘探数据线改动以发生SCLK时钟信号赋给SCLK引脚。篇幅受限,I2C的FPGA完成纷歧一赘述。

4.2 FPGA对DAC8581芯片的操控

信号输出运用芯片DAC8581,16位串行,SPI接口,在本规划中最高数据更新率是1.8MHz,电压输出。DAC8581接纳从FPGA传送过来的串行数据,将其进行数模转化,发生振荡信号,模仿实践振荡台的抱负振荡状况。

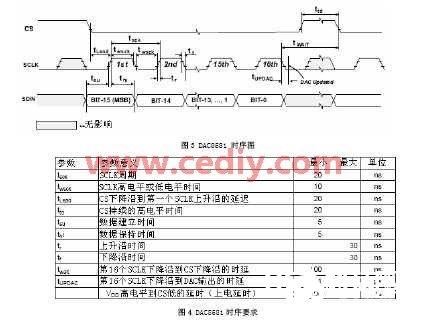

FPGA中,由PLL倍频得到36MHz的时钟供给给DAC8581的SCLK引脚。由调频信号核算得到串行DAC的数据更新率,按此频率更新串行DAC的数字输入。由同一个PLL倍频得到240MHz的时钟捕捉将由DAC处理的数字输入信号和SCLK引脚信号的跳变沿,然后发生DAC8581的CS片选信号。

数据data一旦预备好,赋给register,240MHz时钟勘探到第一次SCLK上升沿,就拉低CS片选,第2次勘探到SCLK上升沿时现已至少是下一个240MHz的上升沿了,然后满意Tlead(见图3、图4)参数的要求。CS低时,一旦240MHz时钟勘探到SCLK下降沿,将register的最高位数据赋给SDA,将register左移一位,SDA坚持不变,直到下一个SCLK下降沿。当捕捉到SCLK的第17个下降沿时,将CS拉高。由此即可满意以上的图3、图4对时序的要求。

4.3 FPGA对DAC8820芯片的操控

DAC8820发生振荡噪声。16位并行,最高数据更新率4MHz,是电流输出型。本体系设有2个用户按键,别离表明发生40KHz~100KHz,100KHz~200KHz的噪声频率规模,FPGA接纳按键信号确认噪声的频率规模,在此频率规模内发生一个随机频率,由此核算得到DAC8820的数据更新率,FPGA按此频率预备数据以更新并行DAC的数字输入。由DAC8820将其进行数模转化,模仿实践振荡台在或许遭到外界各种搅扰信号后发生的噪声状况。

DAC8820的引脚WR(低有用)是将16位数据加载到输入寄存器;LDAC(高有用)是将数据从输入寄存器加载到DAC寄存器;可是若将同一信号一起赋给WR和LDAC,则可在下降沿将16位数据加载到输入寄存器,在上升沿将数据从输入寄存器加载到DAC输出。

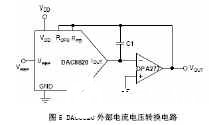

由FPGA将24MHz的晶振时钟分频得到数据更新率,由此得到的时钟信号经高频时钟同步赋给DAC8820的WR和LDAC。因为DAC8820是电流输出的,所以将电流输出通过OPA277电流电压转化输出,见图5。图中的C1是补偿电容,其效果是避免增益峰值的呈现。

5 定论

综上,此振荡模仿器的调频信号的分辨率是16比特,可发生0 ~5kHz的明晰信号,所以频率精度可到达0.076Hz,并可与200KHz以下的确认频率规模的随机噪声进行组成,输出信号起伏分辨率可达16比特,并且噪声的频率规模是可控的。

本文作者立异点:充分运用了FPGA可现场编程的特色,给读者供给了一个施行简略,本钱低,可按用户需求灵敏改动,且易晋级的振荡模仿器的规划方案;且对有特殊要求的信号发生器的规划有必定学习含义。

责任编辑:gt