导言

跟着测控技能及数字图画处理技能的高速开展,依据三角法线结构光的三维丈量具有高精度、非触摸、实时性和强自动受控性的特性,因此在实际中有广泛的运用,尤其是在核算机视觉、医疗确诊和工业检测等范畴运用价值日渐增强。在结构光检测体系中,运用CCD相机以及工业相机摄取用线结构平面激光照耀照在物体外表构成的光条纹中心信息,然后依据光条纹中心偏移量进行三维定标,这样能够得到物体外表的各类信息,比方外表的缺点以及形变等。有鉴于此,线结构光条中心信息的图画处理在丈量进程中就显得十分要害。尽管现在结构光中心线的提取办法有许多种,比方:阈值法、极值法、灰度重心法、方向模板法、Hessian矩阵法等,这些办法都有各自的优缺点以及必定的运用规模。依据数字图画处理的特点是处理的数据量十分大,处理十分耗时。所以本文研讨了在FPGA上用硬件描绘言语完结图画的中心线提取算法,选用了极值法、阈值法和重心法相结合的中心线提取办法。通过功能模块的硬件化,以便高速提取结构光中心线。成果标明,试验体系到达了依据视频速度的运用要求。

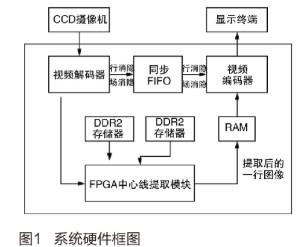

1 、体系硬件规划

图1为光条中心线提取体系的硬件规划框图。整个中心线提取体系主要有四个组成部分:

(1)视频数据编码模块:编码器选用ANALOG DEVICES公司的ADV7179芯片,该编码器能完结ITU—R BT601/BT656 YCrCb(其份额为4:2:2)格局的数字信号转为NTSC/PAL摸拟视频输出信号;

(2)DDR2 SDRAM存储器操控模块:选用两片MICRON公司的MT47H64M16 DDR2存储器来完结图画帧数的穿插缓存,为后边的中心线提取供给像素值以及坐标值;

(3)中心线提取模块:FPGA选用的是Altera公司Cyclone III系列的EP3C40F484C6芯片,该芯片价格低廉、实用性强,能充分发挥芯片的并行核算才能,完结中心线的快速提取;

(4)视频数据编解码模块:解码器选用TEXAS INSTRUMENT 公司的TVP5150芯片,该芯片低功耗,能处理视频输入输出同步问题,并且输出类型的特性能够通过I2C串行接口进行编程装备。

整个体系从CCD摄像机接纳的模仿视频信号通过视频解码芯片解码后,转换成BT656(4:2:2)YCbCr SDTV(标清)格局的数字视频信号,通过一个FIFO来进行行/场消隐、解出同步信息等操作,之后提取图画信息的Y(亮度值)重量,然后在数据上传输。关于图画的传送选用两片DDR2来进行奇偶两场传送;一起对视频解码器输出的同步信号进行检测。当有用数据到来时,FPGA挑选一片DDR2,运用隔行存储办法,完结一帧图画的存储,当第二帧图画有用数据到来时,FPGA挑选另一片DDR2,以相同的办法完结第二帧图画的存储,顺次穿插存储,然后经内部的处理模块处理后得到图画光带中心线坐标[8]。将提取的一行中心线坐标存储在RAM里边,再通过视频编码器将数字视频信号转换成模仿视频信号输出到显现终端显现。

2、 算法的FPGA完结

2.1 算法流程

咱们首先以列扫描的办法读出一帧数据,并将读出的亮度值与所设定的阈值进行比较。滤除不需求的点,然后通过像素值比较得到像素值最大点,之后用最大点周边的3*3邻接点来进行灰度重心法核算出光条中心点。具体做法如下:

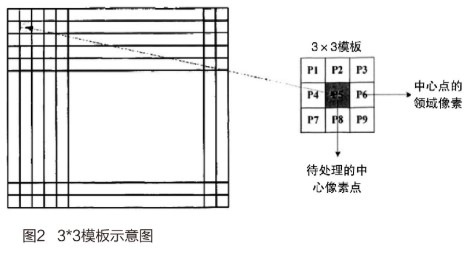

2.2 存储单元

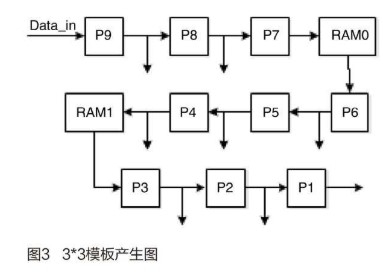

关于算法的完结,还要考虑图画数据的存储结构。这其间包含:点存储器,用来存储需求运算的单个像素点;行存储器,用来缓存需求运算的图画的一行像素点;帧存储器,用来存储整帧图画。一般帧存储器都需求很大的容量,而FPGA内部完结起来比较困难,所以FPGA板都会添加外部存储器,由外部的DDR2 SDRAM 芯片完结[9];为了使进行运算的范畴9个3*3的像素点能在同一时钟输出,便于进行之后的流水线算法模块,因此在3*3的滑动窗的硬件规划中,本文选用了2个RAM存储器来进行行存储。具体操作是:先用两个RAM存储器存储两行数据,比及第三行到来时,再将前两行的数据读出来,之后用9个寄存器存储这9个数据,以确保数据的一起获取[10]。存储结构见图2所示。

这样,当图画像素点串行输入时,通过这种结构的存储器体系,即可得到相应点进行灰度重心法核算所需的一切邻域点的并行输出。

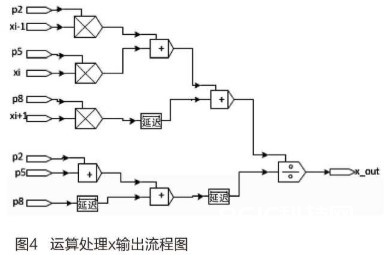

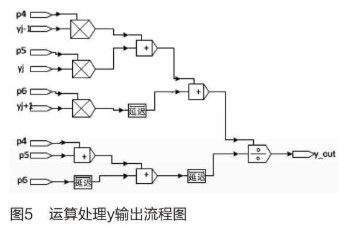

2.3 运算单元

运算单元由乘法器和流水线加法树两部分构成,乘法器的作用是履行运算中的坐标值与像素相乘,流水线加法树的作用是进步运算速度以及削减运算单元占用的硬件资源,该加法数规划为4段流水线结构,榜首段为6个2输入的8位乘法器和2个2输入的8位加法器以及2个推迟单元;第二段为2个2输入的15位加法器和2个2输入的9位加法器以及2个推迟单元;第三段为2个2输入的16位加法器和2个推迟单元;第四段为2个除法器,作用是将运算的像素与像素坐标值的乘积累加后除以运算的像素的累加值,输出的成果即为中心点 的坐标值。运算如图3和图4所示。

3、 FPGA完结的成果

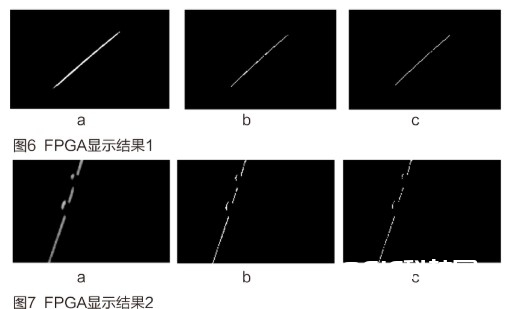

本文FPGA选用的是Altera公司Cyclone III系列的EP3C40F484C6芯片,并在Altera公司的QUARTUS II 软件平台上,运用硬件描绘言语Verilog HDL 表达完结。关于一幅巨细为576行、720列的结构光条纹图画,以每秒25帧的速率抵达时,运用装备为2.53GHz Intel CPU 、3GB内存的通用微型核算机通过软件编程的办法完结对一帧巨细为576行、720列的图画进行提取激光中心线操作,耗时71.5 毫秒。而运用以上专用硬件完结的算法通过仿真的体系最高频率到达100MHz ,高出了体系像素点时钟频率(50MHz ),处理相同的一帧图画需耗时4.1毫秒,速度进步将近20倍,且FPGA逻辑资源占用16% 。足以在视频图画输入的一起完结核算,到达了规划意图。并将体系的收集图片与处理后的图片进行比较,处理成果图6图7所示。图6a、7a为收集图画,图6b、7b为MATLAB处理成果,图6c、7c为EP3C40F484C6处理成果。

试验成果显现能够看出:在精度上FPGA比较PC端稍好,体现在线条的细节体现及线条提取的滑润度上。并且在运行速度上,FPGA提取速度显着优于PC机提取的速度。可是缺乏的是因为模板所取的宽度较小,所以关于一些光带宽度较大,光强横向散布不均匀的图画,正如图7所示,则该办法提取的图形精度不高,图画较为不滑润。这些也将是下一步需求研讨的内容。

4、 结束语

精度和速度是大数据量布景下中心线提取办法的中心目标,本文运用FPGA硬件电路的并行体系结构,将以FPGA为中心的实时处理体系运用结构光三维丈量体系傍边,以硬件方式完结图画光带中心线提取的算法,通过试验标明,关于这些宽度不大且散布均匀的结构光,该办法对中心线提取准确、快速。满意结构光三维丈量的要求。

责任编辑:gt