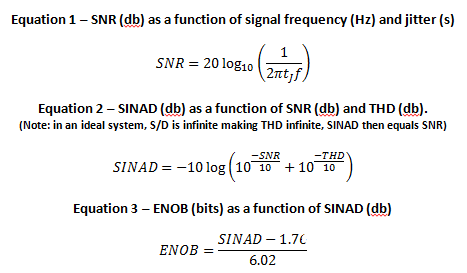

许多人都知道,颤动(这是时钟边缘不确定性)是欠好的现象,其不仅可导致噪声添加,并且还会下降数据转换器的有效位数 (ENOB)。

例如,假如体系需求 100MHz 14(最小值)位的 ENOB,咱们就需求颤动小于 80 飞秒的时钟!这可经过假定一个无失真的抱负体系进行核算,让 SINAD 和 SNR 数值持平(见公式 2)。

接下来,使 ENOB 等于 14,咱们可在大约 86db 下核算出最小 SNR。将成果带入公式 1,核算出大约为 80fs 的 tJ 值。

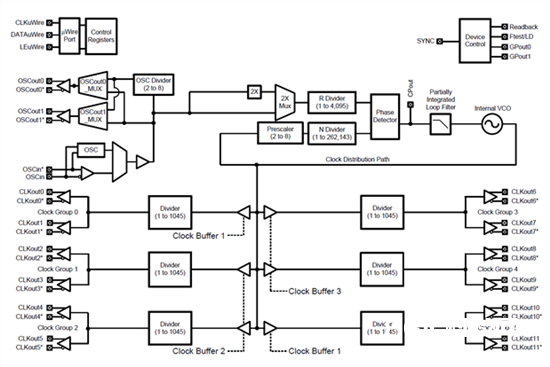

在数字信号处理过程中,采样时钟与处理时钟之间需求有必定相关。也就是说,无论是在十分之一速率下仍是在全速率下采样,样片都必须在其速率的倍数下进行处理,并且要相位共同。这就需求一个“主”时钟,其可用来衍生体系中的一切其它时钟。

您可运用温度补偿晶体振荡器 (TCXO) 和低相位噪声 PLL 完成这一点,可将主时钟明显添加至更高的频率。然后,您可对该最新高频率时钟进行下分频,以供给都与主时钟相相关的剩下体系时钟。这样,采样时钟以及各种数字处理时钟都彼此具有相关性。

现在有许多时钟解决方案,但许多都需求时钟缓冲器或其它时钟分配办法,其可下降全体颤动功用。您可运用如 LMK03806 等一款器材来战胜这个问题,其在同一器材中整合了一切主时钟发生器和时钟分配功用(带驱动器),如图 1 所示。该器材可在 300MHz 下运转的一起,具有缺乏 50fs 的 RMS 颤动(1.875MHz 至 20MHz)。此外,您还可经过对输出进行编程来支撑 LVDS、LVPECL 或 LVCMOS 并对其进行同步,以取得共用上升沿。

图 1 — LMK03806(具有时钟发生器、时钟分频器和驱动器)的方框图

因而,您下次规划采样体系时,别忘了考虑时钟颤动功用,由于这会影响全体动态规模。