摘要

在多核体系构架与并行核算年代,尤其是云核算的呈现,虚拟化技能正迅速开展成为核算体系中的一项核心技能。虚拟化技能供给了体系层次之间的笼统化,并将资源以一个或多个虚拟的运转环境供给给用户。现在对虚拟化的研讨工作首要重视于资源的切割,独立和封装等研讨点,但首要在一个特定处理器体系结构以及处理器同构的前提下。

本项目提出一种新颖的M2M(Multiple ISAs applications to Multiple heter-ogeneous core,M2M)概念,将虚拟化体系分为多核异构层、虚拟化办理层、二进制翻译层、软件使用层四个层次,立异地在传统的虚拟化办理层上添加二进制翻译层,然后引进多个不同体系结构的使用程序,虚拟化办理器调度分配给硬件层引进的异构处理器。M2M的特性使虚拟化体系上层使用的灵活性大大添加,而且硬件异构化也使体系的功率有用进步。

本项目首要奉献点和立异点有:

多指令集体系使用虚拟环境。在使用层供给不同指令集体系构架的虚拟运转环境,以支撑不同使用体系的使用程序。

软硬协同的二进制翻译层。在二进制翻译层,选用软硬协同的办法完结不同架构体系间的动态二进制翻译,进步硬件方针代码生成和运转的功能和灵活性。

规划完结了自主可扩展32位的SoC核。在多核异构层,规划了一个自主,可扩展,可装备的32位RISC处理器。根据此处理器核可装备完结多个RISC SoC渠道(QS-I)。本项目在XUP Virtex-5和Digilent Nexys3 FPGA开发渠道构建了多核异构层。

动态虚拟化办理。在虚拟化办理层,以轻量级的办法完结了体系资源与上层使用的办理。经过资源办理与使命调度动态分配或搬迁运转使命。虚拟层的多个体系结构的使用程序(如x86和MIPS)可动态运转于异构的处理器核上(如处理才干不同的MIPS核)。

供给了体系库和运转程序。在软件使用层,为自主规划的QS-I渠道供给完善的程序运转环境并规划了多样化的使用程序。项目彻底自主地规划完结了体系库(如图形库、I/O库)以及典型的多样化使用软件,包含MIPS下的吃豆子游戏、X86下的推箱子游戏。

1.项目布景

在核算机科学范畴中,虚拟化代表着对核算资源的笼统,而不仅仅局限于虚拟机的概念,完结虚拟化的办法不止一种,不管何种办法都是以不同层次的笼统来完结某一视角对应的作用。

1.1.项目需求

虚拟化技能正迅速开展成为核算体系中的一项核心技能,它供给了核算机体系层次之间的笼统层,并将资源分配以供给一个或多个虚拟的运转环境。现在对虚拟化的研讨工作首要重视于资源的切割,独立和封装等研讨点,但首要在一个特定处理器体系结构以及处理器同构的前提下。本项目提出一种新颖的M2M(Multiple ISAs applications to Multiple heterogeneous core,M2M)概念,将虚拟化体系分为多核异构层、虚拟化办理层、二进制翻译层、软件使用层四个层次,立异地在传统的虚拟化办理层上添加二进制翻译层,然后引进多个不同体系结构的使用程序,并在硬件层引进处理器的异构性。M2M的特性使虚拟化体系的上层使用的灵活性大大添加,而且硬件异构化也使体系的功率有用进步。

1.2.相关技能及其开展现状

本末节将介绍虚拟化以及动态翻译等技能的根本概念及其开展现状。

1.2.1.虚拟化技能的根本概念

虚拟化技能最早可以追溯到上个世纪60年代,IBM公司的System 360体系对运转多个虚拟化体系进行了最早的测验。现在,虚拟化技能正迅速开展成为核算机体系中的一项核心技能,它供给了核算机体系层次之间的笼统层,并将资源分配以供给一个或多个虚拟的运转环境。

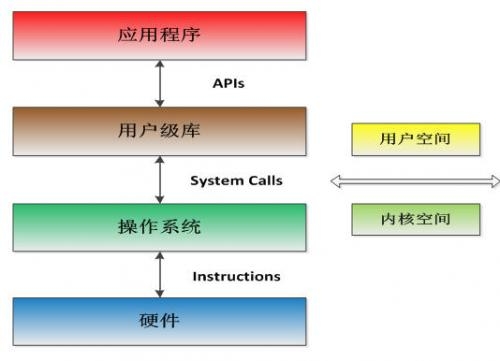

例如核算机体系可分为如图 1中所示的四个层次,由最底层的硬件自下而上分别是操作体系、用户库、使用程序。相应地,虚拟化技能可以针对各个层次进行笼统虚拟,然后为上一层的使用供给一个或多个虚拟环境。

图 1 核算机体系的四个层次

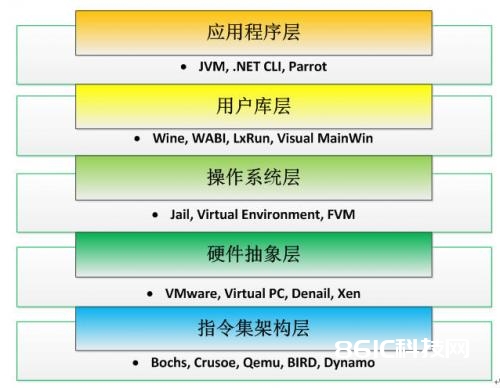

更详细地,虚拟化的层次可分为如图 2所示的指令集架构(ISA)、硬件笼统层(HAL)、操作体系、用户级库、使用程序的五个层次。图 2中还在各个层次下方列出了与其对应的闻名产品。

图 2 虚拟化技能的五个层次及其相应产品

1.2.2.ISA层的虚拟化技能

ISA层的虚拟化是虚拟化技能中的一个重要内容,它的首要意图是为上层使用供给一个或多个不同于物理层实践处理器ISA的ISA笼统层,然后使得多个处理器架构的使用程序可以在同一个处理器上运转,如图 3所示。

图 3 ISA层的虚拟化

ISA层虚拟化所发生的异构性使处理器自身的功能得到进步[1]。一起,x86架构凭仗其强壮的软硬件支撑,仍将在未来的处理器竞赛中占有控制位置[2] 。本项目将要点完结不同ISA(x86和MIPS)之间的虚拟化技能,使该RISC处理器与x86架构抵达二进制兼容。

1.2.3.动态翻译技能

在ISA层的虚拟化中,二进制翻译是最重要的完结技能。二进制翻译是指把一中体系结构的机器码翻译成为另一种体系结构的机器码。经过二进制翻译,体系结构将成为一个软件层,它使得杂乱的留传体系结构可以用简略的硬件来完结,而且使得新颖的体系结构可以兼容本来的软件;此外,二进制翻译可以促进软件的优化[3]。

二进制翻译有两种首要的完结办法,一种是静态翻译,另一种动态翻译。

静态翻译把整个二进制可履行文件翻译成方针体系结构的指令集,它不需求先运转代码,一切的翻译都在编译时完结。所以静态翻译很难做到正确性,由于不是一切的代码都能在编译时被翻译器发现。比方,可履行文件的某些部分只能经过直接跳转才干抵达,而直接跳转的方针值只要在运转时才知道。

动态翻译把一小段源体系结构的代码翻译成方针体系结构的代码并把这一小段生成的代码缓存起来。只要当代码被运转时才开端履行翻译。跳转指令会被指定到现已翻译和缓存起来的代码段上。

2.项目方针及开发渠道挑选

2.1.项目方针及内容

本项目提出一种新颖的M2M(Multiple ISAs applications to Multiple heter-ogeneous core,M2M)概念,在虚拟化办理层上添加二进制翻译层,然后引进多个不同体系结构的使用程序,并在硬件层引进处理器的异构性。如图 4所示的项目整体层次包含多核异构层、虚拟化办理层、二进制翻译层以及软件使用层。

图 4 项目整体层次

本项目方针是根据Xilinx公司的XUP Virtex-5和Digilent的Nexys3 FPGA开发板完结多个RISC SoC渠道树立硬件多核异构层;挑选MIPS和x86 ISA构架规划吃豆子、俄罗斯方块等典型使用程序构成多样化使用场景,完结M2M原型体系。

详细使命如下:

多核异构层

完结MIPS根本指令集,支撑准确中止,含一级Cache的32位RISC CPU的RTL描绘及其验证;

完结VGA(或DVI)、PS/2、SRAM、UART等外设的控制器模块描绘及各个模块的验证;

引进Wishbone总线,集成SoC渠道的各个模块;

根据不同FPGA的RISC SoC渠道(分别在XUP Vritex-5和Digilent Nexys3上根据自主软核QS-I建立了RISC SoC渠道),构建多核异构层

虚拟化办理层

对多核异构层的资源办理;

对使用层多样化程序的调度分配

二进制翻译层

以软硬件协同办法完结RISC处理器在ISA层对x86的虚拟化,使得RISC处理器可以与多架构(如x86)二进制兼容;

动态翻译的软件架构规划

软件使用层

体系软件编写。体系软件包含外设的驱动程序及体系控制程序;

运转环境及库编写。规划完结体系库(如图形库、I/O库);

使用软件编写。使用软件包含多个SoC完好使用体系(x86和MIPS),如简略的游戏程序。

2.2.开发渠道挑选

本项目首要选用Xilinx公司的XUP Virtex-5开发渠道及Digilent公司的Nexys3开发渠道。

2.2.1.XUP Virtex-5 FPGA开发渠道简介

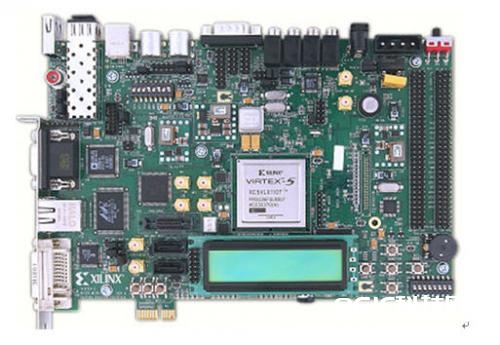

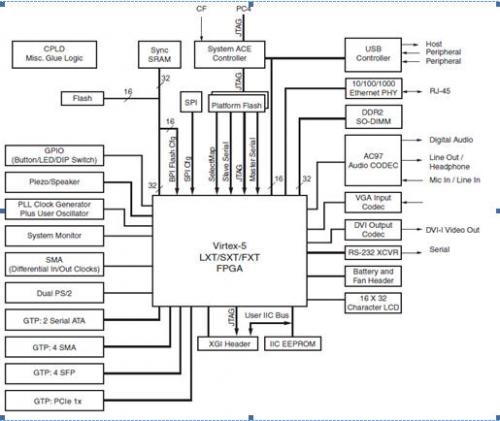

XUP Virtex5是集成了OpenSparcT1开源微处理器的一个强壮体系。其丰厚的特征以及开发渠道的通用性,使得该板卡十分合适在教育及研讨的范畴建立各种体系。如数字规划、嵌入式体系、通讯体系、网络、视频及图画处理等各个范畴。XUP Virtex-5实体图见图 5,其资源模块图如图 6所示。XUP Virtex-5含有丰厚的片上资源以及完好的工业标准接口。

图 5 XUP Virtex-5 FPGA开发渠道

图 6 XUP Virtex-5渠道资源模块

本项目根据XUP Virtex-5 FPGA开发渠道构建了根据自主软核QS-I的RISC SoC渠道。

2.2.2.Digilent Nexys3 FPGA开发渠道简介

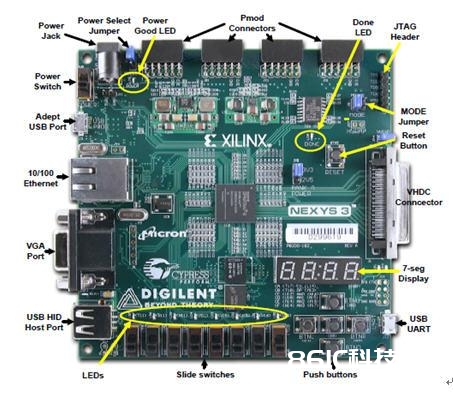

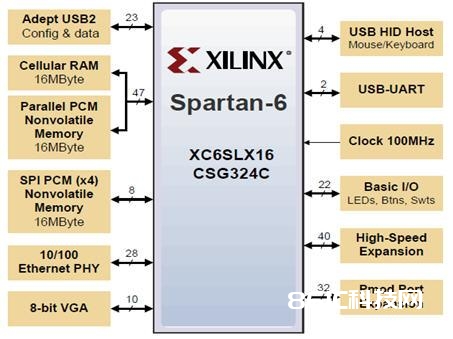

Digilent公司的Nexys3渠道是一个根据Xilinx Sparten-6 FPGA的完好,易用的数字电路开发渠道。Sparten-6 FPGA为高功能逻辑规划做了充沛优化,其片内的block RAM,时钟办理模块,DSP等资源为高档逻辑规划供给了必要硬件根底。Nexys3实体图见图 7,其渠道资源模块如图 8。

图 7 Digilent Nexys3 FPGA开发渠道

图 8 Digilent Nexys3渠道资源模块