TOP1 射频 低噪声扩大器电路

低噪声扩大器电路

射频 LNA规划要求:低噪声扩大器(LNA)作为射频

LNA规划要求:低噪声扩大器(LNA)作为射频 信号传输链路的榜首级,它的噪声系数特性决议了整个射频

信号传输链路的榜首级,它的噪声系数特性决议了整个射频 电路前端的噪声功用,因而作为高功用射频

电路前端的噪声功用,因而作为高功用射频 接纳电路的榜首级LNA的规划有必要满意:(1)较高的线性度以按捺搅扰和避免灵敏度下降;(2)满意高的增益,使其能够按捺后续级模块的噪声; (3)与输入输出阻抗的匹配,一般为50Ω;(4)尽或许低的功耗,这是无线通讯设备的开展趋势所要求的。

接纳电路的榜首级LNA的规划有必要满意:(1)较高的线性度以按捺搅扰和避免灵敏度下降;(2)满意高的增益,使其能够按捺后续级模块的噪声; (3)与输入输出阻抗的匹配,一般为50Ω;(4)尽或许低的功耗,这是无线通讯设备的开展趋势所要求的。

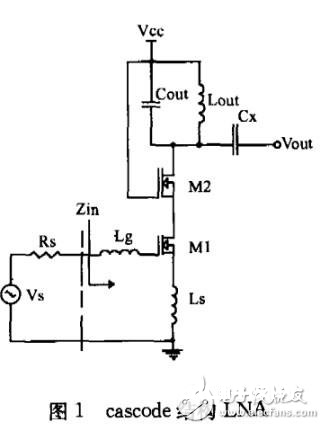

InducTIve-degenerate cascode结构是射频LNA规划中运用比较多的结构之一,因为这种结构能够添加LNA的增益,下降噪声系数,一起添加输入级和输出级之间的隔离度,进步安稳性。InducTIve-degenerate cascode结构在输入级MOS管的栅极和源极别离引进两个电感Lg和Ls,经过挑选恰当的电感值,使得输入回路在电路的作业频率邻近发生谐振,然后抵消掉输入阻抗的虚部。由剖析可知运用InducTIve-degenerate cascode结构输入阻抗得到一个50Ω的实部,可是这个实部并不是真实的电阻,因而不会发生噪声,所以很合适作为射频LNA的输入极。

高安稳度的LNA

cascode结构在射频LNA规划中得到广泛运用,可是当作业频率较高时因为不能疏忽MOS管的寄生电容Cgd,因而使得整个电路的安稳特性变差。关于单个晶体管可经过在其输入端串联一个小的电阻或在输出端并联一个大的电阻来进步安稳度,可是因为新添加的电阻将使噪声值变坏,因而这一技能不能用于低噪声扩大器。

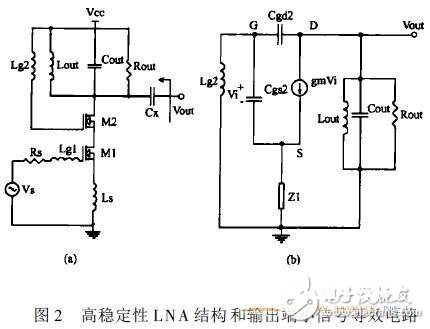

文献对cascode结构提出了改善,在图1的基础上经过在M2管的栅极接上一个小值的电感Lg2就能够完结在增益不变的状况下,进步电路的安稳性,一起在M2管的漏极上接一个小值的电阻以调理电压增益如图2(a)所示。(b)所示的是小信号等效电路,其间Z1代表省掉部分的等效阻抗,能够看到因为M2 管的寄生电容Cgd2的值比较小,所以关于输出端阻抗而言,Lg2简直能够疏忽。因为扩大器的增益等于输出阻抗和输入阻抗值之比,所以添加 Lg2后并没有影响LNA的增益。

其间ZLoad=jwLout//(jwCout)-1//Rout,Zs是源端电感LS的阻抗。

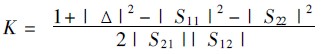

扩大器的安稳系数为[3]

其间Δ= S11S22-S12S21 (6)

安稳系数K能快速给出安稳性判别依据,当K》1,|Δ|《1时,LNA将会无条件安稳。那么由公式(5)和(6)可知,若反向增益S12减小,那么K值将会增大,LNA将会添加安稳性。从图2(b)能够看到,由电感Lg2和MOS管的电容Cgd2组成一个低电阻通路使得从输出端反响回来的信号流向接地端,然后下降了反向增益S12,进步了LNA的安稳度。

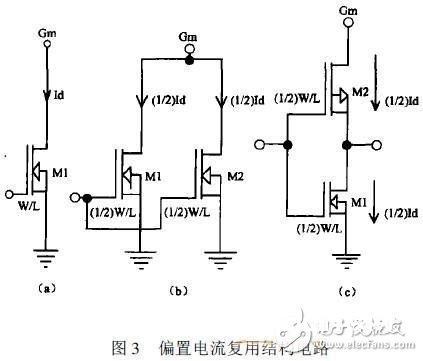

偏置电流复用结构

现代无线通讯设备要求具有更小尺度,更轻重量,更长的待机时刻。这就要求下降射频前端的电源电压,因而低电压、低功耗技能成为迫切需求。由公式(3)可知当输入端处于谐振时Ls=RsCgs/gml,其间Cgs是图1中M1管栅极和源极之间的电容,gml是M1管的跨导。图所示的cascode结构能够取得较小的噪声系数,可是往往需求比较大的漏极电流Id,增大了直流功耗。文献 [4]中提出了偏置电流复用技能,其根本思想是:为了节约直流功耗,能够将PMOS管和NMOS管串联在直流偏置通路里,对其结构的阐明如图3所示。

图3(a)所示的单个NMOS器材的宽长比和漏极电流Id都是(b)所示的单个NMOS的两倍,但因为两个NMOS并联,因而(a)和 (b)具有相同的跨导值gm。(c)中的M2是PMOS管,且和(b)中的NMOS管具有相同的宽长比,因为PMOS器材的电子迁移率比NMOS稍低 [2],所以gmc=(gml+gm2)m,即其跨导值略低,而它的输入电容和Cgs近似。由(7)式可知(c)电路结构的噪声系数将略增一点,可是因为电流减小了一半,因而在电源电压必定的状况下能够有用下降电路的功耗,有利于低功耗LNA规划。

TOP2 轿车收音机射频电路规划

轿车收音机运用环境的特殊性对电路功用具有更高的要求,而射频电路的规划是完结高功用的要害。本文介绍了TDA7513的射频电路规划办法,依据实践规划经历提出了进步射频电路EMC特性和噪声特性的规划办法和办法,并指出了射频电路功用测验的留意要害。射频电路是收音机电路规划的要点和难点,假如射频电路规划欠好,收音机的噪限灵敏度和信噪比以及其它技能方针都会大大下降,乃至只能手动收到很少的几个播送电台,主动查找电台功用失效。从收音机天线端的播送信号场强来看,信号的动态规模非常大,尤其是轿车收音机所在的环境改动快而大。

收音机射频电路一般很难集成进%&&&&&% 中,一般由别离元件组成前置低噪声扩大器(LNA)和谐振带通滤波器。轿车收音机射频电路的效果从时域上看是要将弱小的播送信号扩大,经过主动增益操控电路(AGC)为后级混频器供应安稳的载波信号强度;从频域上看,它要盯梢所挑选的电台信号,滤除去搅扰信号如镜像频率(》60dB按捺)和本振频率,改善射频信号质量。

射频电路规划

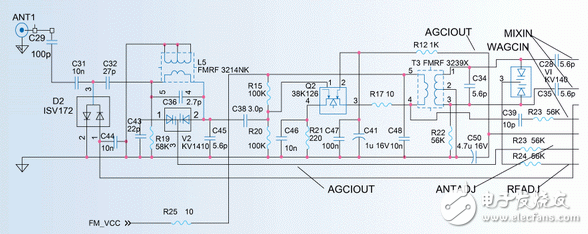

图1是咱们规划的轿车收音机射频电路方框图,它由天线滤波器和射频低噪声扩大器以及谐振带通滤波器组成。该款轿车收音机的规划方针是噪限灵敏度为 0dBu(30dB S/N)、音频信噪比64dB、主动查找灵敏度小于10dBu,具有较强的抗邻频道搅扰和其它搅扰信号才能,完结MCU全主动调整功用。

图2是轿车收音机TDA7513的FM收音机部分射频前端电原理图。C31、C32、D2(1SV172)、 C44组成调频波段天线信号调理电路,1SV172是VHF~UHF频段天线信号衰减器,它是电流操控型元件,跟着电流的增大其阻抗减小。它受控于后级 FM宽带AGC和窄带AGC组成发生的FMAGC电流,起控点为天线信号电平57dBu。L5、C36、V2(KV1410)、C43、R19、C45组成天线带通滤波器,带宽为12MHz左右。该天线滤波器能够人工用无感调批调理射频线圈L5,也能够经过MCU调理变容二极管V2,然后完结主动调整功用。

Q2(3SK126)、C38、R15、R20、C46、R21、C47、C41、R17组成低噪声射频扩大器,增益为30dB。本规划中选用N沟道场效应管3SK126作射频扩大器具有输入阻抗高、增益高和噪声低的长处,而且是电压操控型器材,规划简略。Q2受控于后级FM宽带 AGC和窄带AGC组成发生的FMAGC电压,起控点为天线信号电平78dBu。T3、C34、V1(KV1410)、C28、C35组成RF谐振带通滤波器,带宽为8MHz左右,T3为FM RF变压器。该带通滤波器相同能够人工用无感调批调理T3,也能够经过MCU主动调理变容二极管V1。接纳机的接纳极限是由接纳机本身噪声功用决议的,所以在收音机的射频电路中要求尽量选用低噪声元件。

高频RFID射频电子电路规划原理剖析

高频RFID频率是13.56MHz的,以最常用的RC500为例,射频输出两个脚TX1,TX2,接纳一个脚RX,别的一个是RX的偏置电压 VMID,让RX信号偏置到1/2电源电压方位,确保接纳功用最好。TX1和TX2输出13.56MHz的方波,别离经过 L200、C213和L201、C212来完结把方波谐振,升压,一起把其它的谐波去掉,一般主张L200或许L201用定值电感,如1uH或许 2.2uH,这个质量比较重要,我一般选用创易出售的sagami电容,1uH。调理C212和C213(默许能够先用150pF的,之后10pF邻近调理),使C212、C213两头电压最大(不必太准),峰峰值能够到达50V,一般主张在30V以上即可,这个视需求定,太高,电流会过大。

电路如下:

C214与天线完结在13.56MHz谐振,天线尽或许面积大一些,比方1平方分米,距离非常好,圈数就1,2圈,若面积比较小,则圈数略微多一些,比方6平方厘米,那么圈数就要6圈,线圈的中心能够接地,这样是为了进步抗静电才能。调理C214让C214两点峰峰值最大,一般能到达30V以上,留意调试的时分,必定要把终究的环境考虑进步,而不是独自的调试天线,环境包含卡,外壳,金属件等,尤其是卡和金属件,对天线的功用影响很大,能够理解为下降了天线的电感量。当调试好天线的谐振之后,前面的升压谐振有必定的改动,再一次调试一下,经过这样,一般都能调试出比较满意的效果。留意电压不要调的太高,一是耗电过大,二是因为Q值过高,导致频带过窄,接纳反而受影响,这个时分恰当下降一下电压,三是电容发热过高,一般主张电容用 0805封装的为好。RFID的信号发射是调制在TX输出的13.56MHz载波上,卡从载波上获取能量当作电源,一起依据调制在载波上的信号进行指令的处理,当RC500接纳的时分,RC500持续输出载波,卡端经过对天线不断的短路,断路来影响载波的起伏,这个便是知名的载波调制技能,为了让接纳灵敏度进步,一般选用副载波负载调试技能,也便是说,卡端先对 13.56MHz/32=423.75K的信号进行调制,之后用423.75KHz再去调制RC500辐射的载波,这个423.75KHz有点相似中频信号,对进步信号的灵敏度有长处。

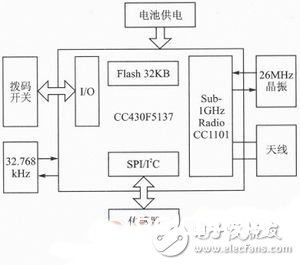

TOP3 低功耗射频无线数据收集电路

无线传感器网络是由布置在监测区域内很多的廉价微型传感器节点组成的网络。它是由很多的中止或移动的传感器以自安排和多跳的办法构成的无线网络,以协作的办法感知、收集、处理和传输网络掩盖地舆区域内被感知方针的信息,并终究把这些信息发送给网络所有者。无线传感器网络首要完结了数据的收集、处理和传输三种功用。传感器网络节点一般遭到作业环境的影响,功耗问题是要首要考虑的。考虑到低功耗要求的规划,节点设备的主控MCU挑选 CC430F5137,运用它内置的射频通讯模块进行射频通讯。因为其低功耗的特色可选用电池供电。软件部分运用CC1101的无线唤醒功用,能史好地下降体系功耗。

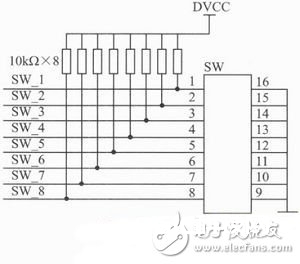

无线传感器网络中能够挂接多个节点设备,而每个节点设备的地址有必要仅有。本文规划的节点设备选用拨码开关来设置每个节点设备的地址,确保每个节点都有一个仅有的地址。经过SPI接口或I2C总线接入传感器器材,能够灵敏地接入不同类型的传感器器材,以到达测验不同物理量的要求。节点的体系结构如图1所示。

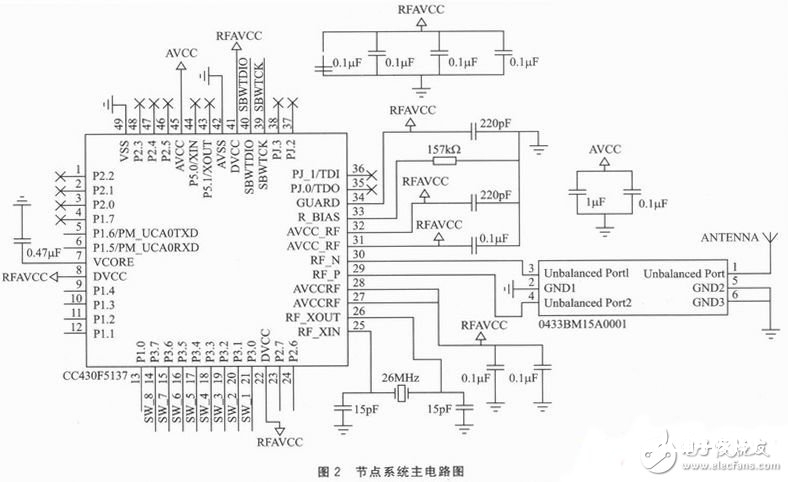

节点电路全体规划

CC430F5137的供电电压规模为1.8~3.6 V,选程度用两节7号电池来供应3 V的直流电压。合作软件的设置能够最大程度地下降功耗。体系的要害部分是射频发送运用一个射频的天线模块,能够确保射频通讯的安稳性,此无线模块由芯片的 RF_N和RF_P两个引脚接入。别的依据射频发送的需求,接入一个26 MHz晶振。CC430F5137的P1.5、P1.6、P1.7引脚能够用于串口通讯和SPI通讯,运用这三个引脚作为串口调试,别的P1.1、P1.2、P1.3引脚能够用于SPI和I2C总线通讯,这三个接口用来预留衔接传感器的芯片。体系的主电路图如图2所示。

地址设定电路

为了使每个节点的地址仅有,选用8位的拨码开关SW进行地址设定。如图3所示,能够由拨码开关来设定终端节点的地址,能够设定255个不同的地址,每一个终端节点作为从设备向中继节点发送数据,然后由中继节点发送到用于网络办理的主控MCU,完结无线传感器网络数据的传送。

本文运用TI公司的CC430F5137芯片,选用射频通讯技能规划的无线数据收集节点,这种规划能够大大地减小体系的体积。本体系能够收集各式各样的信号,能将收集到的数据安全安稳地传送到中心数据收集点。规划中载波监听功用和信道闲暇评价功用改善的射频发送函数,能够有用地进步多个节点一起发送数据时的抗搅扰性。

TOP4 跳频电台射频前端电路

跟着DSP技能的开展,电子器材制造工艺的进步,A/D、D /A的取样速率越来越高,无线电台中的数字处理不断往射频前端推动,信道可重构的才能不断得到进步,体系能够直接从中频采样,进行数字信号处理。本计划接纳机射频前端体系依据软件无线电理 论来规划和完结,以到达树立一个通用化、规范化、模块化的接纳机射频前端体系仿真渠道的方针。以完结接纳机射频前端体系低噪声系数,小的互调失真,大的动 态规模和镜像按捺,杰出的AGC,满意的增益和正确的挑选性等规划要求。经过对接纳机射频前端的规划计划可行性剖析和运用射频电路仿真软件ADS进行体系 建模规划与参数仿真,完结接纳机射频前端电路规划的体系功用。

射频前端体系计划规划及可行性剖析

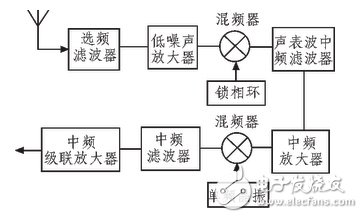

本接纳机射频前端首要任务是对信号进行滤波、混频、 扩大的功用,并对体系或许遭到的镜像搅扰频率、互调搅扰频率进行按捺。体系功用模块首要包含滤波器、混频器、扩大器及本振等。体系作业频率规模为 100~150MHz,其间每10MHz带宽作为一个信道用于跳频调制,选用超外差二次混频的结构,整个射频前端体系的规划增益为110dB,体系噪声为 3dB。其原理框图如图1所示。由图1能够看出,选频滤波器后的扩大器为低噪声扩大器(LNA),LNA的噪声系数对整个体系的噪声系数起决议性的效果。 规划时在增益、噪声系数、动态规模、VSWR、安稳性等方针之间进行平衡。榜首级混频经过PLL改动榜首级本振频率,以接纳不同信道的射频信号,经下变频 把接纳信号搬移到中频为70MHz、频率带宽为10MHz的频带上。

图1、接纳机射频前端原理框图

在此过程中,混频器是一个非线性器材,会引进很多交调重量,使得混频后呈现很多的组合搅扰频率点,对有用信号形成严峻的搅扰,直接影响着接纳机功用。声表波 中频滤波器针对混频或许呈现的镜像频率搅扰,进行对中频信号高品质的频率挑选性滤波,到达进步镜像频率按捺的规划方针。第二级混频把中频为 65~75MHz的频带信号搬移到10~20MHz,如图2所示(虚线为一次混频镜像频率,灰色为第2次混频镜像频率)。因为其作业频率相对较低,二次混 频后的频带信号经过主动增益操控扩大器级联扩大发生72dB左右的增益,其高增益也更简略完结、更安稳。

图2、频谱及镜像剖析图

射频前端体系建模与功用仿真及剖析

运用ADS2008软件对接纳机射频前端建模,设置各模块 参数,选频滤波器针对输入射频信号100~150MHz进行滤波。LNA噪声系数3dB,增益24dB,锁相环输出本振信号别离为175、185、 195、205、215MHz。SAW中频滤波器中心频率为70MHz,频率带宽10MHz。一次混频和二次混频后中频扩大器别离发生28dB和72dB 增益,如图3所示。

图3、接纳机射频前端体系仿真框图

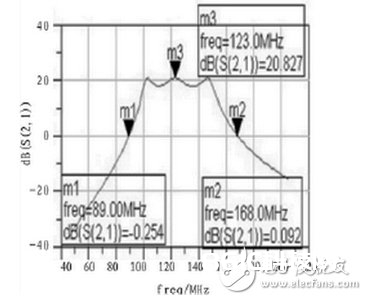

射频前端体系频带挑选性仿真

接纳机射频前端体系的频带挑选性的功用,首要由射频 前端的选频网络所决议。选用传统LC滤波器,经过调理榜首级本振的输入频率,改动选频网络的中心频率,设置本振为195MHz,完结对 120~130MHz射频信号的下变频处理。在ADS中建立榜首级混频电路模块的仿真原理图。由图4能够看出,接纳机在123MHz处最大增益为 20.827dB,也便是LNA的增益减去滤波器的插入损耗。选频滤波器能很好对240~290MHz镜像搅扰信号进行按捺。

图4、选频网络S参数仿真

本文在软件无线电体系理论基础上,对宽带接纳机射频前端体系选用超外差式二次混频结构,树立了一个通用化、规范化、模块化的接纳机射频前端体系仿真渠道。从功用仿真成果能够看出,该计划能够很好地运用在软件无线电射频前端电路中,能够到达规划要求。

TOP5 WLAN射频优化电路

无线局域网(WLAN)是依据IEEE 802.11规范、运用免费的ISM频段射频资源完结的局域网络衔接。IEEE 802.11的榜首个版别的规范由IEEE在1997年拟定,该规范界说了媒体访问操控层和物理层。其间,物理层界说了作业频率为2.4GHz的ISM频 段,总数据传输速率为2Mb/s。

此外,为完结更高的数据吞吐量,2013年WiGig安排并入了WiFi联盟。WiGig致力于推行IEEE 802.11ad规范,该规范选用60GHz频段,供应最高7Gb/s传输速率的短距离无线通讯服务。因为60GHz信号无法穿透障碍物,当终端设备进入 WiGig信号无法掩盖的区域时,将主动切换到更低频段,可是传输速率将大幅下降。

表1总结了IEEE 802.11规范演进的进程,从中能够看出WLAN规范的每一次晋级和弥补,其成果无非便是为了得到传输速率/吞吐量。为了完结这一方针,能够选用以下两 种手法。1、选用更宽的信道带宽。为完结这一意图,有时就需求进步作业频段。因而,WLAN现已从开端的2.4GHz逐渐向5GHz过渡,而且现已呈现了 60GHz的规范,然后能够运用更宽的频谱资源。2、选用空间复用技能。从IEEE 802.11n开端,MIMO技能被引进WLAN,而且最大空间串流也在IEEE 802.11ac中得到添加。

表1:WLAN物理层规范演进

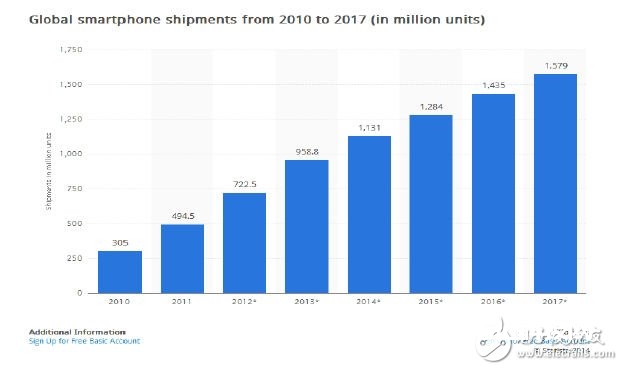

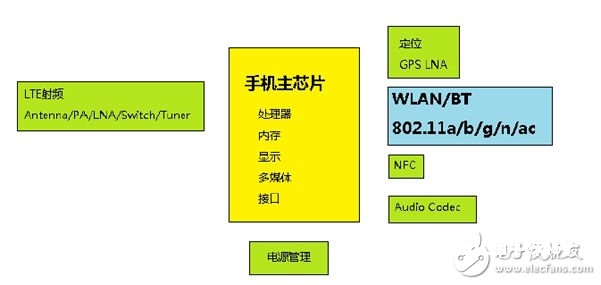

2010年以来,全球智能手机的 出货量稳步增长。如图1的估计所示,到2017年,全球智能手机每年的出货量将挨近16亿部。在智能手机中,因为工艺的差异,手机主芯片一般不会集成 WLAN的射频电路。关于主芯片,WLAN的射频电路归于外围芯片,如图2所示。WLAN规范的不断进步要求WLAN射频电路除了要支撑5GHz的 IEEE 802.11ac的需求,也要对IEEE 802.11a/b/g/n作向下兼容支撑,此外,还要统筹到与2.4GHz WLAN规范同频的蓝牙(BT)的共存。

图1:全球智能手机出货量计算

图2:智能手机内部架构

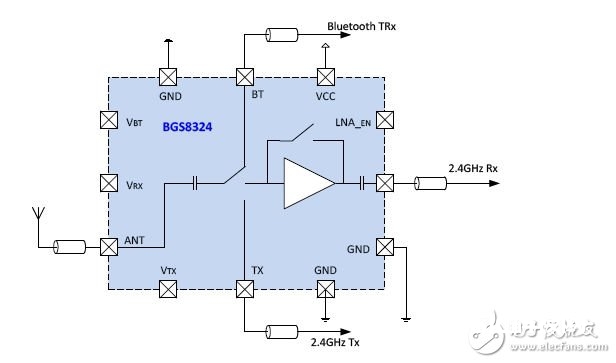

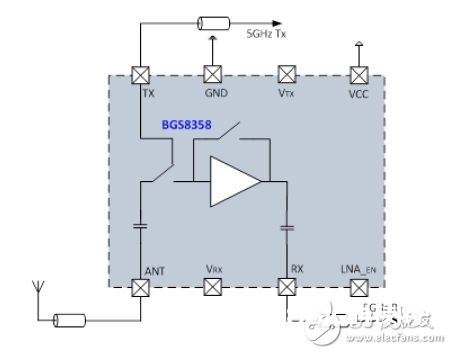

为满意对智能手机WLAN衔接规范不断进步的需求,恩智浦半导体行将推出两款集成开关的低噪声扩大器芯片(LNA+SW)BGS8324(图3)和BGS8358(图4)。

图3:BGS8324 2.4GHz (IEEE 802.11b/g/n)前端芯片架构

图4:BGS8358 5GHz (IEEE 802.11a/n/ac) 前端芯片架构

BGS8324是作业在2.4GHz频段的WLAN接纳前端芯片,支撑IEEE 802.11b/g以及IEEE 802.11n的2.4GHz频段,一起统筹蓝牙的共存。该产品选用2mm×2mm的QFN封装,无需外部匹配器材,具有体积小、功耗低、规划简略等特 点。该芯片支撑2.7V到6V的电压,具有接纳扩大、直通、发射和蓝牙四种办法,并内置对5.8GHz共存信号的防堵塞功用。BGS8358是作业在5GHz频段的WLAN接纳前端芯片,支撑IEEE 802.11a/ac以及IEEE 802.11n的5GHz频段。该芯片选用1.5mm×1.5mm的QFN封装,相同不需求外部匹配器材,具有体积小、功耗低、规划简略等特色。该芯片支 持2.7V到6V的电压,具有接纳扩大、直通和发射三种办法,并内置对2.4GHz共存信号的防堵塞功用。

本文回忆了WLAN的物理层规范IEEE 802.11的演进进程,剖析了该规范每次批改经过作业带宽的添加以及MIMO技能的运用使得数据吞吐量大幅进步的趋势。考虑到WLAN在智能手机中的广 泛运用,为投合最新的WLAN规范,恩智浦半导体推出了用于智能手机WLAN射频计划的BGS8324和BGS8358两款产品,以兼容IEEE 802.11a/b/g/n/ac各种规范,一起,还统筹到2.4GHz频段蓝牙的共存。这两款产品具有体积小、功耗低、规划简略等长处,具有宽广的商场 远景。

TOP6 射频前端功率扩大偏置电路

偏置电路:有扫描成果能够得到管子作业点的各项参数。为确保管子一直作业在线性扩大区,挑选直流作业点为VDS=5V,IDS=0.8A,VGS=-0.4V。 由模仿电子技能的常识可得,偏置电路可有两种办法:自偏压电路和分压式自偏压电路。

自偏压电路比较简略,可是当静态作业点承认之后,VGS与ID就承认了,因而R的挑选的规模很小。分压式自偏压电路是在其基础上加接分压电阻后组成的。漏极电源VDD经过火压电阻R5和R1分压后,经过R4供应栅极电压VG=R1*VDD/(R1+R5),一起漏极电流在源极电阻R3上也发生压降 VS=ID*R3,可知静态时加在FET上的栅源电压? 。

图中C1、C2为隔直电容,C3去耦电容,L1、L2为去耦电感。因为在大信号仿真时为了进步电源功率,故挑选Vdd的值比较小。R3、R4的值比较小也是为了下降消耗在其上的直流功率,而进步电源的功率。

选用RFID技能的车辆办理体系电路详解

RFID技能在商场上被广泛运用。在国外,射频标签已被广泛运用于工业主动化、商业主动化、交通运送、物流等很多范畴。其特有的高准确率和方便性大大下降了企业的物流本钱,进步了企业的商场竞争力和服务功率。本文规划了完好的智能车库操控体系,车库模型全体选用“回”字规划计划,此计划在模型车库中现现已过验证和实践的信息收集,能够满意实践运用。硬件部分以STC公司出产的STC 11F32XE单片机作为操控中心,对体系硬件进行了全体规划,并对硬件体系中各个功用模块的详细规划进行了以下详细介绍。

智能小车的规划,彻底按照了国家级机器人比赛规范,车辆选用直流电源供电,便于体系对电源的办理和尽或许的下降设备的功耗。稳压芯片在电源和操控器以及其他设备之间的衔接,既能够使体系电源供应咱们所需求的电流电压,又能够有用的维护电源。运用STC 89C58单片机作为模仿车的操控器,能够对车辆运转中的改动做出及时反响,便于模仿人驾驭车辆正在进行行进,中止,撤退等进、出车库的操作。归纳考虑需求和本钱,选用STC 11F32XE单片机微处理器作为操控中心。STC 11F32XE单片机在整个体系中,从读卡模块读取信息,及时处理获取到的信息并将处理成果传回给卡片,完结信息交流。

程序下载模块电路图如图1所示,首要在芯片没有作业的时分,PC机经过串口(DB9)发送信号给STC 11F32XE芯片,让芯片处于等候下载状况。当给单片机上电的时分,电脑终端和MAX232芯片经过T1OUT0和R1IN0衔接,转化电平后,终究经过T1OUT0和R1IN0衔接到方针芯片,经过整个电路回路,完结程序的下载。

MAX232芯片在此下载电路中,由1、2、3、4、5、6脚和4只电容发生+12v和-12v两个电源,供应给RS-232 串口电平的需求。由TTL/CMOS数据从T1IN、T2IN输入转化成RS-232数据从T1OUT、T2OUT送到电脑DB9插头;DB9插头的 RS-232数据从R1IN、R2IN输入转化成TTL/CMOS数据后从R1OUT、R2OUT输出,完结电平转化。

射频辨认模块

射频辨认部分电路如图2所示,磁卡进入天线发生的磁场后,接纳解读器宣布的射频信号,凭仗感应电流所取得的能量经过TX1和 TX2发送出存储在芯片中的产品信息,解读器RC522读取信息并解码后,经过M-MFMOSI、M-MFMISO和M-MFRST送至STC 11F32进行 有关的数据处理。

MF RC522芯片运用其先进的调制和解调概念,在13.56MHz下的被迫非触摸式通讯办法和协议。使其内部发送器部分经过TX1和TX2驱动读写器天线与 ISO 14443A/MIFARE卡的通讯。硬件接纳器部分供应了一个巩固而有用的解调和解码电路,用于处理ISO14443A兼容的应对信号。与STC 11F32XE经过M-MFMOSI、M-MFMISO和M-MFRST衔接中的通讯选用连线较少的UART(相似RS232)办法,数据传输速率高达 424kbit/s,有利于削减连线,缩小PCB板体积,下降本钱。

TOP7 射频低噪声扩大电路

液晶显现模块

显现电路如图3,选用12864液晶屏,运用该点阵的中文字库,显现咱们在实践运用场景中的对客户和对自己的同一操作的一致可视化操作。

整个智能车库的规划,全面考虑了实用性和安稳性。对现在很多运用的传统车库和制造的车库模型运用状况进行数据计算和剖析,每个泊车区在功用和结构上,都采取了独立的规划计划,在实践运用的过程中,能够依据需求,在现有车库模型的基础上,对泊车区按实践需求进行增减,以满意泊车需求。在程序规划过程中,依据磁卡不同的操作场景,设置成多个作业办法,尽或许的下降程序间的相互影响,到达体系的通用性和无误操作。

从概念上来讲,RFID 相似于条码扫描,关于条码技能而言,它是将已编码的条形码附着于方针物并运用专用的扫描读写器运用光信号将信息由条形磁传送到扫描读写器;而RFID则运用专用的RFID读写器及专门的可附着于方针物的RFID单元,运用RF信号将信息由RFID单元传送至RFID读写器。RFID单元中载有关于方针物的各类相关信息,如:该方针物的称号,方针物运送起一直止地址、中转地址及方针物经过某一地的详细时刻等,还能够载入比如温度等方针。RFID单元,如标签、卡等可灵敏附着于从车辆到载货底盘的各类物品RFID技能所运用的电波频率为50KHz-5.8GHz,如图一所示,一个最根本的RFID体系一般包含以下几个部份:

一个载有方针物相关信息的RFID单元(应对机或卡、标签等); 在读写器及RFID单元间传输RF信号的天线; 一个发生RF信号的RF收发器(RF transceiver);一个接纳从RFID单元上回来的RF信号并将解码的数据传输到主机体系以供处理的读写器;天线、读写器、收发器及主机可部分或悉数集成为一个全体,或集成为少量的部件。不同制造商有各自不同的集成办法。

典型的射频电路

射频电路最首要的运用范畴便是无线通讯,图1为一个典型的无线通讯体系的框图,下面以这个体系为例剖析射频电路在整个无线通讯体系中的效果。

这是一个无线通讯收发机的体系模型,它包含了发射机电路、接纳机电路以及通讯天线。这个收发机能够运用于个人通讯和无线局域网络中。在这个体系中,数字处理部分首要是对数字信号进行处理,包含采样、紧缩、编码等;然后经过A/D转化器转化器变成模仿办法进入模仿信号电路单元。

射频电路的组成和特色

下面,将针对图方框图中的低噪声扩大器(LNA)评论一般射频电路的组成和特色。

上图给出了这个扩大器的电路板图, 留意到输入信号是经过一个经过匹配滤波网络输入扩大模块。扩大模块一般选用晶体管的共射极结构,其输入阻抗有必要与坐落低噪声扩大器前面的滤波器的输出阻抗 相匹配,然后确保最佳传输功率和最小反射系数,关于射频电路规划来说,这种匹配是有必要的。此外,低噪声扩大器的输出阻抗有必要与其后端的混频器输入阻抗相匹 配,相同能确保扩大器输出的信号能彻底、无反射的输入到混频器中去。这些匹配网络是由微带线组成,在有些时分也或许由独立的无源器材组成,可是它们在高频 状况下的电特性与在低频的状况下彻底不同。图上还能够看出微带线实践上是必定长度和宽度的敷铜带,与微带线衔接的是片状电阻、电容和电感。

射频电路的功率和增益

增益、噪声和非线性是描绘射频电路最常用的方针。在射频和微波体系中,因为反射的普遍存在和抱负的短路、开路难以取得,低频电路中常用的电压和电流参数的丈量变得好不简略,因而,功率的丈量得到了广泛的运用。而且,传统的射频和微波电路运用分立元件和传输线构成,电路的输入、输出一般需求匹配到一个体系阻抗(50?或75?)。因为上面两个原因,电路的功用方针,如增益、噪声、非线性等,都能够经过功率表示出来。

TOP8 测验环路滤波器及射频电路

本文以ADF 4153型小数分频频率组成器为例,给出了简略完结的三阶环路滤波器的规划办法,能够满意芯片实践测验的需求。

外接环路滤波器的规划

环路滤波器是电荷泵锁相环电路的重要环节,它衔接在电荷泵和压控振荡器之间。锁相环的根本频率特性是由环路滤波器决议的。实践上,正是因为环路滤波器的存在,锁相环才能够挑选作业在恣意的中心频率和带宽内。环路滤波器的类型多种多样,大致分为有源滤波器和无源滤波器两大类,无源滤波器与有源滤波器比较,其长处在于:结构简略、低噪声、高安稳度和易以完结。

最常见的无源滤波器是如图1所示的三阶滤波器。一般来说,环路滤波器的带宽应为PFD频率(通道距离)的1/10.进步环路带宽会缩短确认时刻。但环路带宽过大会大起伏地添加不安稳性,然后导致锁相环无法确认的状况。

图1三阶环路滤波器

环路滤波器规划参数的挑选

为了研讨环路滤波器对锁相环输出频率相位噪声的影响,规划出契合芯片测验需求的外围环路滤波器。咱们在ADIsimPLL软件中进行了如下仿真装备。器材类型:ADF 4153,fPFD=25MHz(抱负信号源),INT=69,FRAC=101,MOD=125,VCO选用ZComm公司的V674ME34-LF,在该装备下,预期输出的RFOUT=1.7452GHz.

a)设定环路滤波器带宽为20kHz,相位裕度50°,其相位噪声的仿真状况如图2所示。

图2环路带宽20kHz时的相位噪声仿真图

从图2中能够得知,当环路滤波带宽为20kHz时,VCO所引起的相位噪声占有了主导地位。芯片所引起的相位噪声则被淹没在总输出噪声之下。换句话说,当环路带宽较窄(如20kH)的状况下,针对锁相环输出信号进行相位噪声测验,其成果并不能真实地反映芯片输出的相位噪声。

设定环路滤波器带宽为100kHz,相位裕度50°,其相位噪声的仿真状况如图3所示。

图3环路带宽为100kHz时的相位噪声仿真图

从图3中能够得知,当环路滤波带宽为100kHz时,VCO关于总相位噪声的奉献显著地下降,芯片所引起的相位噪声占有了主导地位,在10kHz以内,总相位噪声输出的曲线根本与芯片所引起的相位噪声重合。由此能够得知,当环路带宽较宽(如 100kHz)的状况下,针对锁相环输出信号进行相位噪声测验,其成果根本能真实反映芯片输出的相位噪声。

本文研讨的ADF 4154的首要测验频点为1.7452GHz(fPFD=25MHz,RSET=5.1k),依据测验要求进行归纳的考虑,设定了环路带宽75kHz,相位裕度50°的约束条件。在进行ADF 4153的外围电路规划时,首要需求承认所运用的VCO类型及其标称功用。然后再依据ADI公司供应的ADIsim-PLL软件进行三阶环路滤波器的规划。从软件得出C1~C3、R2、R3的详细取值,再依据现有的标称电容电阻值进行调整,反算出实践规划的环路带宽及相位裕度。

由此,咱们承认了环路滤波器中各个电容、电阻的取值,并规划了可用于ADF 4153芯片测验的电路原理图,如图4所示。VCO的输出不只需求衔接外部频谱仪进行测验,还需求经过%&&&&&%反响到ADF 4153的REFINA端,一起REFINA端还需求预留SMA头用于射频输入频率规模及灵敏度测验。一个简略的电阻网络用于完结VCO输出信号功率的再分配。

图4环路滤波器及射频电路规划

本文首要依据芯片测验意图,针对外围电路中的环路滤波器规划来进行评论,文中给出了一种简略、易行的工程化计算办法和流程,并对其进行了验证测验,测验成果满意芯片测验的需求。这种办法现已运用于多款小数分频频率组成器的测验电路的规划中。