本文主要是先论述传统Gardner算法的原理,然后给出改善后的规划和FPGA完结办法,终究对成果进行仿真和剖析,证明该规划计划的正确、可行性。

0 导言

数字通讯中,位同步功能直接影响接纳机的好坏,是通讯技术研究的要点和热点问题。通讯体系中,接纳端发生与发送基带信号速率相同,相位与最佳判守时间共同的守时脉冲序列,该进程即称为位同步。常见的位同步办法包括滤波法和鉴相法。滤波法对接纳波形进行改换,使之含有位同步信息,再通过窄带滤波器滤出,缺陷是只适用于窄带信号。最为常用的位同步办法是鉴相法,包括锁相法和内插法两种。锁相法选用传统锁相环,需求不断调整本地时钟的频率和相位,不合适宽速率规模的基带码元同步。而内插规律运用数字信号的内插原理,通过核算直接得到最佳断定点的值和相位。

Gardner算法便是依据内插法的原理,通过守时环路调整内插核算的参数,然后盯梢和锁定位同步信号,该算法的长处在于不需求改动本地采样时钟,能够习惯较宽速率规模内的基带信号,因此具有传统办法不行替代的优势。Gardner算法的完结办法,为算法的运用供给了根底。Farrow结构十分合适完结Gardner算法的中心,即内插滤波器部分,其长处是资源占用较少,且滤波器系数实时核算,便于内插参数调整。守时差错检测,但在守时差错检测时需求信号中存在断定信息,而且对载波相位差错灵敏。缺乏进行了改善,提出了GA-TED(Gardner TIming Error DetecTIon)算法,其长处是不需求预知断定信息,且独立于载波同步,而且合适FPGA 完结。改善的Gardner 算法,并将其运用于M-PSK 体系。提高了Gardner 算法的抗自噪声才能,即降低了对本地时钟的要求。

本文依据FPGA 渠道并选用Gardner 算法规划,其间,内插滤波器选用Farrow 结构,守时差错检测选用GA-TED算法。一同对传统Gardner算法结构进行了改善,使环路滤波器和NCO的参数可由外部操控器设置,以习惯不同速率的基带码元,完结通用的位同步器的规划计划。此外,本规划计划还对FPGA 代码进行了优化,节约了很多硬件资源。终究进行了仿真和剖析,给出了仿真成果,证明了该计划的可行性。

1 传统Gardner 算法与改善

1.1 传统Gardner算法基本原理

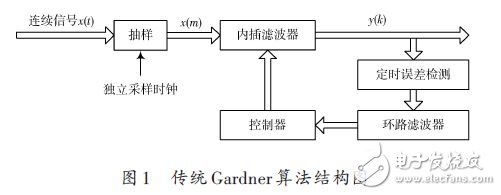

传统Gardner算法结构如图1所示。

在图1中,输入的接连时间信号x(t) 码元周期为T,频带受限。在满意奈奎斯特定理的条件下,接纳端选用独立时钟对x(t) 进行采样。内插滤波器核算出内插值y(k),送至守时环路进行差错反应和参数调整,并与操控器输出的位同步脉冲BS一同送往解调器的抽样断定器。

守时环路包括守时差错检测、环路滤波器和操控器。守时差错检测提取插值时间和最佳判守时间的差错;该差错经环路滤波器滤除高频噪声后送给操控器;操控器核算插值时间(即为位同步信号的2倍频)和差错距离。插值时间和差错距离用于调整内插滤波器的系数,使插值时间尽可能与最佳断定点同相,终究完结位同步信号的提取。

1.2 改善的Gardner算法结构

从上节能够看出,传统Gardner算法无法满意较宽速率规模基带信号的位同步要求。为完结该要求,本规划在FPGA 渠道的根底上,对算法完结结构进行了改善,改善结构如图2所示。

图2中,内插滤波器选用Farrow结构的FIR 滤波器完结,滤波器系数实时核算;守时差错检测选用独立于载波且采样点较少的GA-TED 算法;环路滤波器、内部操控器可由外部操控器设置参数,基带码元速率改动时,相应参数能够随之改动。因此,本规划能够满意位同步器的通用性要求。

该同步器作业进程如下:外部操控器依据基带码元速率设置相应参数,通过外部操控器接口将操控、地址和数据信号别离送往分频器、环路滤波器和内部操控器。时钟电路别离供给采样时钟和FPGA 时钟,FPGA作业时钟在片内通过分频器发生所需频率的时钟,供FPGA 各模块运用。输入接连时间信号x(t) 经由独立时钟操控的ADC 进行采样,转换为8 位数字信号送至FPGA 内,符号化后变为有符号数字序列,送入内插滤波器模块。内插滤波器依据输入信号的采样值和内部操控器给出的参数μk,在每个插值时间kTI 核算出最佳断定点的内插值y(kTI)。守时差错检测核算出差错μτ (n),输出至环路滤波器。环路滤波器依据当时的参数设定,滤除噪声并将差错信息送给内部操控器。内部操控器以NCO为中心,依据处理后的差错信息和设定的频率字参数调整插值时间kTi,使之尽可能挨近最佳判守时间,并输出位同步脉冲BS,一同核算出差错距离μk 送给内插滤波器,进行内插值核算,终究完结守时信息的康复。

2 FPGA规划

2.1 全体结构规划

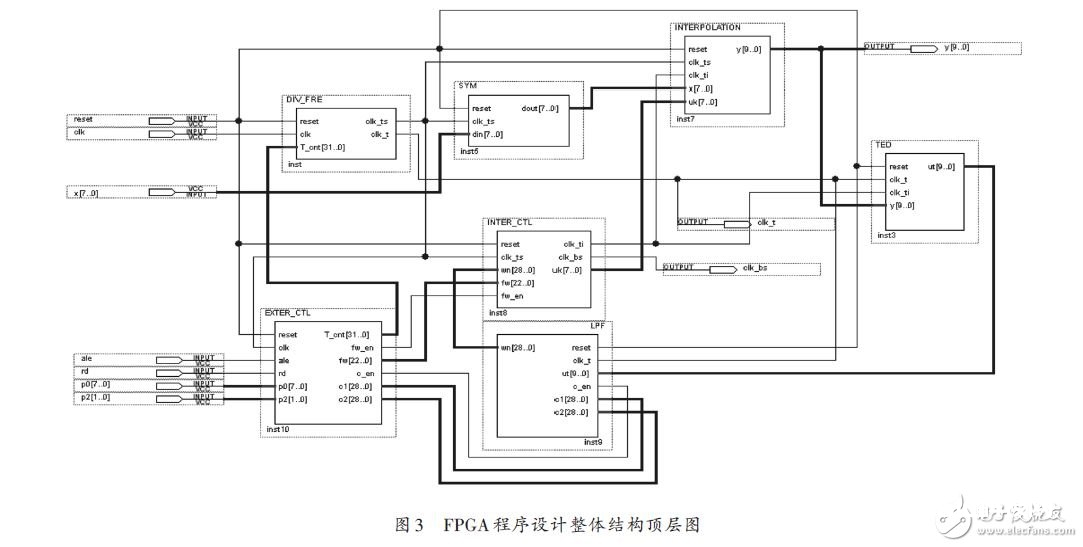

依据图2的算法结构,FPGA规划选用模块化方法,全体结构的顶层图如图3所示。

从图3能够看到,该规划包括分频器(DIV_FRE)、符号化(SYM)、内插滤波器(INTERPOLATION)、守时差错检测(TED)、环路滤波器(LPF)、内部操控器(INTER_CTL)和外部操控器接口的时序电路(EXTER_CTL)共7个模块。其间,分频器由片外晶振供给时钟输入,分频后为片内其他模块供给相应时钟。其间码元时钟的分频系数可由外部操控器通过接口进行设置。符号化是将A/D采样发生的无符号数转换为有符号数,以便后续模块进行带符号的运算。

外部操控器接口的时序电路将外部操控器送来的操控信号(ALE和RD)、地址信号(P2.0、P2.1)和数据信号(P0口)、转换为FPGA 内分频器、环路滤波器和NCO的使能信号和参数,完结对位同步器各参数的设置。

分频器、符号化和外部操控器接口模块完结较为简略,不再赘述。而内插滤波器、守时差错检测、环路滤波器和内部操控器的完结较为杂乱,且本规划通过选用相应算法和改善结构,完结了位同步器的通用性。本文将具体论述这些模块的规划。

2.2 模块具体规划

2.2.1 内插滤波器规划

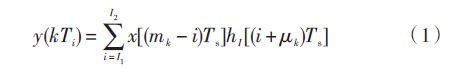

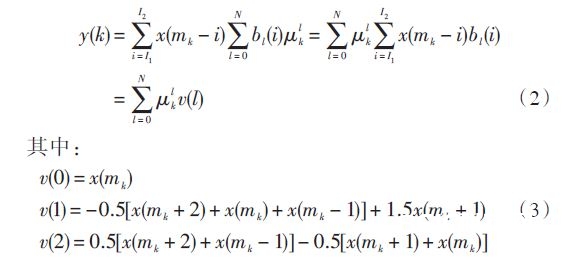

内插滤波器是完结算法的中心,它依据内插参数实时核算最佳断定点的内插值,即:

式中:mk 为内插滤波器基点索引,决议输入序列中哪些采样点参加运算,它由插值时间kTi 确认;μk 为差错距离,决议了内插滤波器的冲激响应系数[1].kTi 和μk 的信息由内部操控器反应回来。

本规划的内插滤波器选用依据4 点分段抛物线多项式的Farrow结构完结。将式(1)改换为拉格朗日多项式,即令:

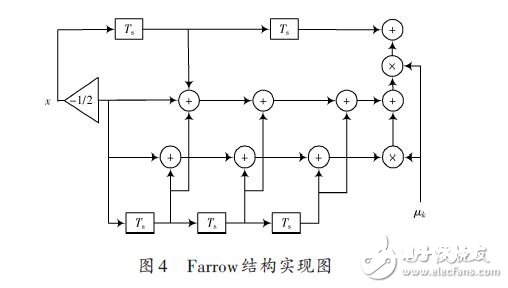

依据式(2)和(3),内插滤波器程序完结结构如图4所示。

从图4能够看到,该结构由1个移位器、5个触发器、 8个相加器、2个乘法器组成,比直接型FIR节约10个乘法器、4个相加器的资源。其间,除以2的运算选用数据移位完结,防止运用除法器。输入的8位数据 x,核算后得到10位的内插值y 输出。因为内部一切寄存器经核算后,均选用最小位数,有用地削减了Logic Elements资源的占用。

2.2.2 守时差错检测规划

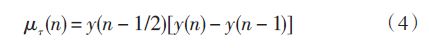

守时差错检测程序选用独立于载波相位差错的GA-TED算法。该算法每个符号周期只需求两个插值,每个码元周期输出一个差错信号μτ (n) ,即:

其间,y(n) 标明第n 个码元选通时间的内插值,前后两个内插值的插值代表差错方向;y(n – 1 2) 标明第 n 个和第n – 1 个码元的中心时间内插值,代表差错巨细。

FPGA完结时,为防止乘法运算,选用y(n) 和y(n – 1)的符号来替代实践值[8],即选用式(5)核算差错信息:

依据式(5)进行程序规划,差错的正负方向判别选用case 句子,当y(n) 和y(n – 1) 的符号位别离为“0”和“1”时,y(n – 1 2)的符号位不变;当符号位别离为“1”和“0”时,y(n – 1 2) 的符号位取反;当符号位为“0”“0”或“1”“1”时,令输出的μτ (n) = 0.TED程序在1 Ti 的时钟操控下进行运算,终究得到29位差错数据,并以1 T 的速率即码元速率输出至环路滤波器电路。

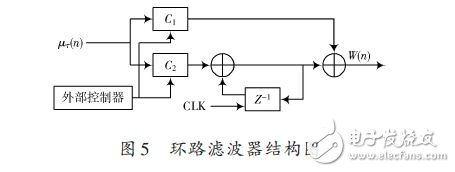

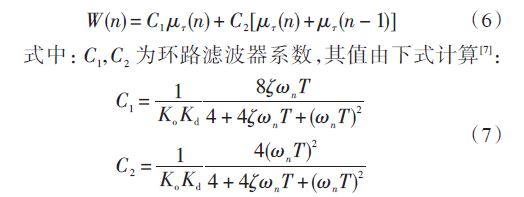

2.2.3 环路滤波器规划

本文对Gardner算法中的环路滤波器进行了改善,依据通用位同步器的要求,选用二阶数字滤波器,而且敞开滤波器参数(C1,C2 ) 和使能(c_en)端口,当码元速率改动时,通过外部操控器来改动参数,完结滤波器的通用性。滤波器结构如图5所示。

从图5能够看到,滤波器的输出为:

式中:Ko Kd 为环路增益;ζ 为阻尼系数,取ζ =0.707;T 为采样时间距离,即相位调整距离;ωn 为无阻尼振荡频率。

为削减资源占用,环路滤波器中的乘法运算均选用移位方法完结,处理后的差错信息送给内部操控器。

2.2.4 内部操控器规划

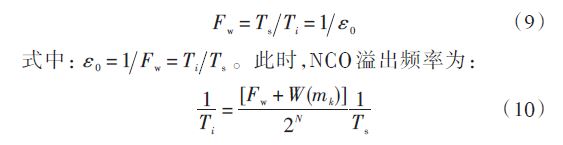

内部操控器依据守时差错信息,调整插值频率1 Ti和差错距离μk ,并输出位同步脉冲BS,它包括NCO(Numerically Controlled Oscillator)和差错距离核算两部分。该程序供给接口(频率字fw 和使能端fw_en),外部操控器能够通过该接口输入参数。

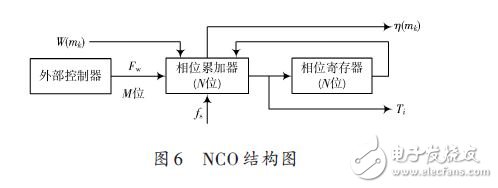

本规划中NCO 选用与文献[10]相似的DDS(DirectDigital Synthesis)结构,其频率操控字Fw 可由外部操控器设置,其结构如图6所示。

图6中,M 为频率操控字位数,N 为相位累加器和相位寄存器的位数。这儿取M = N = 23,选用递减型的NCO,归一化后相位累加器的累加值为:

式中:Fw 为频率操控字;W (mk ) 为环路滤波器输出的差错信号,二者由环路滤波器供给,决议了NCO的溢出周期。其间,当:

NCO 溢出信号即为提取出的位同步信号的2 倍频(2BS),经2分频后能够得到位同步脉冲(BS)输出,2BS一同作为内插滤波器和差错距离核算的使能信号。

差错距离μk 在NCO 溢出后的下一个Ts 时间进行核算,环路锁守时:

将其切断为8位数据送给内插滤波器。

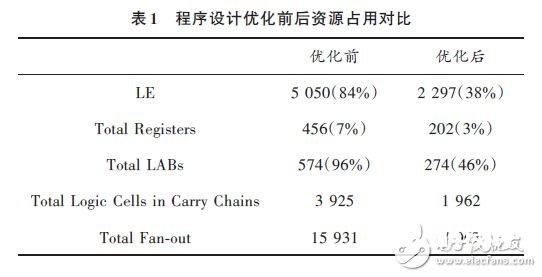

本规划一同对代码进行了优化,数据有用位的截取、内插滤波器的结构优化、乘法选用移位核算替代等办法,有用地节约了硬件资源,优化前和优化后的资源占用状况比照见表1.

3 仿真和剖析

3.1 Matlab仿真

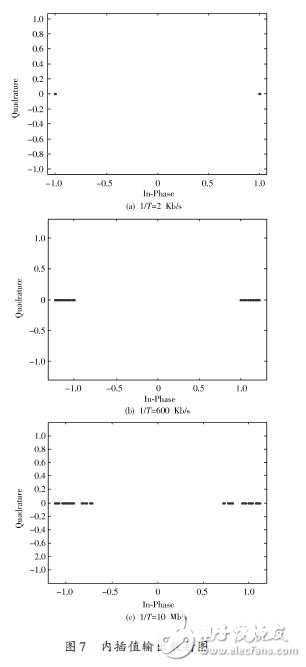

本文选用Matlab对算法进行理论仿真,输入采样值x(m) 为[-1,1]之间的随机码,采样频率上限为20 MHz,令码元速率别离为2 Kb/s,600 Kb/s,10 Mb/s,环路滤波器、内部操控器参数随码元速率改动。取内插滤波器的插值输出y(kTi) 做散射图剖析,验证对不同速率的基带信号,内插值是否挨近最佳断定值,如图7所示。

从图7能够看出,在基带速率和采样率满意奈奎斯特定理的条件下,该仿真输出的内插值均会集在抱负值 -1和1周围,虽然有必定的含糊,且频率越高,含糊程度越大,但码元断定阈值在0值点,所以断定值无需严厉为±1,该图标明关于较宽速率规模内的基带信号,输出的插值均能够较好地用于码元断定,即算法正确。

3.2 FPGA仿真

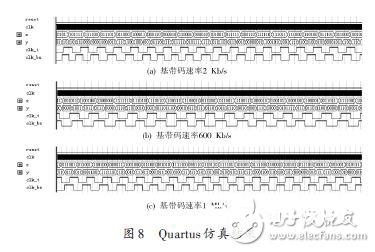

在Quartus下对本规划进行仿真。基带信号选用M 序列,由FPGA生成,令基带码速率别离为2 Kb/s,600 Kb/s,1 Mb/s,一同分频器、NCO 及环路滤波器参数也做相应设置,仿真成果如图8所示。

在图8中,x为基带码元序列,y为内插值输出,clk_t为基带码元时钟,clk_bs为提取出的位同步信号。从图中能够看到,clk_bs通过守时环路调整,其上升沿逐步向clk_t的下降沿(即最佳断定点)接近,且跟着基带码元速率的改动,clk_bs也会随之改动,但其间心频率与clk_t相同,相位与最佳断定点相差不超越半个码元周期,能够进行码元断定,这标明本规划对2 Kb/s~1 Mb/s内的基带信号,均可完结位同步。

4 结语

本文提出了一种依据FPGA的通用位同步器的规划计划。该规划计划中的同步器在传统Gardner 算法的根底上进行了改善,其间,内插滤波器选用Farrow结构,守时差错检测选用GA-TED算法,环路滤波器和内部操控器参数可由外部操控器设置,因此完结了较宽速率规模内基带码元的位同步。仿真成果标明,该计划占用FPGA资源较少,而且在实践运用中具有牢靠有用性。