在针对大批量运用开发体系时,要考虑的一个重要因素是本钱。有多个方面会影响整体具有本钱,而不只仅是每个元器材的价格。这包含硅片的功耗要求、资料(BOM)总本钱、规划和测验体系的工程师的效能等。挑选FPGA供货商很重要,要考虑影响体系本钱的方方面面,这体现在整个产品规划周期中。

下降本钱和功耗,进步效能,让产品更快地运转,这些均是规划工程师现在有必要面临的扎手问题,因而,FPGA的挑选很重要。Altera Cyclone V FPGA经过多种办法协助规划人员下降体系总本钱,规划人员获益的不只是TSMC的28nm低功耗(28LP)制作工艺,还包含Cyclone V器材系列内置的体系结构,以及Altera规划东西辅佐体系所供给的强壮的高效能东西。选用Cyclone V FPGA,不只能完成业界最低的整体具有本钱,还可取得类型最全的低本钱器材——从25K逻辑单元(LE)到301K LE,以及不到100K LE的仅有28nm解决方案。

Cyclone V FPGA系列有六种方针类型:仅含逻辑的(E)类型、根据3G收发器的(GX)类型、根据5G收发器的(GT)类型,以及这些类型的SoC衍生产品(分别是SE、SX和ST),每一类型都含有集成双核ARM Cortex-A9 MPCore运用级处理器。每一器材类型集成了丰厚的硬核知识产权(IP)模块。与前几代体系结构比较,所选用的先进技能包含,自习惯逻辑模块(ALM)、精度可调数字信号处理(DSP)模块、分段式锁相环(fPLL)、硬核存储器操控器等。

28LP制作工艺下降规划本钱

Altera在28nm选用了左右开弓的制作战略,关于需求尽可能进步带宽的体系,运用TSMC的28nm高功用(28HP)工艺,关于低本钱和低功耗运用,则选用28LP工艺。Stratix V FPGA选用了28HP工艺,而Arria V和Cyclone V FPGA都选用了LP工艺。关于任何电子体系,下降功耗当然也就意味着下降了运营本钱以及整体具有本钱。

Cyclone V FPGA中运用的本钱最优28LP工艺定制满意了低本钱和低功耗运用需求。经过选用各种技能,包含运用比28HP工艺更长的栅极沟道等,一同下降了走漏电流和动态电流。经过运用比28HP工艺更传统的金属工艺以及线键合封装技能,进一步下降了本钱。与倒装焊封装比较,线键合封装运用户在每一类型上节约了大约5美元。Altera的收发器规划特长反映在高速串行接口的高牢靠性和低功耗上。在前期功耗预算基准测验中,与Cyclone IV FPGA比较,Cyclone V FPGA展示出显着的低功耗优势(图1)。

图1 与前几代技能比较,Cyclone V FPGA大致下降的功耗

低本钱28nm产品进步规划灵活性

从体系规划的视点看,某一FPGA系列供给多种器材密度挑选有很大优势。Cyclone V FPGA的系列类型容量从25K LE到301K LE,在低本钱28nm器材市场上具有显着的优势。规划人员能够在较小的类型上进行规划,假如产品规划拓宽了,今后则能够移植。相同的,假如规划规划变小了,他们还能够运用更小的器材。一般来说,假如在规划周期的中心阶段转换器材系列来处理这类工程更改(ECO),其时刻和资源本钱都十分高。Cyclone V系列有丰厚的纵向移植挑选,Altera供给了最全面、性价比最高的低本钱FPGA器材(如图2)。

图2 Cyclone V FPGA和Spartan-6以及Artix-7 FPGA的纵向移植途径比照

Cyclone V FPGA体系结构下降了规划本钱

Altera的28nm体系结构经过多种办法下降了规划本钱。中心架构进步了逻辑功率,是现在密度最高的互联结构。硬核IP完成了高功用,进步了灵活性,并且缩短了规划时刻。经过优化后的收发器具有同类最佳的信号完整性,削减了调试时刻。仅运用两种电压轨,因而,电源分配网络本钱更低,更简略规划。选用fPLL,支撑组成恣意频率的时钟,不需求贵重的振荡器,智能引脚布局进步了器材的可布线才能,增强了信号完整性。

内核架构和布线进步了逻辑功率

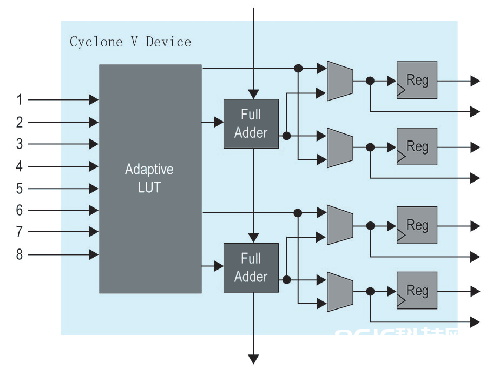

Cyclone V FPGA选用了立异的内核架构来高效完成逻辑和DSP功用。据预算,与前几代技能比较,由于进步了逻辑运用率,仅增强内核就能够使规划人员在每一类型上节约20美元。Cyclone V体系结构的根本构建模块是ALM。它包含一个8输入分段式查找表(LUT)以及两个加法器和四个寄存器——都严密封装在一同(图3),进步了功用,能够很好的运用硅片面积。这一体系结构与Altera的高端器材相相似,是Cyclone IV FPGA的承继开展,其根本构建模块是LE,具有4输入LUT以及一个寄存器。ALM结合严密封装,不只进步了硅片的性价比,并且更简略完成时序收敛,特别是需求许多寄存器和流水线的规划。Cyclone V系列供给等价的301K-LE,以笔直接近逻辑阵列模块(LAB)的方式摆放,每一LAB有10个ALM。由适配器主动装备ALM (由Altera的Quartus II开发软件供给),完成运用所需求的纯组合或许算术功用。

图3 Cyclone V FPGA自习惯逻辑模块

Cyclone V FPGA具有新的嵌入式存储器模块,即M10K。这一存储器模块体积小于竞赛体系结构中的嵌入式存储器模块,然后进步了粒度,单位硅片面积供给更多的存储器端口,很少糟蹋模块。片内存储器体系结构十分适宜需求许多DSP的运用,例如电机操控、演播设备和3D电视等。为能够高效的低本钱处理宽浅缓冲和延时单元,Cyclone V器材还供给了更小的640位MLAB模块。

Cyclone V FPGA还选用了高功用精度可调DSP模块。运用Altera立异的DSP模块以及有限冲击呼应(FIR)滤波器专用系数块和反应通路,规划人员能够独立装备每一乘法器的精度,从9×9到27×27位,详细取决于运用需求。经过这一功用,Cyclone V FPGA完成了规划人员在运用时所要求的精度适宜的乘法器,支撑规划人员尽可能选用最高效的硬件。例如,一个简略视频处理运用只需求9位精度,而一些高端五颜六色体系则需求24位。关于9位视频运用,一个模块能够分红三个9位乘法器,将DSP模块的功率进步了三倍。一个精度可调模块能够高效的满意一切这些规划要求。然后支撑规划人员让FPGA资源来习惯其算法,而不是让算法来习惯有限的资源要求。

硬核IP完成高功用

Altera在固定硅片中增强了某些常用的IP模块(例如双倍数据速率存储器操控器、协议仓库,乃至是嵌入式ARM处理器),开释名贵的可编程逻辑资源,用于完成其他逻辑功用,然后进步了功用,下降了功耗和本钱。作为一个比如,PCI Express(PCIe)协议仓库需求大约150K LE作为软核完成,在硬核模块中则只需求三分之一的器材面积。选用竞赛技能和东西测验完成PCIe内核的用户会发现,运用Altera硬核IP结合Qsys体系集成东西,在规划和调试时刻上均匀能够节约6个星期的时刻。

Altera还在FPGA中引入了第一种PCIe多功用支撑。这一技能简化了不同外设之间对PCIe链路带宽的同享。支撑8种功用,PCIe多功用支撑将多个单一功用端点集成到一个多功用端点中,能够节约20K LE。运用PCIe多功用,规划人员能够很好的定制业界规范处理器和驻留在FPGA逻辑中特有的多种外设。并且,支撑多功用后,规划人员能够运用规范操作体系(OS)驱动软件,在FPGA的外设上同享PCIe链路带宽。没有多功用支撑时,开发进程中的一项首要作业是定制驱动软件以完成这种资源同享功用。并且,多功用支撑不需求多个软核或许硬核PCIe内核,将其集成到了一个多功用PCIe端点中,然后有用下降本钱。

硬核IP最早呈现在Altera的40nm器材中,作为PHY层单元,不再需求外部高功用串行I/O电路板元器材。在Altera 28nm器材中,嵌入式硬核IP模块完成了ASIC的本钱、功用和功耗特性,不会献身规划灵活性。例如,能够在Cyclone V GT器材中装备PCIe硬核IP模块来支撑PCIe Gen1或许Gen2。此外,Cyclone V FPGA还供给两个硬核PCIe内核——是竞赛器材的两倍。与软核逻辑完成比较更强的优势是,硬核IP模块功耗下降了65%,而功用进步了50%,表1列出了Cyclone V FPGA中的硬核IP功用,以及经过硬核完成所节约的资源量。

表1 Cyclone V FPGA中的硬核IP功用

硬核IP模块

每个模块节约的FPGA资源

32位DDR3/DDR2存储器操控器,带有ECC、指令或许数据

>40K LE和45 M10K模块

PCIe Gen1和Gen2

>10K LE

PCIe 多功用

>20K LE

ARM Cortex-A9 MP Core处理器和外设

>40K LE

老练牢靠的收发器针对各种数据速率进行优化

Altera的28nm系列产品引入了模块化收发器,支撑规划人员满意实践运用的器材功用需求。在Altera一切28nms FPGA系列中,这种收发器运用了相同的根本体系结构,最大作业速率从3.125Gbps直至28Gbps。正如Stratix V和Arria V器材相同,Cyclone V收发器能够在几种不同的速率设置之间动态切换,能够降速来下降功耗。这种挑选功用为下降体系均匀功耗供给了一种办法,在空闲时,收发器作业在最小速率,根据需求切换到高速作业。

假如I/O扩展等运用只需求5Gbps或许速率更低的收发器,不会呈现28Gbps作业时大型晶体管那样的功耗和本钱。相反,收发器以最低功耗和最低本钱完成了3.125Gbps和5Gbps功用,Cyclone V FPGA系列能够很好的习惯规划。与Stratix V和Arria V器材中的收发器相似,Cyclone V FPGA收发器支撑多种协议,包含3G SDI、千兆以太网(GbE)、CPRI、Display Port、PCIe、SATA和Serial RapidIO等。Altera收发器信号完整性以及经过收发器东西包完成的实时调试功用,能够节约数星期的电路板开发和调试时刻。

选用两种电压轨简化电源分配

在一切低本钱FPGA中,Cyclone V FPGA需求的电压轨数量最少。它们有内置片内电压稳压器,因而,只需求运用两种电压轨来一同支撑逻辑和收发器电源。这样,能够不需求板上电压稳压器,防止布线拥塞,削减了电路板层数,然后简化了电路板规划。竞赛器材至少需求三种电压轨来支撑内核、I/O和收发器逻辑。额定的电源轨需求添加元件以及PCB面积,还可能会带来布线拥塞问题,在电路板开发预算中,本钱可能会添加10到30美元。

fPLL可组成恣意频率无需额定振荡器

Altera 28nm器材的通用锁相环是fPLL,它具有高档分段式频率组成以及M/N频率完成功用。在规范PLL中,M和N值都是整数。Altera选用了delta-sigma调制器,并在反应通路中运用了32位M和N值,支撑反应M分频器选用分段值。这支撑完成准确的频率组成功用。能够组成恣意时钟频率,fPLL能够代替电路板上的振荡器,然后下降了电路板本钱,减小了电路板面积。

智能引脚布局进步可布线才能

Cyclone V FPGA以最低的开发本钱供给优异的信号完整性。选用了惯例棋盘式电源和地形式,简化了布板。此外,器材左边是惯例的收发器布局,并进行重复,而接收器总是在外部,然后完成了最佳信号完整性。还尽量远离收发器放置存储器I/O引脚,相关于收发器进行屏蔽。Altera的办法是,首要经过防止引脚布局问题,削减在耗时的调试进程上的投入。

Altera体系规划东西下降整体具有本钱

Altera的集成规划环境,包含Quartus II软件,为FPGA业界供给了先进的东西集,它供给相似AS%&&&&&%的时序收敛东西(TimeQuest时序剖析器),其高效能特性包含:Qsys体系集成东西、体系操控器、收发器东西包,以及DSP Builder和SoC虚拟方针软件渠道。其间,Qsys是下一代SOPC Builder东西,用于协助规划人员构建并调整体系。Qsys支撑用户开发的以及商用IP模块的快速集成,加快了规划流程,进步了效能。并且,Qsys支撑分层规划,简化了大规划规划的办理。运用体系操控台这一东西,用户能够运用体系级会话功用,经过便利简略的软件运用编程接口(API),在指令行或许体系操控台图形用户界面(GUI)中,选用脚本,或许交互式运转,在更高的笼统级上实时调试FPGA。体系操控台十分适宜电路板开发等使命,使规划人员能够经过JTAG或许TCP/IP来运用和操控FPGA硬件。

选用具有高档模块库的DSP Builder进行DSP运用规划

运用DSP Builder,能够选用DSP规划东西MATLAB Simulink来规划FPGA,它让规划人员能够持续停留在自己了解的EDA环境中,运用易于了解的原理图输入东西进行规划,针对方针Altera FPGA主动生成可归纳RTL代码。乃至能够直接从MATLAB环境中,在Quartus II软件中编译规划,不需求预先学习Verilog或许VHDL便能够开发FPGA规划。

DSP Builder为Simulink供给两种首要插件,根本模块库和高档模块库,支撑拖动组件,把它们链接在一同,并进行仿真。两种模块库都支撑将可归纳组件放到Simulink原理图浏览器中。选用高档模块库,DSP Builder会主动对数据通路进行流水线处理,满意fMAX方针要求,尽可能从头运用模块。

SoC虚拟方针

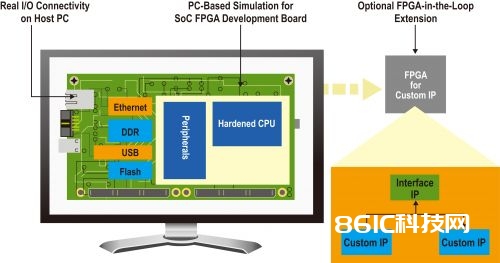

Altera SoC FPGA虚拟方针是对Cyclone V SoC FPGA中的双核ARM Cortex-A9 MPCore嵌入式处理器开发体系的快速功用仿真。这一全面的原型开发东西“开箱即用”,在PC上运转,发动Linux操作体系,对实践开发电路板进行建模。虚拟方针与其仿真的实践硬件二进制和寄存器兼容,支撑器材专用产品软件的开发,取得实践硬件后,不必修正就能够在硬件中运转。为能够全面的表明Altera SoC FPGA器材,虚拟方针还选用了根据PC的仿真FPGA扩展功用,名为环路FPGA。如图4所示,扩展环路FPGA支撑虚拟方针与Altera商用FPGA开发电路板的衔接,在这些电路板上,能够完成自己的定制IP,与虚拟方针其他组件一同运转。运用这一特性,能够选用定制外设和硬件加快器等FPGA硬件来测验软件。

图4 具有扩展可选环路FPGA的SoC虚拟方针软件开发渠道

集成实例——选用Cyclone V FPGA的轿车剖析

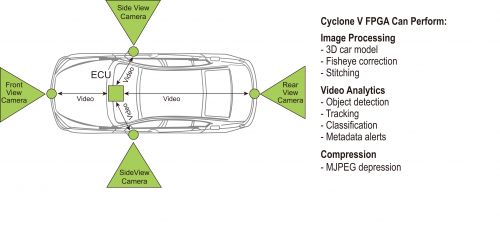

Cyclone V FPGA适用于许多运用,现在开展很快的一种运用是轿车剖析。Cyclone V FPGA的低本钱以及强壮的功用特性十分适宜这一运用领域。在进行串行视频数据处理时,需求进行许多的核算,需求许多存储器,这都能够运用硬核存储器操控器、高速串行收发器、fPLL以及丰厚的内部逻辑和存储器资源等硬件特性。

此外,用户运用Altera的视频和图画处理(VIP)包很简略在Qsys中开发杂乱视频处理体系。图5显现了轿车中的一个视频数据集成实例。在这一环境中能够高效的运用Cyclone V FPGA,这是由于它供给了高清晰功用和其他视频处理特性,例如,缩放和方针勘探,不光本钱低并且功耗也低。

图5 Cyclone V FPGA体系运用实例——轿车的视频剖析

定论

Cyclone V FPGA下降了整体具有本钱。TSMC的28LP工艺规划用于尽可能下降功耗,一同也是本钱最低的28nm制作工艺。低功耗意味着进步了用户价值链的体系牢靠性,延长了体系寿数,下降了运营总本钱。此外,Cyclone V FPGA还有许多体系结构优势,有利于下降体系本钱,这包含,硬核存储器操控器、高效的逻辑和布线资源、fPLL、精度可调DSP模块,以及最少的电压轨需求等。并且,Quartus II软件带有Qsys和体系操控台功用、DSP Builder和SoC虚拟方针渠道,支撑高效便利的规划Cyclone V FPGA。关于FPGA规划人员,Altera硅片和规划东西协同作业,完成了最低的整体具有本钱。