运用FPGA完成大型规划时,或许需求FPGA具有以多个时钟运转的多重数据通路,这种多时钟FPGA规划有必要特别当心,需求留意最大时钟速率、颤动、最大时钟数、异步时钟设计和时钟/数据联系。规划进程中最重要的一步是确认要用多少个不同的时钟,以及怎么进行布线,本文将对这些规划战略深化论述。

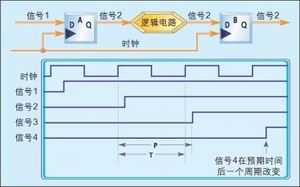

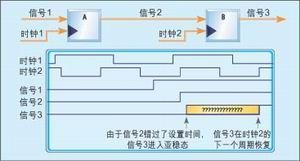

FPGA规划的第一步是决议需求什么样的时钟速率,规划中最快的时钟将确认FPGA有必要能处理的时钟速率。最快时钟速率由规划中两个触发器之间一个信号的传输时刻P来决议,假如P大于时钟周期T,则当信号在一个触发器上改动后,鄙人一个逻辑级大将不会改动,直到两个时钟周期今后才改动,如图1所示。

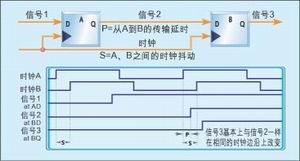

传输时刻为信号在第一个触发器输出处所需的坚持时刻加上两级之间的任何组合逻辑的推迟,再加两级之间的布线推迟以及信号进入第二级触发器的设置时刻。不管时钟速率为多少,每一个FPGA规划所用的时钟有必要具有低颤动特性。颤动S是触发器的一个时钟输入到另一个触发器的时钟输入之间的最大推迟。为使电路正常作业,颤动有必要小于两个触发器之间的传输时刻。

图2显现了假如颤动大于传输时刻(S>P)将呈现的状况,该电路用时钟的两个上升沿来推迟信号1。可是,信号1上的一个改动会在相同的时钟周期上传输到的信号3上,然后引起信号2的改动。因为S>P,电路将不能不正常。

须留意的是,时钟速率与传输延时并没有什么联系,乃至一般的100bps时钟也会呈现颤动问题。这意味着尽管FPGA供货商声称他们的芯片具有较短的传输时刻和很高的时钟速率,但颤动问题或许会严峻,乃至那些没有运转在最高速率上的规划也是如此。

好在FPGA供货商现已认识到时钟颤动的影响,并在他们的芯片中供给低颤动的布线资源。这些特别的布线可以在芯片中一个给定范围内的任何两个触发器之间供给一个确认的最大颤动。部分产品的低颤动资源覆盖了整个芯片,而其它的则或许只覆盖了FPGA逻辑块中的一个特定的行或列。关于一个需求许多不一起钟源的规划,这些低颤动FPGA是比较抱负的挑选。

多时钟规划的最严峻问题之一是用异步时钟将两级逻辑结合在一起。因为异步时钟会发生亚稳态,然后严峻下降规划功用,或彻底损坏规划所能完成的功用。在触发器的时序要求发生抵触时(设置时刻和坚持时刻)将发生亚稳态,触发器的终究输出是不知道的,并使整个规划处于不确认状况。假如有一级逻辑要将数据异步地发送到另一级,图3所示的景象将不能满意触发器的设置和坚持时刻要求。切当地说,假如规划中含有异步逻辑将有或许会发生亚稳态。在处置异步资源时必需十分当心,因为这或许发生一些很严峻的问题。

多时钟规划

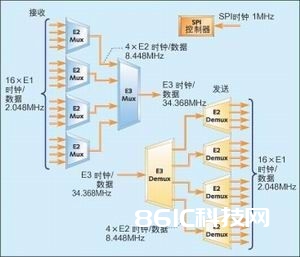

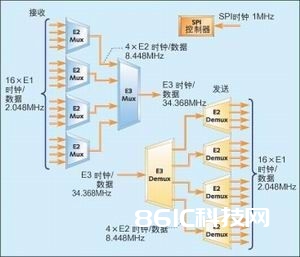

本文以电信运用中的E3多路复用/解复用规划为例。如图4所示,多路复用器接纳来自一组独立线路接口芯片的16个独立E1信道,每一个信道都作业于2.048MHz;经复用后,这些E1流组合成4个E2流,别离作业在8.0448MHz;4个E2流终究组合成一个E3流,以34.368Mbps的速率串行发送出去。在接纳端履行相反的操作:解复用器从E3流提取4个E2数据流,然后从E2流提取16个E1流,终究将E1流发送到接纳端的线路接口芯片。

这些E1线路接口在发送和接纳时都独立作业,因而2.048MHz的时钟速率可以有+/- 20ppm的误差。相同,因为大多数体系一起发送和接纳数据,分立的多路复用器和多路解复用器将供给2个独立的E3流(发送和接纳)。因而,两个34.368MHz的时钟可以存在纤细的差异。

因为E2流是在芯片上发生的,这些E2多路复用器可以同享同一个8.448MHz时钟。可是,因为接纳的数据速率与咱们所规划的板无关(且不能假定一切E2多路复用器运用相一起钟),所以E2解复用器时钟有必要能作业在略为不同的速率下。

此外,假定规划中需求一个由作业频率为1MHz的处理器操控的独立SPI(串行外围接口)总线接口,该接口用于状况和操控。这样一来,规划中一共用了32个2.048MHz时钟,5个8.448MHz时钟,2个34.368MHz时钟和一个1MHz时钟,一共多达40个时钟。

本规划中最快时钟是34.368MHz E3时钟。FPGA的最大时钟速率的确认很重要,因为规划的差异将影响到该最大值。可是,在芯片商的材料手册中常常可以看到“大局时钟设置及坚持时刻”和“至CLB输出的时钟”两个参数,将这两个参数的最大值相加,再添加25%就能可以得到最小时钟周期的初略值,在最大时钟速率条件下答应10%的余量,以确保过热条件下能正常作业。因而,咱们设置的最小速率为40MHz,许多较新的FPGA都可以很简略地支撑该频率。事实上,FPGA供货商现已推出了超越300MHz的器材。

在确认了能满意最大频率要求的FPGA后,就需求确保有满意的空间来完成你的规划。假如所选的FPGA没有满意的余量,就不能供给满意的布线资源来满意规划的时序束缚。一般芯片供货商声称的速率是最佳条件下的速率,FPGA供货商一般主张FPGA逻辑在布线功用开端显着变差曾经可以用到80%。在挑选FPGA器材时,主张在新的规划时最好使FPGA逻辑用到50%左右,这样就答应核算开始规划巨细呈现超差,以及为在规划起动后发生不可避免的规划变更留出空间。假如终究的规划只占用低于50%的资源,则可以运用同一系列中较小的FPGA以下降成本。

经过时序束缚来规则慢时钟速率,然后可以改善规划中最快时钟的布线。在多路复用器比如中,假如设置FPGA布线东西SPI总线时钟为1MHz,而E3时钟为40MHz,布线东西将尽量使E3时钟的逻辑电路模块相邻布局。假如因为空间的约束而不能将悉数电路布局在一起,则首要应将SPI逻辑别的布局,因为SPI逻辑可以处理更长传输推迟。一切FPGA供货商的布线东西都能规则这些较慢时钟速率。

削减时钟数量

依据市场调查,现在还没有哪个FPGA器材可以支撑这种多路复用器/解复用器规划所需的40个时钟。所以,咱们有必要削减所需求的时钟数。

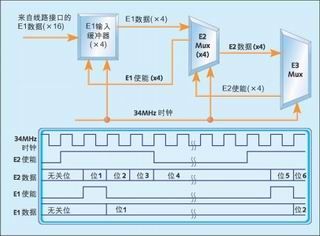

首要了解E2和E3多路复用器的时钟。前面现已剖析了4个E2多路复用器作业在相一起钟下的可接受度,E3多路复用器运转于比E2时钟高得多的速率,必需运用一个不同的时钟。可是,假如咱们从E3时钟中引出E2时钟是否可行呢?因为E3多路复用器要从每个E2支路得到数据,咱们可以在需求E2多路复用器给咱们数据时,简略地将脉冲送给每个多路复用器。咱们没有去掉任何时钟,但E2时钟现在是根据E3时钟。

假如在一切的多路复用器中也运用相同的时钟,而且只运用一个使能信号来告知E2多路复用器什么时候作业,这时会发生什么问题呢?假如E3多路复用器用34.368MHz时钟发生使能信号,在这些使能信号上的颤动不会比用在FPGA中任何其它同步逻辑更大。所以,使能信号可以运用正常(高颤动)布线资源,这样就不需求独自的8.448MHz多路复用器时钟,读取E1数据缓冲器的数据时也是相同。换言之,假如E2多路复用器需求数据,它可以激活到特定缓冲器的使能信号。到缓冲器的时钟自身可以坚持E3多路复用器所用的34.368MHz时钟,如图5所示。

终究,咱们查看16个从线路接口芯片输入到FPGA的E1时钟。这些时钟有会发生下面几个问题:首要,16个时钟将占用太多可用芯片时钟布线资源;其次,在同一个FPGA中运用16个异步时钟来驱动彼此附近的触发器,因为地弹、串扰和其它效应将发生噪声问题。例如,因为噪声的原因,一个正边缘触发器会鄙人降边缘时改动输出状况,此类问题将难以处理。