在散射计数字处理体系中,需求多通道ADC电路来对数据进行采样。在该体系中,需求对ADC收集后的数据进行数字下变频、脉冲紧缩和波束组成等处理。可是,由于采样电路的路数许多,各个ADC通道由于布线差异、时钟差错等环境要素的影响,导致了ADC通道之间呈现共同性问题,特别是当存在多片ADC芯片并行作业时,会呈现两种不同的通道差异:一种是同一片ADC的两路收集电路之间的差异,另一种是不同片ADC收集电路之间的差异。这种差异会增大后期信号处理的差错,下降整个体系的精度。因而采样通道共同性是一个非常重要的问题。

本文提出一种高精度多通道ADC通路之间的共同性丈量办法,丈量各个采样电路的共同性,以便后期进行批改。

1 通道共同性丈量原理

本文的布景是散射计,在评价前端采样电路全体功能的时分,咱们的方针是将全体差错限定在必定的规模内。由于工程中的多路通道选用的是同一类型的ADC芯片,所以在测验之前,假定各个ADC芯片的转化功率、接口、供电电源、功耗以及输入规模没有差异,满意体系要求。那么各个通路之间的采样差异与几项要害的标准有关。其间比较重要且对后级数据处理有较大影响的方针是:各通路起伏增益共同性、直流偏置共同性和推迟共同性。

因而把这三项共同性方针的调查作为本文的中心。

1.1 直流偏置

测验从ADC的直流特性下手,由于ADC的沟通参数测验存在多种非标准办法,依据直流特性更简单对两片ADC集成芯片进行比较。直流特性一般比沟通特性更能反映器材问题。所以本文对共同性调查的第一项便是直流偏置的共同性。

本文对直流偏置共同性的调查是对采样得到的双通道数据进行归一化处理后别离对两个通道的信号求均值,设y1是采样通道1后经过归一化处理的成果,y2是采样后通道2经过归一化处理的成果。即可得到直流偏置共同性:

△DC=mean(y2)-mean(y1) (1)

1.2 起伏增益

起伏增益是ADC芯片的重要方针,增益差错会导致下降动态规模。假如在多通道ADC采样电路中,各个通道的起伏增益有比较大的不一起,对后级处理将会形成很差的影响。举例来说,两路相同的模拟信号经过不同ADC收集通道后,假如起伏增益的共同性欠好,那么不管对后级的相关处理仍是波束组成处理都会形成更大的差错。因而比较精确的

丈量两路采样电路的起伏增益是本文的一个课题。

当采样率较低和存在噪声的影响时,无法从时域提取比较高精度的正弦信号的起伏。由于经过采样后的信号是离散的,无法确保能够采到输入信号的最大值,因而无法从时域提取精确的起伏信息。依据帕斯瓦尔定理,信号的时域能量和频域能量是相同的,因而选用FFT剖析办法,将信号转化到频域,从频域提取起伏信息。

设两路信号从频域获得的起伏值别离为A1和A2,则起伏共同性如公式(2)所示为:

由于FFT成果是离散化的频谱,所以为了能到精确的起伏信息,需求确保频谱采样的正确性,即需求防止频谱走漏,这要求信号的剖析长度为整周期。一起并且两个通道的剖析长度要相同,以确保FFT的增益相同。

1.3 推迟估量

关于ADC采样电路而言,推迟共同性会影响相关处理成果。特别是在运用欠采样技能的时分,电路所发生的推迟更简单对后级形成影响。因而本文对多路ADC采样通道推迟的共同性做了要点调查和测验。

本文对剖析通道推迟选用了两种办法,即FFT法和相关法。这两种办法本质上是相同的,仅仅相关剖析法为了进步剖析精度,需求完结的时移和相关运算较多,速度较慢。

1.3.1 FFT法

FFT法有剖析速度快的特色,由于采样后的信号经过FFT后,能够很直观的看出被采信号的频域特性。比较于相关法,FFT法更快速,更直观。

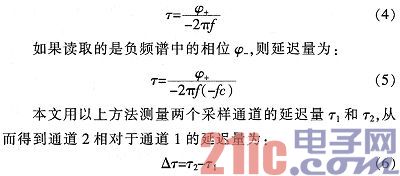

在FFT法中,本文先运用时域推迟和频域相位的对应联系,即:

x(t-τ)←→X(j2πf)exp(-2πfτ) (3)

把被采信号转到频域剖析。然后依据被采信号的频谱,找出频谱中能够读取最大值点的相位。假如读取的是正频谱相位φ+,则能够得到推迟量为:

1.3.2 相关法

两个信号相关是两个信号之间时移t的函数。关于自相关处理,当t=0时,两者最类似(重合),相关值最大,跟着t的增大,相关值减小。在通讯、信号处理、方针辨认和生物医学中经常用相关函数来衡量两个信号的类似程度。

进行相关处理的两个信号为同一个信号时是自相关。自相关是一个信号与其推迟后信号之间类似性的衡量,推迟时间为零时,则自相关成果便是信号的均方值,此刻自相关的值是最大的。并且白噪声的自相关成果为零,所以相关法能够很好的去除噪声对测验成果的影响。

由于本文测验的被采信号是由公分器分出来的两路信号,在抱负的状态下这两路信号本质上是同一路,由此可得假如不存在两路的推迟不共同,则这两路通道的信号进行相关操作得到的值应该是最大的。可是由于差错的存在,两路信号必定会有推迟的不共同。

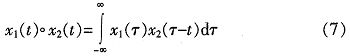

本文依据这一原理,将采到公分器上的两路信号和依据公式(7)进行相关

如公式(7)所示,在(-T/2,T/2)的一个周期内对通道1信号进行时延,对时拖延的信号与通道2信号的相关成果进行检测,当相关成果获得最大时的时延值即为通道2相关于通道1的推迟量τ’。

在对通道1信号进行推迟时,运用时域推迟和频域相位的对应联系所示的性质,在频率乘以线性相位,由于原始采样率较低,要得到较高的剖析精度,需求用较高的采样率来核算推迟步进值,即对通道1信号进行非正周期采样点的时移。

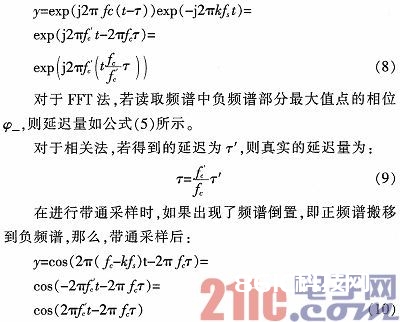

上述剖析和核算办法的鸿沟条件是低通采样,即信号频率为满意奈奎斯特采样定理。可是本次测验有必要满意选用数字中频接收机体系的布景,因而本文还测验了ADC在带通采样情况下的推迟特性。

设鸿沟条件为带通采样,原始中心频率为fc,采样率为fs,带通采样后的中心频率为,则带通采样后的信号为f’c:

即相位取反,这会导致推迟的符号取反,即本来超前的通体现出了滞后的现象,因而在这种情况下本文对核算成果取反以得到实在的推迟量。

2 实测数据剖析

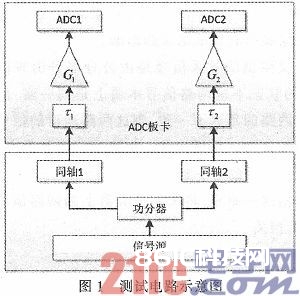

为了确保两个通道信号源的共同性,使刻苦分器将单路信号源的输出一分二作为两路ADC的输入,测验示意图如图1所示。

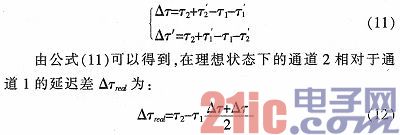

由于功分器以及同轴电缆的非抱负要素,会影响共同性测验成果,因而本文去除了测验条件的影响。以推迟为例,设两个ADC通道的推迟为τ1和τ2,而两根同轴的推迟为τ’1和τ’2,假定依照图1所示办法测得通道2相关于通道1的推迟差别离为△τ,然后交流两根同轴线,再测得通道2相关于通道1的推迟差为△τ’,则可得到以下联系:

经过上述剖析,在实测数据剖析阶段,本文运用了公式(12),以消除导线对推迟共同性测验的影响。

2.1 丈量过程

考虑到本次丈量的布景涉及到低通采样和带通采样。而测验中的采样频率为20 MHz。因而本文所取的被采样信号的频率厂的规模从1 MHz到81 MHz,以此来充沛测验在不同鸿沟条件下各路ADC采样电路的共同性。

本次测验中,一共有16路ADC采样电路,别离散布在8片类型为ADC9269的ADC芯片上。为了更为精确的丈量,本文丈量了这16路采样电路中同一片ADC芯片的两路和不同片ADC的两路中的7组数据以进行比较剖析。用以充沛比较其差异。

为了消除导线对后期数据剖析的影响,本文的测验选用的办法是采样完结一组数据后,将功分器的两路信号输出反过来再接入这两路,得到对应的一组数据,在后期处理中就能够消除导线对共同性测验的影响。

本次测验运用Xilinx公司ISE(Integrated Software Environment)软件的chipscope抓取数据,并把数据导入MATLAB中进行共同性的高精度剖析,得到了很多的共同性剖析成果数据。

2.2 共同性测验成果

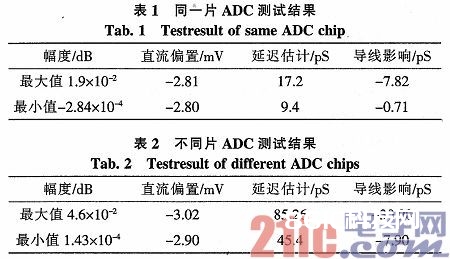

经过以上测验过程,并对得到的数据进行整合,得到表1和表2。它们反响了起伏共同性、推迟估量、导线对推迟的影响的最大值和最小值。

由表1和表2能够直观的看出,本文所调查的起伏共同性、直流偏置共同性、推迟共同性、导线对推迟的影响都达到了很高的精度。这是由于本文选用了合理的丈量办法。这关于采样后的数字信号处理有很大的协助。即使共同性测验成果体现很差,这种高精度的测验办法也对后期共同性的批改有很大的协助。

表1与表2也反映了同一片ADC的两路和不同片ADC的两路之间的差异。在同一片ADC的不同两路中共同性是很好的。不同ADC间的共同性稍差。这是由于布线差异和时钟差错的影响。这种测验办法也能够给出电路规划者一些规划依据,以能够削减布线差异和时钟差错对共同性所形成的影响。

本文的布景是散射计,采样后需求进行的信号处理包含:波门采样、数字下变频、波束组成、脉冲紧缩和滑窗求和。依据上述测验成果能够确认,本文布景散射计下的十六路ADC采样通道完全能够满意体系要求。

3 结束语

经过上述办法对很多的数据进行收集与剖析,本文完结了对多通道ADC的测验。在考虑到低通采样和带通采样的情况下,别离对偏置共同性、起伏共同性和推迟共同性进行了丈量。其间推迟共同性运用了两种办法,即FFT法和相关法。经过对以上的测验数据剖析,得出这两种办法本质上是相同的定论,仅仅相关剖析法为了进步剖析精度,需求完结

的时移和相关运算较多,速度较慢。测验成果很好的反映了各个通道的共同性,这种办法不只适用于本文布景所用的散射计体系,也适用于其他多路ADC通道的共同性测验。关于后期差错批改和后级数字处理也有很高的价值。