技能和立异正在引发新一轮的工业改造。当时全球集成电路工业正处于技能改造时期,摩尔定律推动速度现已大幅放缓,集成电路技能开展途径正逐渐向多功用交融的趋势改动。 2019年国际半导体大会高峰论坛上,台积电(南京)有限公司总经理罗镇球在其“半导体工业开展趋势”的主题讲演中指出。

台积电(南京)有限公司总经理罗镇球

现阶段,无论是电脑、手机仍是其他终端都需求人宣布指令的。罗镇球以为,未来这些设备或许机器之间是能够相互交流、相互下指令并服务于用户的,而这便是所谓的万物互联。毋庸置疑,半导体是IT职业的最首要驱动要素之一,半导体运用继续添加,社会对半导体技能的等待日积月累。

关于半导体工业的开展,罗镇球表明,台积电经过工艺支撑推动摩尔定律向前、经过立体封装推动摩尔定律向前、经过硬件和软件结合进步能效比。

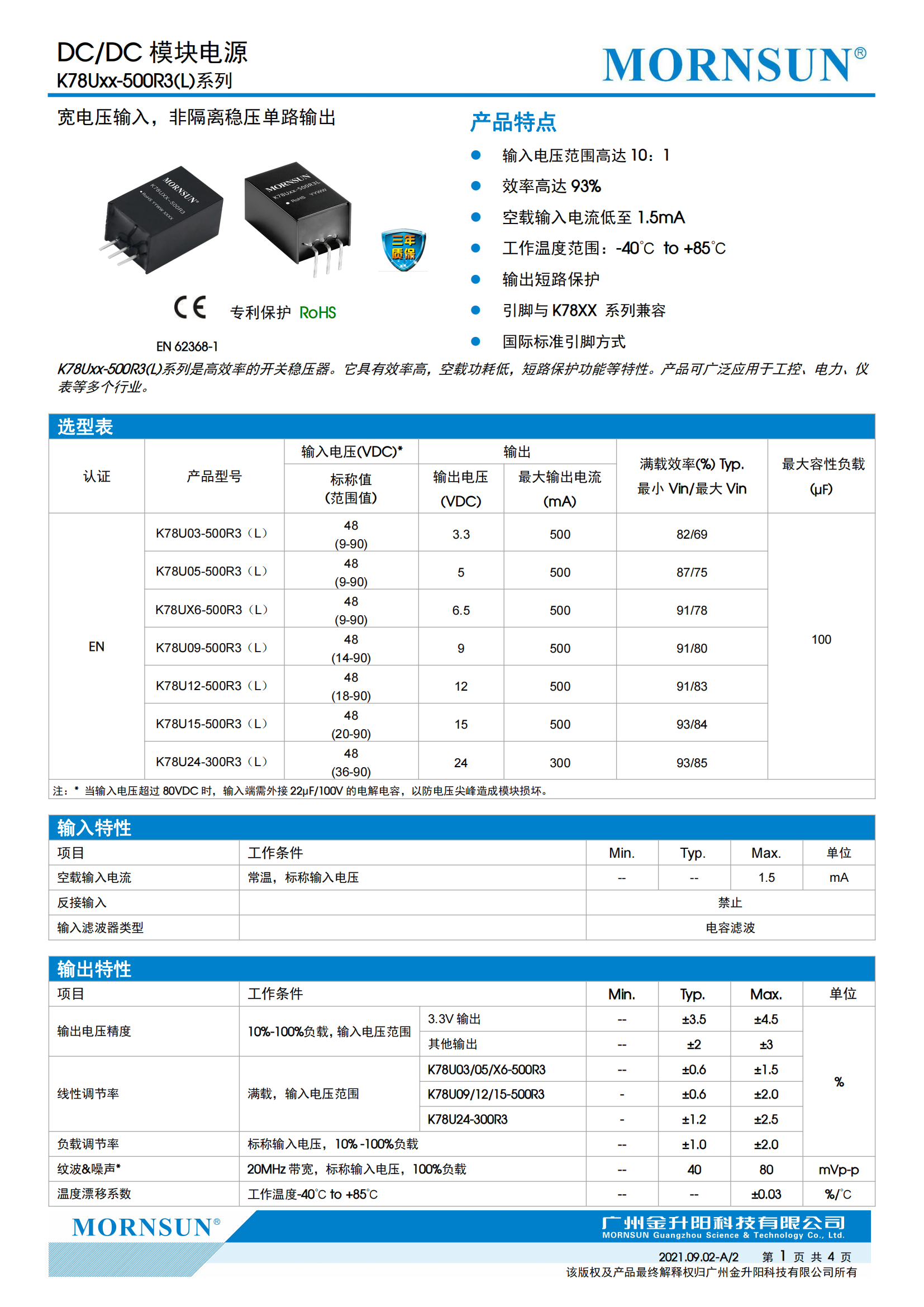

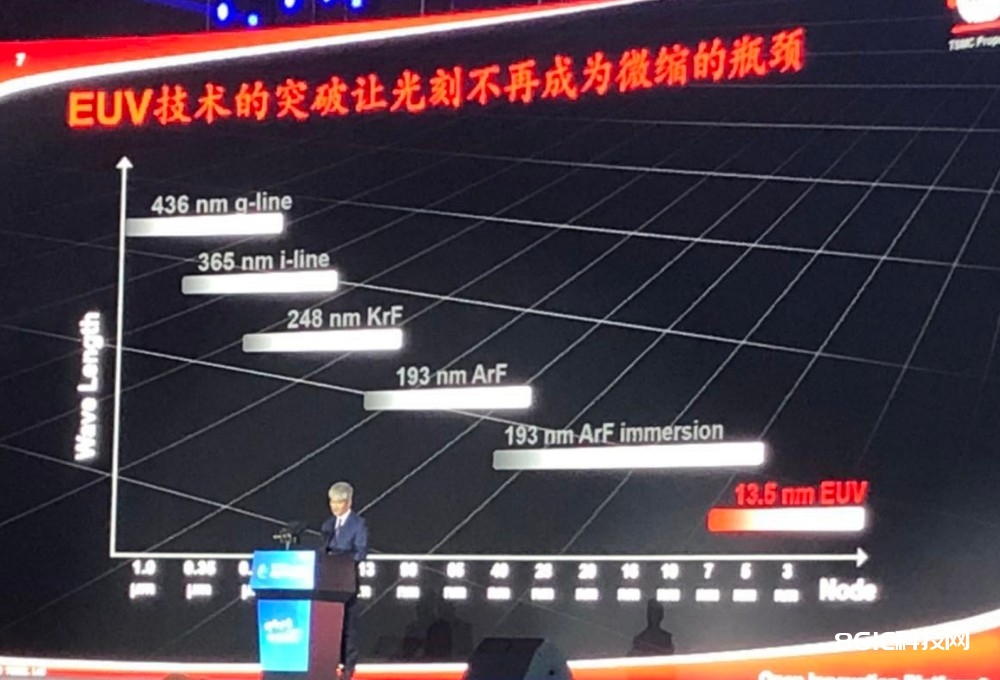

EUV助力光刻技能打破枷锁

在工艺的微缩演进进程中,EUV技能(远紫外线光刻技能)功不可没。光刻机的技能的难易首要调查其波长,波长越短技能难度越高,意味着其精度也就越好。

如上图,每一格表明10倍联系,台积电先后进入248、193纳米的光刻机阶段。193纳米的光刻机兼容性较为强壮,兼容40nm至7nm一切标准,现在7nm工艺芯片台积电现已做到批量生产,仍旧选用40nm的40光刻机。

从未来开展视点看,193纳米的光刻机波长是193,而EUV的波长是13.5纳米,这也就意味着未来有关EUV的枷锁现已打破。在未来,光刻打破的进程现已不再是难题。

新资料是下一步尽力方向

资料方面,晶体管结构由平整式变为立体式,现在台积电正着手研制一款更好的晶体管结构。别的,新式的二维资料具有许多传统资料所不具备的共同的光电功用,特别是其杰出的非线性光学特性在构筑高功用、新功用光电子器材方面现已展现了巨大的潜力。有关二维资料一般是三维立体结构,二维资料的轻浮意味着它的场效应越来越好、高度越来越低,这也预示了工艺方面能够做进一步的微缩。新资料是台积电下一步的尽力方向,加之台积电现在具有的晶体管架构“增幅”,也助力了半导体技能的继续开展和推动。

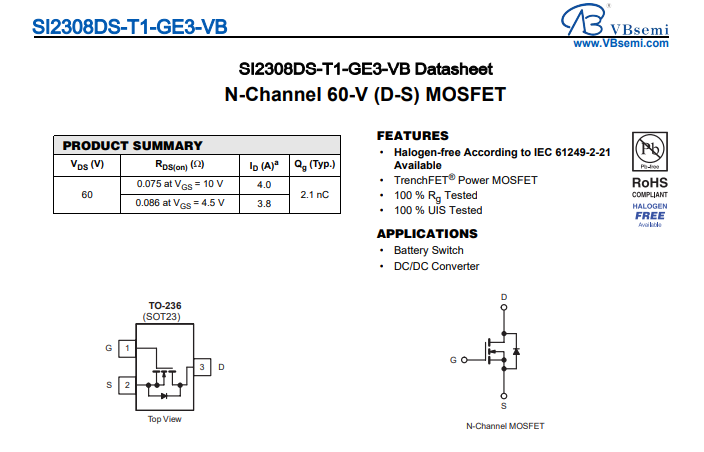

IC集成度进步剑指规划改造

台积电不只致力于存储器与CPU的结合,还会把各种不同功用的IC做异质性结合,包括微机电、射频等等。台积电未来开展趋势在于针对不同的运用场景,对不同芯片做异构集成(以封装的办法集成)。

IC规划方面,现阶段一般运用硅片与硅片连线,而将来会有必定的改造,详细如:打穿VF,下一列向上穿,以替代铜箔基板的衔接;或是6纳米连线,VF对VF直接衔接。间隔的缩短,意味着面积的缩小。

在开端规划IC时,选用将IC的规划区分成块的规划方案,便于将来更好的堆叠。I规划成一部分,逻辑规划成一部分,微机电规划成一部分,别离规划好后将各个部分串接。因为这种改动的进程,规划公司也需求在规划概念上做一些调整和改动。规划进程中,需求从头考虑在封装时拉线的间隔,这样更有利于面积的缩小。

进步能效需软硬件同步

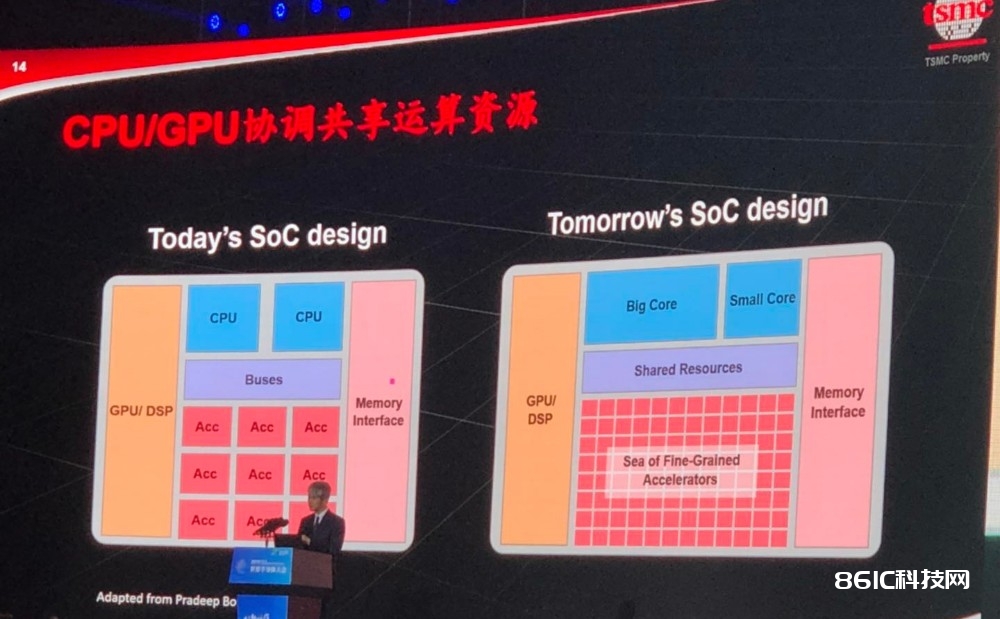

台积电针对进步能效比方面,施行了GPU专门处理绘图的相应措施,其不只进步了能效比,还可针对不同运用拓荒新的IC,以专门处理事情。有关未来开展,专用的DSP或CPU无法处理的事情,或可运用软件重构,硬件被软件重构后可履行不同的特别运用,以此来完成软硬结合,从而使能效进一步进步。台积电方针是能够比传统通用CPU能效比进步1000倍。

关于未来的运用场景未来的趋势是,因为场景需求,仍旧需求CPU、DSP。程序完成后,编译器会对硬件的架构进行考虑剖析。在履行程序时分,会从头构建修改结构,以此来应对特别运用场景。一切的功用在同一个运用场景中,经由软言语与编译器来优化、同享、运用加速器。

小结

晶体管的部分,台积电会继续适应摩尔定律向前开展,依托新资料,新架构,继续向前推动。关于3D封装,台积电运用继续堆叠的办法,使面积变小。规划方面得改造,助力IC集成度的体高。别的,软件与硬件结合的办法,能够充沛进步设备在运用的场景时的能效。