项目布景及可行性剖析

1.. 项目名称: HF/VHF数字调制多功用发射机

2.. 项意图首要内容及现在的发展状况:

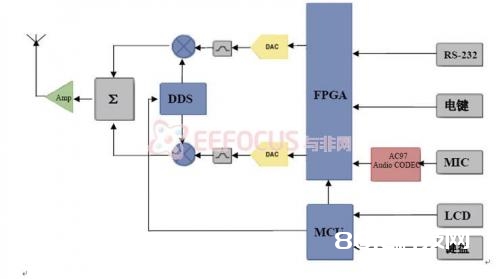

本项目首要的内容是:规划制造一台能作业在HF及VHF波段的数字调制发射机,能供给AM, FM,DSB,SSB等语音通讯调制形式,及ASK,FSK,PSK等数据通讯调制形式. 话筒输入的语音信号经 AC97 Audio CODEC 编码后输入FPGA进行数字调制, 电键和RS—232接口输入的数字信号经FPGA进行数字调制,各种调制形式能在瞬间彼此切换.

现在的发展状况:本项目已经过可行性证明,证明计划可行.现在正在进行子模块的功用区分,以及子模块性能参数的开始确认.

3.. 项目关键技能及立异点的论说:

本项意图关键技能是:数字实时调制;FPGA乘法器的复用;双路DAC正交输出;DDS和FPGA的归纳运用.

数字实时调制,要求对FPGA的逻辑资源有深化的了解.经过合理规划逻辑电路,运用流水线技能,进步FPGA的信号处理速度,以满意数字实时调制对FPGA处理速度的苛刻要求.

因为FPGA的乘法器数量有限,经过逻辑单元构成乘法器则会耗费很多的逻辑单元,不光不契合对本钱效益的要求,而且这样往往也不能满意多调制形式数字调制器对乘法器的巨大需求.在规划多调制形式数字调制器时有必要考虑怎么把有限的乘法器经过复用来削减对乘法器的需求,尽可能使用FPGA内部的乘法器,而不使用逻辑单元来构成乘法器.若用DSP芯片来完结多调制形式数字调制器, DSP芯片内部的乘法器在程序运行时就能得到复用,因而在完结多调制形式数字调制器的时分往往选用DSP芯片的计划而不选用FPGA的计划.

双路DAC正交输出与后边的DDS,两路混频器和加发器一起构成镜像按捺混频器,用于把DAC输出的信号进行频率的搬移,以满意输出信号掩盖HF和VHF频段的规划要求.因为两路DAC后接的LPF的相频特性不可能完全一致,因而在FPGA中有必要考虑添加补偿算法.

本项意图立异点在于:经过对各种调制形式Verilog完结的改善,在确保满意实时调制的状况下,复用乘法器,把逻辑单元的耗费削减到最低,然后削减体系的功耗.空余的逻辑单元为后继的体系晋级留下满足的逻辑单元资源.而且能够供给比多DSP芯片计划更高的可靠性和集成度,契合现代消费电子产品对体积的苛刻要求.

使用DDS+FPGA数字调制计划,相对于市面上消费通讯产品很多选用的模仿调制计划,具有可靠性高,抗搅扰才能强,体积小,调试简单,设备晋级简单等长处.

4.. 技能老练性和可靠性论说:

技能老练性:

以DAC+FPGA的根本计划为根底.合作DDS专用芯片产生正交本地振动信号,使用AC97 Audio CODEC进行音频信号的采样与编码,选用RS-232接口与PC机进行通讯,以MCU,LCD,键盘作为人机交互界面.以上这些是本体系的首要组成模块,它们都具有高老练性的特色,选用这些模块构成的设备现正被很多生产和出售,因而本体系所选用的根本技能是非常老练的.

技能可靠性:

本规划项目以V2PRO硬件开发渠道为根底,合作双路DAC,DDS信号产生,混频电路,以及宽带扩大器,人机交互模块构成. V2PRO硬件开发渠道具有集成度高,扩展简单的特色,还集成有AC97 Audio CODEC和稳压供电电路,因而V2PRO硬件开发渠道具有高可靠性的特色.

双路DAC,DDS信号产生器,宽带扩大器均选用专用芯片构成,混频电路则选用混频器模块, 人机交互模块没有选用FPGA内部的PowerPC来完结,首要是根据EMI/EMC的考虑,防止把外部的搅扰引进FPGA影响体系输出信号的质量. 人机交互模块选用工业级的具有适当抗搅扰才能的单片机,程序选用代码圈套等办法进步抗搅扰才能, 人机交互模块的电路严厉依照EMI/EMC的要求规划,添加各种抗搅扰电路,而且在经过充沛测验后才接入体系.上述电路因为很多选用专用芯片和模块来替代分立元件电路以及以谨慎的精力进行规划,因而具有可靠性高,调试简单,体积细巧等长处.

项目施行计划

1.计划根本功用框图及描绘:

①话筒输入的语音信号经 AC97 Audio CODEC 编码后输入FPGA进行数字调制,可供给AM, FM,DSB,SSB等语音通讯调制形式.

②电键和RS—232接口输入的数字信号经FPGA进行数字调制,可供给ASK,FSK,PSK等数据通讯调制形式.

③实时的高速数字信号调制经过FPGA来完结,各种调制形式能在瞬间彼此切换.

④两组DAC在FPGA的操控下可输出正交的已调制信号.

⑤两组DAC后接LC低通滤波器,用于滤除高次谐波.

⑥DDS,两组混频电路,以及加法器用于改动终究输出信号的频率.

⑦加法器后接的扩大器用于缓冲和扩大终究的输出信号.

⑧单片机,LCD,键盘构成人机交互模块,用于在脱离PC机的状况下,操控体系的一切功用.

2.需求的开发渠道:

①完结本计划所需求的根本功用、功用、接口

完结本计划需求FPGA具有满足多的逻辑单元,而且具有16位或以上数量满足多的乘法器,用于完结DSP算法. 具有高速扩展接口,用于衔接两路DAC. 具有低速扩展接口,用于衔接人机交互模块和电键.具有AC97 Audio CODEC,用于对话筒输入的语音信号进行编码.具有RS-232端口,用于与PC机相连.具有稳压供电电路,以便接上5V电源即可正常作业,简化整个体系供电电路的规划.具有高速时钟源电路,为FPGA和外部的DAC供给时钟源.

②所需求的政策FPGA开发渠道,简述为什么需求此渠道

所需求的政策FPGA开发渠道是V2PRO,因为本项目要求FPGA具有16位或以上数量满足多的乘法器,需求有AC97 Audio CODEC, RS-232端口, 高速扩展接口, 低速扩展接口,高速时钟源电路,独立的稳压供电电路.

③是否需求其它配套的开发工具

除了Xilinx ISE Foundation, ModelSim XE-III外,还需求LabVIEW用于开发PC机上的RS-232通讯操控软件.

3.计划施行过程中需求开发的模块

需求开发的FPGA模块包含:

①DAC输出模块:用于把调制模块输出信号的经过高速扩展接口输出到DAC和操控DAC的作业状况.

②调制模块:用于完结AM,FM,DSB,SSB, ASK,FSK,PSK,的实时数字调制.

③RS-232接口模块:用于经过RS-232接口与PC机通讯,并把PC机传来的待发射数据传入调制模块.

④电键接口模块: 用于经过低速扩展接口衔接电键,把电键输入的数据传入调制模块.

⑤AC97 Audio CODEC接口模块: 用于把AC97 Audio CODEC输入的音频量化数据输入调制模块.

⑥功用操控模块: 用于经过低速扩展接口与人机交互功用子板相连,操控体系的各项功用.

模块开发的办法:

开发办法是选用自顶而下的规划办法,首要确认该模块中各子模块的详细功用和彼此的互连联系,然后确认各子模块的详细参数.在确认各子模块的详细参数和互连联系后,在Xilinx ISE Foundation顶用Verilog来完结.最后用ModelSim XE-III对该模块和其子模块别离进行仿真.

4.体系终究要到达的性能指标

输出频率规模10MHz~150MHz,输出阻抗50ohm,输出功率>=10dBm. 作业温度0~50,频率步进距离1Hz,频率稳定度1ppm(开机后10分钟),音频呼应规模(-6dB)500Hz~2.5KHz,.可供给AM, FM,DSB,SSB等语音通讯调制形式,可供给ASK,FSK,PSK等数据通讯调制形式.话筒可输入语音信号, 电键和RS—232接口输入数字信号.PC机经过RS-232接口与本体系通讯,透过PC机上的软件,能够操控本体系的各个功用,而且能够使用PC机上的软件进行数据的发送.使用本体系的用户交互模块,能够在脱离PC机的状况下操控本体系的各个功用.

需求的其它资源

1.规划输入输出功用子板

①双路DAC功用子板:使用8bit或12bit 的DAC芯片来完结.选用高速扩展接口与V2PRO硬件开发渠道相衔接.此功用子板独自进行规划和调试,测验经过后再和体系衔接在一起.

②DDS信号产生功用子板:使用ADI公司的DDS芯片产生正交本地振动信号,与人机交互功用子板相连. 此功用子板独自进行规划和调试,测验经过后再和体系衔接在一起.

③混频功用子板:加法器和两个混频器一起构成此功用子板.与双路DAC功用子板,DDS信号产生功用子板,宽带扩大器功用子板相连. 此功用子板独自进行规划和调试,测验经过后再和体系衔接在一起.

④宽带扩大器功用子板:选用专用宽带扩大芯片构成.与混频功用子板相连. 此功用子板独自进行规划和调试,测验经过后再和体系衔接在一起.

⑤人机交互功用子板:选用单片机,矩阵键盘,LCM构成,用于在脱离PC机的状况下,完结体系的操控和人机交互. 与V2PRO硬件开发渠道经过低速扩展接口相连,与DDS信号产生功用子板相连. 此功用子板独自进行规划和调试,测验经过后再和体系衔接在一起.

2.测验设备

指针万用表,数字万用表,200M数字示波器,200M频谱剖析仪,5V稳压电源,20M函数信号产生器, 逻辑剖析仪

3.政策、开发工具

规划软件包含: Xilinx ISE Foundation, ModelSim XE-III,Cadence SPB 15.7 , Synopsys Saber Z-2007 , Multisim v9 , Filter Solutions 2006 , Proteus 7.1 , AVR Studio 4, WinAVR, LabVIEW

硬件开发渠道包含: V2PRO, BASYS