在运用最新模数转化器(ADC)和数模转化器(DAC)规划体系时,我已知道了许多有关JESD204B接口规范的信息,这些器材运用该协议与FPGA通讯。有一个没有深化评论的主题便是处理ADC至FPGA 和FPGA 至DAC链路问题的协议部分,这两种链路原本便是相同的TX 至RX体系。作为一名运用工程师,所需求的便是了解其间的细微差别,这样才干充分利用JESD204B经过现有LVDS和CMOS接口供给的优势。

有了JESD204B,无需再:

● 运用数据接口时钟(嵌入在比特流中)

● 忧虑信道偏移(信道对齐可修正该问题)

● 运用很多I/O(高速串行解串器完成高吞吐量)

● 忧虑用于同步多种IC的杂乱办法(子类1 和2)

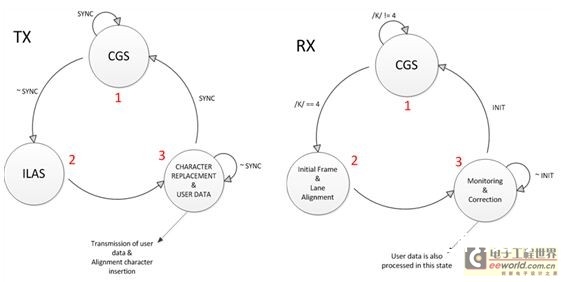

咱们来考虑一种由ADC 等数字源向FPGA发送数字数据的简略状况。在正确发送或接纳数据之前,有几件事有必要要做,如图1所示以及下文所阐明的那样。

图 1 JESD204B 协议状况图

1. 代码组同步(CGS)- 不需求接口时钟,因而RX有必要将其数位及字鸿沟与TX串行输出对齐。RX 可向TX发送SYNC恳求,让其经过一切信道发送一个已知的重复比特序列,本例中每字符每K 是K28.5。切当的字符比特序列可在规范中找到。RX 将移动每个信道上的比特数据,直到找到4个接连的K28.5字符停止。这时,它不只将知道比特及字鸿沟,并且现已完成了CGS。随后,它会撤销对SYNC的断语,而TX和RX则都会进入下一个状况:初始信道对齐序列(ILAS)。

2. ILAS – JESD204B 协议的一个杰出特性可完成经过RX模块中的一些FIFO/缓冲器吸收信道偏移。在完成CGS后,TX 可在每个信道上发送已知的字符帧调集,称为信道对齐序列(以每字符每R K28.0 开端,以每字符每A K28.3 完毕)。收到对齐序列后,RX 会对数据进行FIFO缓冲,直到一切信道都收到完好的对齐序列。由于现已知道了整个序列,因而信道随后可从头对齐,这样每个信道上的任何信道偏移都可经过FIFO存储器吸收,并且,信道随后还可在相同的时刻点、在RX 模块内开释该数据。这可缓解为串行解串器信道供给匹配布局的需求,由于信道偏移可经过FIFO存储器吸收。

3. 用户数据 – 在代码组同步及信道对齐后,就可正确接纳用户数据。如果在该最终状况时用户数据无效,则需求从头启动本进程,RX 会发送一个SYNC恳求从头开端该进程。