ADC 逐次比较型

1.转化方法

直接转化ADC

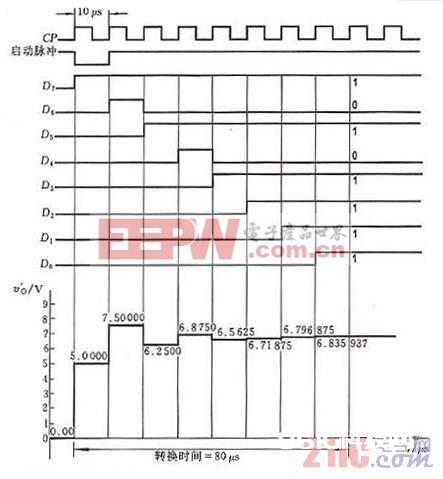

2.电路结构

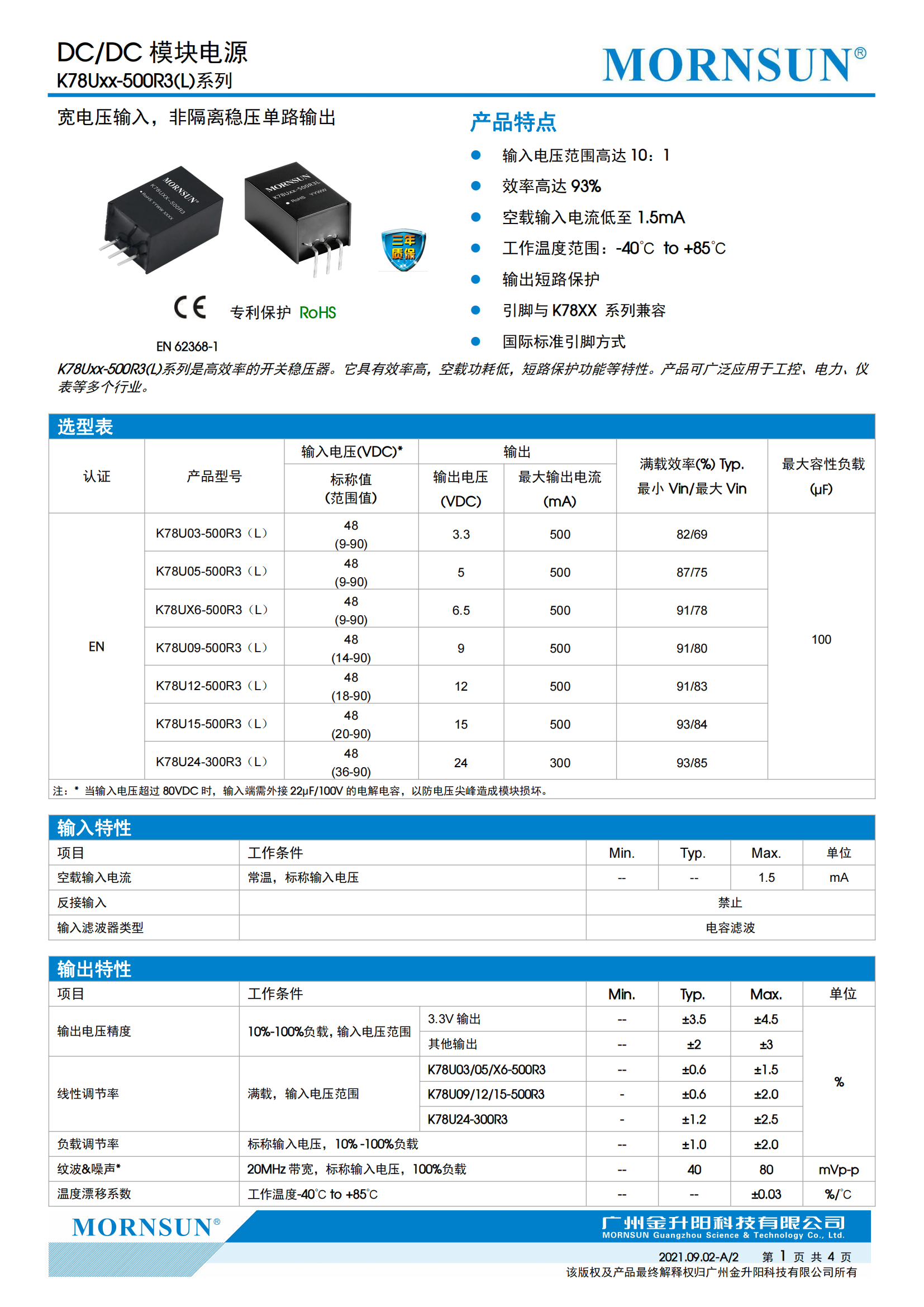

逐次迫临ADC包含n位逐次比较型A/D转化器如图11.10.1所示。它由操控逻辑电路、时序产生器、移位寄存器、D/A转化器及电压比较器组成。

图11.10.1逐次比较型A/D转化器框图

3.作业原理

逐次迫临转化进程和用天平称物重十分类似。天平称重物进程是,从最重的砝码开端试放,与被称物体跋涉比较,若物体重于砝码,则该砝码保存,不然移去。再加上第二个次重砝码,由物体的分量是否大于砝码的分量决议第二个砝码是留下仍是移去。照此一向加到最小一个砝码停止。将一切留下的砝码分量相加,就得此物体的分量。模仿这一思路,逐次比较型A/D转化器,便是将输入模仿信号与不同的参阅电压作多次比较,使转化所得的数字量在数值上逐次迫临输入模仿量对应值。

对11.10.1的电路,它由发动脉冲发动后,在第一个时钟脉冲效果下,操控电路使时序产生器的最高方位1,其他方位0,其输出经数据寄存器将1000……0,送入D/A转化器。输入电压首要与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI VREF/2,则为0。比较成果存于数据寄存器的Dn-1位。然后在第二个CP效果下,移位寄存器的次高方位1,其他低方位0。如最高位已存1,则此刻 vO=(3/4)VREF。所以v1再与(3/4)VREF相比较,如v1≥(3/4)VREF,则次高位Dn-2存1,不然Dn-2=0;如最高位为0,则vO=VREF/4,与vO比较,如v1≥VREF/4,则 Dn-2位存1,不然存0……。以此类推,逐次比较得到输出数字量。

为了进一步了解逐次比较A/D转化器的作业原理及转化进程。下面用实例加以阐明。

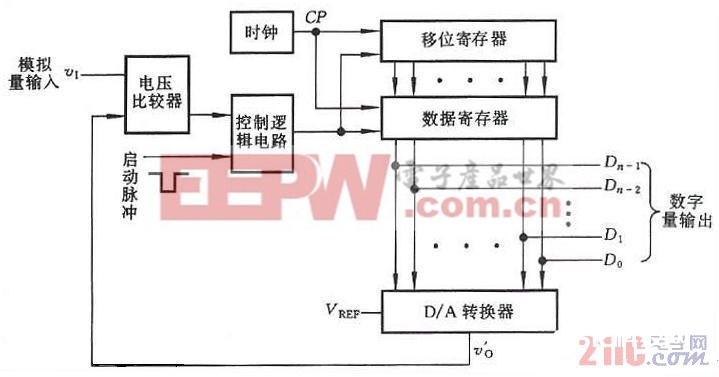

设图11.10.1电路为8位A/D转化器,输入模仿量vA=6.84V,D/A转化器基准电压VREF=10V。 依据逐次比较D/A转化器的作业原理,可画出在转化进程中CP、发动脉冲、D7~D0及D/A转化器输出电压vO的波形,如图11.10.2所示。

由图11.10.2可见,当发动脉冲低电平到来后转化开端,在第一个CP效果下,数据寄存器将D7~D0=10000000送入D/A转化器,其输出电压 v0=5V,vA与v0比较,vA>v0存1;第二个CP到来时,寄存器输出D7~D0=11000000,v0为7.5V,vA再与7.5V比较,因vA7.5V,所以D6存0;输入第三个CP时,D7~D0=10100000,v0=6.25V;vA再与v0比较,……如此重复比较下去,经8个时钟周期,转化完毕。由图中v0的波形可见,在逐次比较进程中,与输出数字量对应的模仿电压v0逐步迫临vA值,最终得到A/D转化器转化成果D7~D0为10101111。该数字量所对应的模仿电压为6.8359375V,与实践输入的模仿电压6.84V的相对误差仅为0.06%。

图11.10.2 8位逐次比较型A/D转化器波形图