FPGA (现场可编程门阵列)由于其硬件并行加快才干和可编程特性,在传统通讯范畴和IC规划范畴大放异彩。一路走来,FPGA并非一个新式的硬件器材,由于其开发门槛过高,硬件加快算法的发布和布置维护要求十分高,FPGA的运用一向是高冷的佳人,没有走入寻常百姓家,导致FPGA的核算潜力还没有得到深化的发掘。

接下来,咱们来看看阿里云对它进行了怎样的改造。

阿里云ECS的异构核算团队和高功用核算团队一向致力于将核算资源“平民化”;高功用核算团队在做的E-HPC便是要让一切云上用户都能够瞬间具有一个小型的超算集群,使得超算不再仅仅是一些超算中心和高校的特权;而咱们异构核算团队则致力于将现在最快、最新的核算设备在云上供给给用户,使得从前高冷的核算资源不再拒人千里之外:咱们推出了FPGA云服务器FaaS 服务, 其间的F1和F2实例现已对外供给服务,能够经过一键布置的方法把Intel和Xilinx的小规范的器材核算才干赋予客户。

今日咱们很快乐地宣告:新晋的大规范FPGA实例,根据Xilinx 16nm Virtex UltraScale+ 器材VU9P的异构核算实例F3在阿里云上线了!

咱们借此机会,对阿里云FPGA核算服务(下面简称FaaS)本身,以及这次发布的F3实例的底层硬件架构平和台架构做一个技能解读。

FaaS

阿里FPGA云服务器渠道FaaS(FPGA as a Service)在云端供给一致硬件渠道与中间件,可大大下降加快器的开发与布置本钱。加快器开发商的加快器能够构成服务供给给加快器用户,消除加快技能与最终用户的硬件壁垒。用户则能够在无需了解底层硬件的状况下,直接按需运用加快服务。

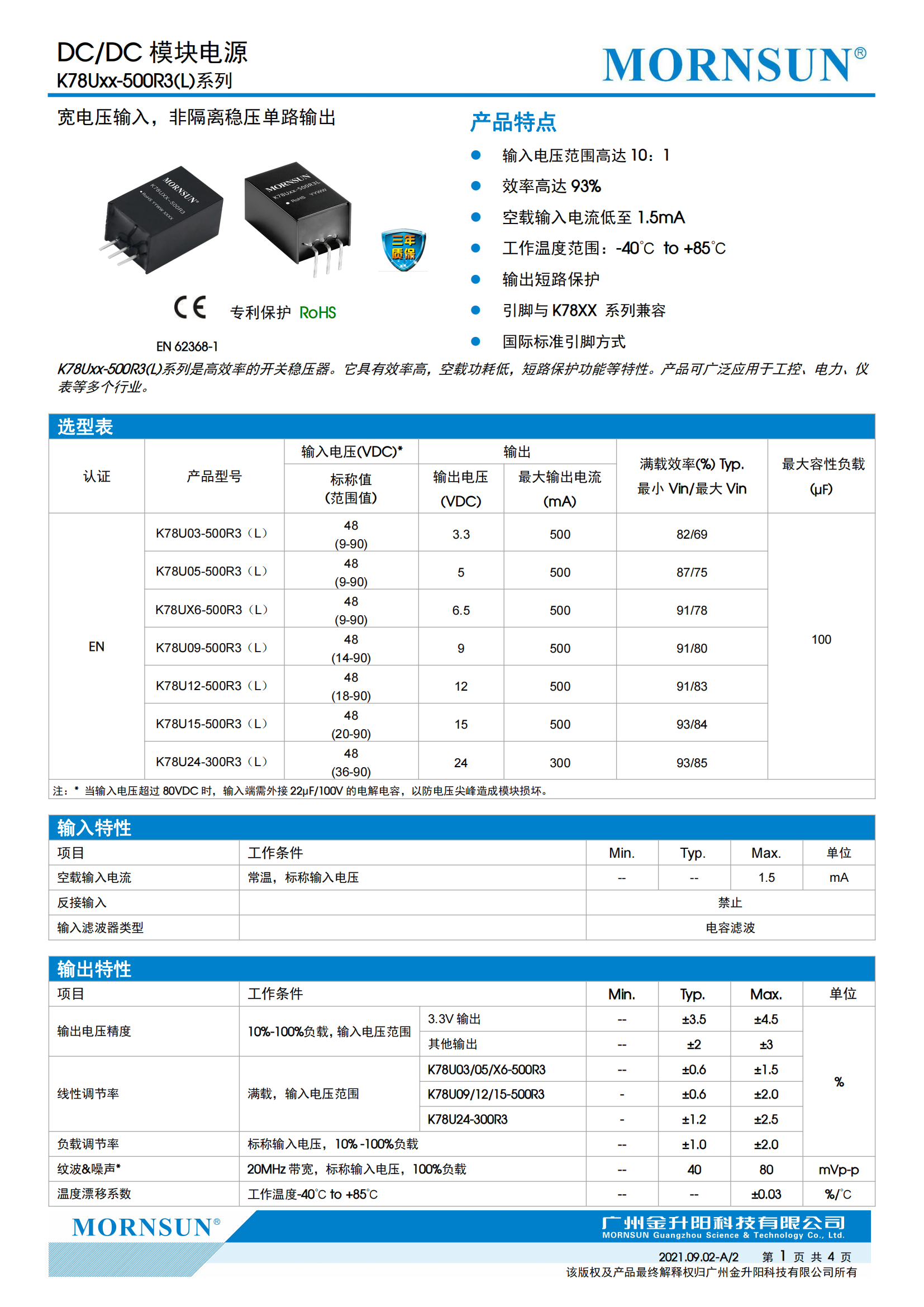

为了给加快器供给方和运用方供给愈加高效、一致的开发及布置渠道,FaaS供给两大套件:HDK和SDK。

HDK

HDK给一切的加快器开发者供给一致的FPGA硬件接口,提早帮用户处理了FPGA开发中难度最大的高速接口开发及调试,例如PCIe、SERDES接口、DDR控制器等等;使得用户能够直接得到硬件渠道和FPGA接口的最大功用,不会由于团队开发才干和经历的短缺,形成硬件渠道功用糟蹋;高效、牢靠、一致的接口套件也为云上渠道的安全阻隔、设备安稳供给了确保,不会由于用户的接口规划问题,形成服务器宕机;一同能够根绝用户在FPGA端对主机的非法操作,为整个云上安全供给确保。

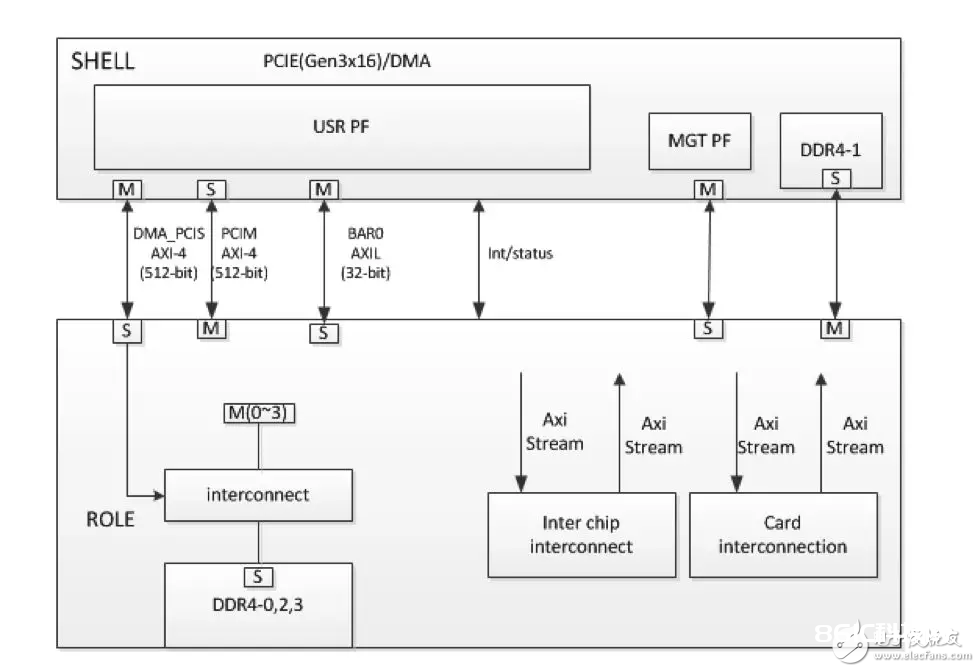

HDK包括两个部分,Shell和 Role;Shell布置在静态区域,供给上述一致接口部分。

在供给一致接口、安全性和快捷性的前提下,阿里云FaaS HDK 也尽最大的尽力确保用户规划的灵敏性,Role的概念应运而生。Role布置在动态区域,是在Shell之外,预先开发并供给的,用户能够合作用户逻辑(Customer Logic)运用。不同于Shell,用户能够根据需求,随时替换Role部分;这种Shell + Role的组合方法,确保了Shell的最轻量化和安稳性,又统筹了一致性、快捷性和灵敏性。

SDK

SDK包括两个部分:

和HDK(Shell+Role)对应的主机端驱动(Drivers)和软件库(Libraries)

FPGA办理东西 faascmd套件

驱动和软件库和HDK的Shell以及Role相对应,和HDK一同,为用户供给一致及灵敏的软件支撑,比方DMA驱动、寄存器拜访驱动等等。

faascmd东西套件为用户供给云上FPGA办理服务,包括安全校验、FPGA镜像生成、下载及办理、FPGA加快卡状况查询反应等功用。公有环境运用FPGA,需求考虑用户FPGA文件的安全,faascmd供给的秘钥及OSS bucket指定机制,有用确保了用户的FPGA下载文件的私密性。在线下的开发及运用中,开发者直接对FPGA进行下载操作,但在云上环境,用户对公有的FPGA资源直接操刁难安全形成较大影响。Faascmd东西会对用户操作请求和物理FPGA资源进行阻隔,确保了用户下载安全的一同,供给给用户相似线下操作的体会;一同会对用户提交的网表进行校验,进步安全、下降危险。faascmd一同也供给调用接口,用户能很容易地在自己的App中调用办理东西,结合本身加快器特性完成各种办理功用。

FaaS 的IP商场

FaaS下降了FPGA开发者的开发准入门槛:云上即开即用的FPGA资源、灵敏的付费形式使得硬件资源触手可及;一同简化了开发流程,一致了开发接口,把中心加快逻辑从周边硬件设备的接口调试中阻隔出来,使得FPGA的新式运用能够只重视事务加快的中心逻辑,快速迭代;在这两点上,阿里云的FaaS 迈出了FPGA核算资源平民化的第一步。

但即便是大大简化了开发流程、供给了触手可及的硬件资源,FPGA仍然有必定的开发门槛。怎样把已有的FPGA 逻辑IP价值最大化,联通FPGA加快的需求方和供给方来扩展生态呢?重要的一点便是怎样处理在公共云数据中心层面确保FPGA加快IP的安全性,特别是对不可信的第三方进行输出和布置这个难题, FaaS是怎样处理这个问题的呢?

答案是经过阿里云FaaS的IP商场。技能上,经过与Xilinx联合开发的定制虚拟化技能到达IP加快与布置环境的强阻隔,IP的用户与IP的网表文件彻底阻隔,网表文件的传输、布置、加快流程全程对用户都不可见;一同加快核算才干又能够透明地向运用该IP的第三方用户敞开,这是阿里云在FPGA云上加快服务的别的一个技能立异。这个立异,彻底根绝了FPGA IP在云上输出的时分被盗版的或许,供给了十分高的安全维护机制。

愈加严厉的保密机制也在规划中:很快能够经过阿里云的KMS加密服务对IP进行加密维护,每次对IP加载前都需求向KMS服务获取秘钥解密,这样一来针对IP的运用下载有据可查;并且使得IP发布方的IP在数据中心内部都是安全的,由于没有了IP供给方的KMS秘钥,即便是阿里云也无法对加密的网表进行解密操作。

在阿里云FaaS IP 商场的协助下,即便是从来没有任何FPGA开发经历的用户,也能够一键从IP商场中获取相应的加快逻辑,并快速布置到对应的FPGA器材上面去。咱们信任,经过即开即用的硬件资源、一致的软硬件逻辑开发接口和IP商场,阿里云能够真实完成FPGA核算资源平民化的许诺。

F3硬件架构

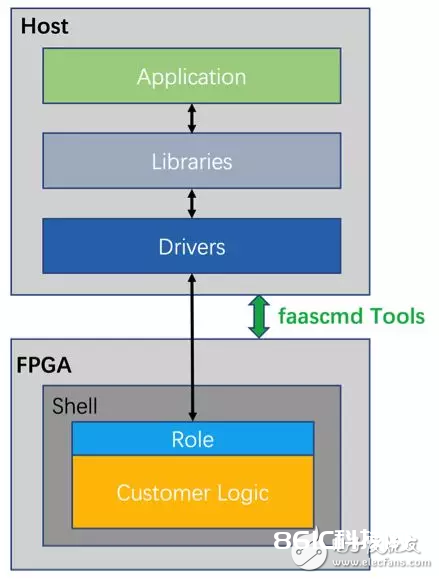

阿里云FaaS的F3实例在底层硬件上,是运用阿里云自主研制的高功用单卡双芯片的VU9P的板卡。这儿要划要点啦:单卡双芯片。必定有用户要问为什么要这么规划呢?单卡双芯片的硬件规划有什么优点呢?

首要,关于用户来说,经过单卡双芯片这样的规范规划,与阿里云配套自研的服务器一同,最高能够供给单实例16 块 VU9P的核算实例。16块 VU9P是十分高的核算密度了,这是规划单卡双芯片的第一个意图:经过进步核算密度,在平等核算单元下集成了更多的加快芯片,能够有用下降单位核算力的本钱,从本钱大幅下降和单位实例的笔直核算力提升上,客户能够两层获益。

单卡双芯片的两个VU9P芯片经过PCIe 桥接入体系,那么双芯片之间的相互通讯呢?是不是只能经过PCIe的总线来进行呢,答案是否定的,除了FPGA Direct这种经过PCIe相互通讯的才干之外,在阿里云的自研的板卡上也是有特别考虑的。在两个芯片之间,咱们规划了一个高速互联通道,使得两个FPGA之间能够经过这个特别的通道以高达600Gb/s的速率进行通讯,这个通讯技能咱们称之为FPGA Link。要知道,现在的数据中心干流布置的接入交流机光口通讯也只能到达100Gb/s的通讯速率,更高的200Gb/s的交流机还在试布置中。

试想一下,无需额定的交流机和光口硬件,两个FPGA芯片能够经过FPGA Link技能以超短时延经过6倍于干流光口通讯的速率进行通讯,这个将会以极低的本钱协助用户敞开很多新的FPGA加快运用形式。比方,小规模的芯片仿真,需求两个器材才干布置得下的状况,能够将全体仿真模块拆解之后布置到两个芯片上,两个芯片之间的数据通路和同步信号经过高速通道互联;还有其他的运用场景,需求把功用模块布置到两个FPGA芯片之上,而两者之间需求很多的数据交流,比方视频转码场景:把小规模可是模块数目比较多的解码单元、视频处理单元布置到一个FPGA之上,把面积占用比较多的编码单元放到别的一个FPGA上,编解码模组之间经过高速互联交流裸视频流。这将大大改进布置的难度,以及极大的解耦两个模块之间的相互依赖和规划难度。以上举了两个比如,读者必定能够触类旁通地想到,其他需求流水线处理并需求很多数据交流的场景,阿里云的F3实例的双芯片实例能够为客户供给最大的价值。

不少运用场景对板载的DDR存储仍是有要求的。阿里云的F3实例,为每个FPGA搭配了客户可见的64GB的DDR内存,这64GB的DDR分红4个通道,别离连接到VU9P的3个硅单元上面,其间一个通道对应的16GB DDR保存常驻,其他3个通道对应的48GB存储以可选的方法可被客户逻辑加载运用。

现在,咱们看到了双芯片实例除了FPGA Direct技能和高达600Gb/s的FPGA Link高速互联才干之外,别的值得一提的是:双芯片的实例与其他的双芯片实例板卡之间也能够经过400Gb/s的光口进行互联,并且400Gb/s的以太协议驱动是经过Xilinx预置的MAC硬核来加快,不占用逻辑面积;经过以太或许自定义的轻量级通讯协议,能够在16芯片之间,以及更多的芯片之间建立2维Mesh或许环形互联,进一步扩展多片互联的运用形式和运用场景。

最终,上一张图,让咱们对上面做的硬件的技能解析有一个更具体的知道:

F3逻辑结构

F3逻辑结构,技能剖析之前,先给咱们上一幅逻辑架构图:

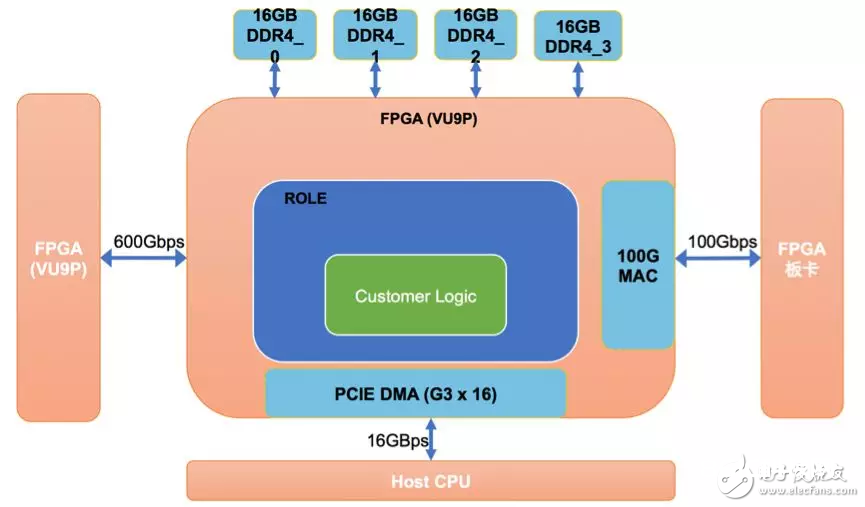

SHELL和ROLE概念

★SHELL:

Shell是FPGA的静态区域,内部包括用户PCIe、办理PCIEe、板卡办理体系和一个DDR拜访通道。为了进步板卡的安全和安稳性,用户无权修正SHELL区域。

★ROLE:

咱们在规划中提出了Role的概念,Role和Shell是相似的封装。而Role跟Custom Logic一同在动态区域。Role的提出使咱们能够愈加轻量化Shell。咱们经过Role完成了同一个Shell既能够支撑OpenCL开发,也能够支撑RTL开发;最终便是Role的再次笼统下降了用户关于FPGA的开发门槛。咱们供给根底的Role,也答应用户自行规划Role。咱们期望更多第三方的规划者经过共享自己Role,使得FaaS渠道愈加精彩。

ROLE内部结构简介

Interconnect:该部分主要是供给给用户四路DDR通道的拜访和USER_PCIe对四路DDR通路的拜访。 该模块协助用户阻隔了时钟域,运用户逻辑在同一个时钟域上对4路DDR通道进行拜访。

Inter chip interconnect: FPGA 单卡双芯片间互联通路;

Card interconnect: FPGA 卡间互联通路;

Custom Logic:用户自定义逻辑部分;

Custom Logic介绍

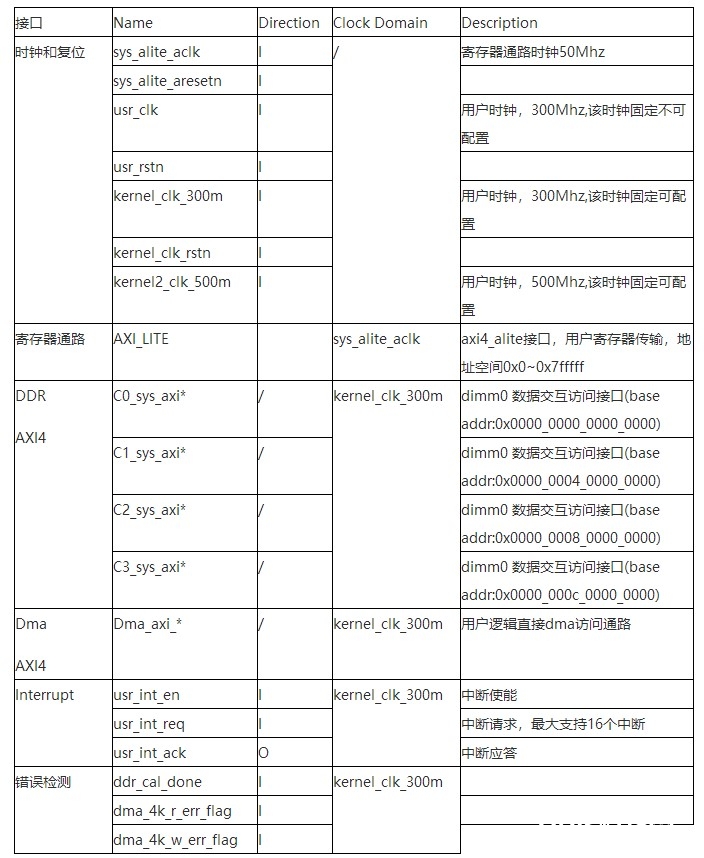

用户逻辑是归于Role的一部分,归于动态加载区域。 为了便利用户规范化运用,咱们在RTL规划中运用了规范的AXI-4和AXI-LITE接口。

1.咱们将具体介绍用户接口,其列表如下:

注:板间互联,卡卡互联接口邀测阶段缺省不供给,需求特别请求对外敞开。

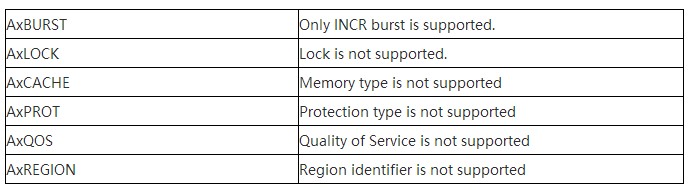

2.AXI-4 and AXI-Lite 约束

3. 正如咱们在介绍Role中所述,用户能够定制化Role操作。咱们阿里云FaaS团队为了便利用户更有用的运用渠道,多个Role版别正在发布中,敬请重视。下降用户运用门槛,缩短开发时刻,健全FPGA运用生态始终是咱们的任务。