1 前语

跟着FPGA的飞速发展与其在现代电子规划中的广泛运用,越来越多的试验和规划中会运用FPGA与RS232通讯。与此同时, FPGA具有功能强大、开发进程出资小、周期短、可重复编程等特色。在FPGA芯片上集成了串行接纳功能模块,然后简化了电路、缩小了电路板的体积、提高了可靠性。本文首要介绍环绕FPGA所规划的契合 RS232规范的串行接纳模块。

2 异步串行通讯原理

串行通讯分为两种类型:同步通讯办法和异步通讯办法。本规划选用的是异步通讯办法,其的特色是:通讯的发送方和接纳方各自有独立的时钟,传输的速率由两边约好。国际上规则的一个串行通讯波特率规范系列是:110、300、600、1200、1800、2400、4800、9600、 19200,单位是 bps。本文选用的是 19200bps。

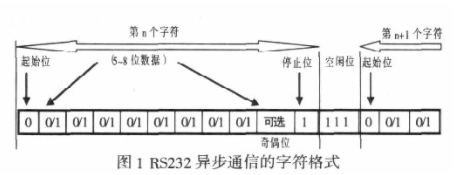

异步传输是一个字符接一个字符传输。一个字符的信息由开端位、数据位、奇偶校验位和中止位组成。每一个字符的传送靠开端位来同步,字符的前面是一位开端位,用下降沿告诉接纳方传输开端,紧跟着开端位之后的是数据位,传输时低位在前、高位在后,字符自身由5~8位数据位组成。数据位后边是奇偶校验位,昀后是中止位,中止位是高电平,标志一个字符的完毕,并为下一个字符的开端传送做预备。中止位后边是不定长度的闲暇位。中止位和闲暇位都规则高电平,这样能够确保开端位开端处有一个下降沿,如图1所示。 3 硬件接口电路原理规划

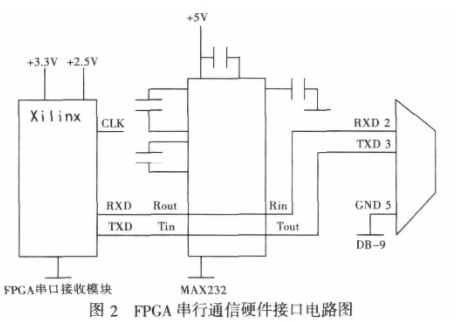

在串行通讯中,遍及选用的是 RS232-C接口的规范。 RS232-C接口信号引脚的衔接办法规则了25芯的D型衔接器DB-25,本规划选用的是一个 9芯的D型衔接器DB-9,而且用昀为简略常用的三线制接法,即地、承受数据和发送数据三脚相连。

本规划的硬件接口电路图如图2所示,由三部分组成: FPGA串口接纳模块、 MAX232和DB-9。FPGA选用的是Xilinx公司的SPARTAN系列的XC2S50芯片,其封装为TQ144。 MAXIM公司的MAX232CPE是为满意EIA/TEA-232E的规范而规划的,具有功耗低、波特率高、价格低一级长处。作业电源为 +5V,外界电容仅为 luF,为双组 RS-232收发器。MAX232有两个发送器,本规划只用其间一个发送器,别的一个发送器的输入端接地、输出端悬空。

异步数据接纳进程可作为一个全体来完成,数据由 DB-9的RxD端输入,经过 MAX232进行电平转化由FPGA串口接纳模块的 RxD端进入,然后在串口接纳模块内部对接纳来得数据进行判别,并昀终完成对FPGA输出信号的操控。

4 FPGA接纳串行数据的软件规划

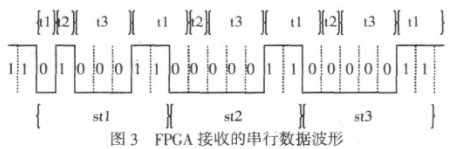

本计划选用的串行异步通讯的帧格局为:1位开端位+5位数据位+1位中止位。经检测与剖析,假如现已确认异步通讯的帧格局,那么每个字符就能够分别用固定的 7位数据表明。比方:字符‘ 0’:‘0000011’;字符‘ 1’:‘0100011’。其间第 1位数据‘ 0’为开端位,昀后 1位数据‘1’为中止位,中心 5位数据为数据位。例如:用串口调试帮手软件发送字符串‘100’,则会在 FPGA的 RxD引脚测得如图 3的波形。其间, st1,st2,st3表明先后发送的 3个字符, t1,t2,t3则表明对每个字符进行检测时所经过的 3种状况。

正如图3波形所示,接纳逻辑首要经过检测输入数据的下降沿来查看开端位。然后发生接纳时钟,运用接纳时钟来采样串行输入数据。由于字符‘0’和‘1’在5位数据位中的仅第一位有差异,因而只需精确地将第一位数据检测出来就能够得出串口调试帮手所发送的字符串。再运用移位操作,将字符串存储在缓存器(即另一组能够更新的字符串)中。

至于剩余的4位数据位和一位中止位,就能够不随接纳时钟采样。待串口调试组手发送的字符串悉数存储之后,一同在该模块中进行判别,并依据字符串的不同来操控FPGA不同的输出。接纳时钟是依据数据传输的波特率发生的:接纳时钟= 16×19200Hz。它始于开端位的下降沿,总算第5位数据位的上升沿。下面是完成检测第1个字符的VHDL源程序。

if(clk0‘event and clk0=’1‘)then —-外部时钟

case state is

when st1=》 —-第1 个字符开端

case tate is

when t1=》 —-开端位开端

if(rxd=’1‘)then —-未到下降沿不计数

cnt16 《= “0000”;

cnt48 《= “000000”; —-一切时钟清零

else cnt16 《=cnt16+1; —-下降沿来,开端位计数开端

end if;

if(cnt16=“1111”)then

tate 《= t2; —-开端位完,进入数据位

end if;

when t2=》 —-进入第1 位数据位

if(cnt16=“1111”)then

cnt16 《= “0000”;

else cnt16 《= cnt16+1;

end if;

if(cnt16=“0011”)then

sdata 《= rxd; —-采样第1 位数据位

end if;

if(cnt16=“0111”)then

if(sdata=’0‘)then

data(0)《=’0‘;

else data(0)《=’1‘; —-判别采样值,假如为0,则发送字符为0,

反之亦然

end if;

end if;

if(cnt16=“1111”)then

tate 《= t3; —-第1 位数据位完,进入下一状况

end if;

when t3=》 —-进入第2 位,第3 位和第4 位数据状况

if(cnt16=“1111”)then

cnt48 《= “000000”;

else cnt48 《= cnt48+1; —-不对剩余的数据采样,直接计数

end if;

if(cnt48=“101111”)then

sdata 《=’0‘; —-采样位清零

tate 《= t1; —-进入收集下一字符的预备状况

state 《= st2; —-第1 个字符收集完,进入下一字符

end if;

end case;

fdata(0) 《= data(0); —-收集完的字符存入缓存区

…… …… ……

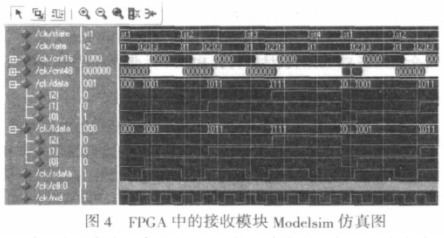

对每个字符的收集进程是相同的。笔者依据实际需求只让计算机发送 3个二进制字符,由此能操控 FPGA的 8种输出状况。在整个 VHDL源程序编写完之后,用 Modelsim 6.0进行仿真,如图 4。

鉴于发送字符与其异步传输帧格局的特殊关系,此仿真中的 rxd用周期为 16×clk0的波形替代,因而就会接纳到字符串‘ 111’。串口调试帮手需求每隔一段时间(大于 1ms)发送一组字符串,则等候状况 st4是有必要的,它也是接纳下一字符的预备状况。缓存区为 3位空数组 fdata,它在接纳下一字符之前有必要清零。

5 结语

虽然现在串行通讯速度慢的特色现已越来越显着,可是由于其传输线少且成本低,大都电子产品开发中都会持续运用串行通讯。本文所介绍的串行接纳模块是笔者依据试验要求自行规划,并在试验中成功地完成了计算机对 FPGA的精确操控。因而,本文也可作为一个实例,供开发者沟通。

本文作者立异点:计算机串口按 ASCII码发送“0”和“1”组成的字符串,在 FPGA内部只需判别接纳到的数据流中的每个开端位之后的第一位数据位,就可昀终得出计算机发送的字符串。此种办法使 FPGA能够简洁、精确的辨认串口数据,且能够方便地修改为任何一种异步通讯帧格局。

责任编辑:gt